资料下载

×

DSP嵌入式显微图像处理系统设计方案

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-11-03

显微图像处理是数字图像处理的一个重要研究领域,随着其技术的不断发展,已经在材料、生物、医学等领域得到了广泛应用。目前的显微图像处理通常利用图像采集系统将显微图像采集到计算机中再进行图像处理,这样,虽然运算速度高,但体积庞大、不便于携带,有一定的局限性。因此,采用数字图像处理技术和DSP技术实现颗粒显微图像的高效、快速、全面的统计与测量,具有重要的实用价值和广阔的应用前景。

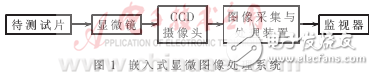

本文提出并设计了一种基于DSP和FPGA的嵌入式显微图像采集处理系统,如图1所示。其中,图像采集与处理装置是整个系统的关键部件,它以DSP和FPGA为核心,DSP作为中央处理器负责图像滤波、阈值分割及目标的数目、直径及面积等统计处理,通过FPGA完成各种接口逻辑和时序匹配,并配以大容量存储器用于图像的存储。DSP芯片体积小,运算速度快,使用灵活方便;FPGA具有在系统可编程和控制逻辑实现灵活的特点。因此,既能够满足处理的快速性,又能满足小型化便于携带的要求。

1 系统硬件平台设计

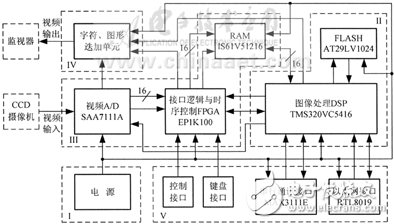

基于视频图像处理的显微图像处理系统的性能,在很大程度上依赖于其硬件处理单元的结构和性能。本系统所采用的硬件结构主要由5大模块组成:DSP核心处理单元、视频图像采集与存储模块、字符与图形迭加单元、通讯与用户交互接口模块、电源模块。系统电路框图如图2所示。

图2 嵌入式显微图像处理系统硬件结构框图

系统的工作过程为:系统上电后,DSP执行BOOTLOAD程序,将用户程序代码从外部Flash load到内部程序存储器,并执行A/D、字符迭加等初始化操作。视频采集与转换模块将CCD摄像机输出的模拟视频信号转换为数字图像数据并存储在RAM中,在一场图像采集完毕后,由场同步信号通过FPGA以中断方式通知DSP,DSP从RAM中读取图像,并负责完成图像滤波、分割、测量等各种处理算法,将测量结果通过字符图形迭加单元显示在监视器屏幕上,也可以根据需要由通讯接口模块传送给主机。各种接口逻辑与时序控制通过在FPGA器件内部编程实现。

模拟视频信号分为两路:一路经A/D转换为数字图像信号,另一路则与视频叠加芯片MAX442和字符叠加芯片μD6453进行图形和字符的叠加显示。这里采用Philips公司的SAA7111A作为视频A/D解码芯片,它将CCD摄像机输出的模拟视频信号转换为数字图像数据,并在FPGA的控制下存储在RAM中,同时产生行同步信号HS、场同步信号VS、奇偶场标志信号RTS0以及像素时钟信号LLC2。MAX442是一个双通道视频信号放大器,增益带宽高达140MHz。μPD6453为NEC公司生产的用于视频设备中的字符发生芯片。待显示的字符和图形与CCD摄像机输出的原始图像一起叠加显示在监视器屏幕上。

在图像采集过程中,视频解码芯片SAA7111A按像素逐点输出4:2:2的YUV格式的数字图像数据。该格式中,每帧图像的分辨率为720×576,即每行有720个像素点,每帧576行,由于一帧图像是由奇、偶两场图像组成的,因此每场图像有288行。为了处理方便,每场采集的图像大小为512×256,即每行采集512个像素,每场(奇场或偶场)采集256行,通过在FPGA中编程实现像素延时和行延时,选择每行中间的512个像素和每场中间的256行。

本文提出并设计了一种基于DSP和FPGA的嵌入式显微图像采集处理系统,如图1所示。其中,图像采集与处理装置是整个系统的关键部件,它以DSP和FPGA为核心,DSP作为中央处理器负责图像滤波、阈值分割及目标的数目、直径及面积等统计处理,通过FPGA完成各种接口逻辑和时序匹配,并配以大容量存储器用于图像的存储。DSP芯片体积小,运算速度快,使用灵活方便;FPGA具有在系统可编程和控制逻辑实现灵活的特点。因此,既能够满足处理的快速性,又能满足小型化便于携带的要求。

1 系统硬件平台设计

基于视频图像处理的显微图像处理系统的性能,在很大程度上依赖于其硬件处理单元的结构和性能。本系统所采用的硬件结构主要由5大模块组成:DSP核心处理单元、视频图像采集与存储模块、字符与图形迭加单元、通讯与用户交互接口模块、电源模块。系统电路框图如图2所示。

图2 嵌入式显微图像处理系统硬件结构框图

系统的工作过程为:系统上电后,DSP执行BOOTLOAD程序,将用户程序代码从外部Flash load到内部程序存储器,并执行A/D、字符迭加等初始化操作。视频采集与转换模块将CCD摄像机输出的模拟视频信号转换为数字图像数据并存储在RAM中,在一场图像采集完毕后,由场同步信号通过FPGA以中断方式通知DSP,DSP从RAM中读取图像,并负责完成图像滤波、分割、测量等各种处理算法,将测量结果通过字符图形迭加单元显示在监视器屏幕上,也可以根据需要由通讯接口模块传送给主机。各种接口逻辑与时序控制通过在FPGA器件内部编程实现。

模拟视频信号分为两路:一路经A/D转换为数字图像信号,另一路则与视频叠加芯片MAX442和字符叠加芯片μD6453进行图形和字符的叠加显示。这里采用Philips公司的SAA7111A作为视频A/D解码芯片,它将CCD摄像机输出的模拟视频信号转换为数字图像数据,并在FPGA的控制下存储在RAM中,同时产生行同步信号HS、场同步信号VS、奇偶场标志信号RTS0以及像素时钟信号LLC2。MAX442是一个双通道视频信号放大器,增益带宽高达140MHz。μPD6453为NEC公司生产的用于视频设备中的字符发生芯片。待显示的字符和图形与CCD摄像机输出的原始图像一起叠加显示在监视器屏幕上。

在图像采集过程中,视频解码芯片SAA7111A按像素逐点输出4:2:2的YUV格式的数字图像数据。该格式中,每帧图像的分辨率为720×576,即每行有720个像素点,每帧576行,由于一帧图像是由奇、偶两场图像组成的,因此每场图像有288行。为了处理方便,每场采集的图像大小为512×256,即每行采集512个像素,每场(奇场或偶场)采集256行,通过在FPGA中编程实现像素延时和行延时,选择每行中间的512个像素和每场中间的256行。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章