24c04的使用说明

电子常识

描述

24c04的使用说明

1.引脚(见: 硬件接法)

读写命令

1 0 1 0 A2 A1 A0 R\w “1001”是AT24cxx 类型识别符(着种芯片的地址)

A2 A1 A0 挂在总线上不同芯片的地址(片选)W/R 0写;1 读2.

引脚说明:

A0~A2: 芯片的地址

SCL:时钟信号线用于产生器件所有数据发送或接收的时钟 在写方式,SCL为高电平时, 数据必须保持稳定。且下降沿送数。

SDA:数据信号线用于传送地址和所有数据的发送和接受仅仅在SCL为低时数据才可以改变;

WP:写保护接+5V时只能读;接GND时即能写也能读;

3.时序

开始信号SCL为高电平时,SDA由高变底

停止信号SCL为高电平时,SDA由低变高

应答信号接收数据的IC在接到第8BIT后(“写”),发出特定的低电平脉冲,表示受到数据

操作步骤:

(1)”写” 启动总线(I方C)—发送器件寻址字节—应答—发送数据寻址地址—回答—发送第一个数据—应答--…………。发送第N个数据—应答—停止总线; 写地址可以指定第一个数据地址后连续送数。 “写”分为字节写和页写两种方式。

(2)”读”所有的操作几乎一样。只是在读完8位数据以后,。从设备不是发出ACK(低电平),而是直接给SETB SDA ,然后发出停止总线信号即可结束本次读。 读也分为当前地址读随机读和顺序读。

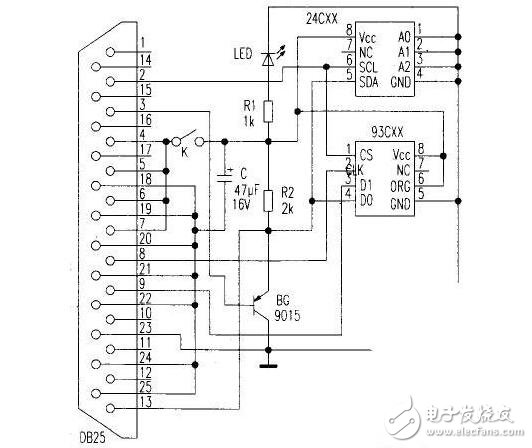

硬件接法

P1.0 接scl(6脚);

p1.1接sda(5脚);

4脚为GND; 8脚为VCC;

剩下的A2(3脚)A1(2脚) A0(1脚),T通过接VCC或GND以确定硬件的地址。 功能:显示60H~63H中的数显示24c04(60h~63h)读到单片机60h~63h中显示。

代码

VSDA BIT P1.0

VSCL BIT P1.1

org 0000h

mov 60h,#00h

mov 61h,#00h

mov 62h,#00h

mov 63h,#00h

start: LCALL DISPLAY

LCALL DLE1

mov 60h,#01h

mov 61h,#02h

mov 62h,#03h

mov 63h,#04h

lcall write

lcall de

lcall read

lcall display

;############# 问题

asd: ajmp asd

;#############

ajmp start

STA: SETB VSDA

SETB VSCL

NOP

nop

nop

nop

CLR VSDA

NOP

clr vsda

nop

nop

nop

nop

CLR VSCL

RET

STOP: clr vsda

setb vscl

nop

nop

setb vsda

RET

WRBYT: MOV 17h,#08H;上升沿

WLP: RLC A

JC WR1

AJMP WR0

WLP1: DJNZ 17h,WLP

NOP

NOP

SETB VSCL

NN: MOV C,VSDA

JC NN

CLR VSCL

;call de

RET

WR1: setb vsda

setb vscl

NOP

NOP

nop

nop

clr VSCL

clr vsda

AJMP WLP1

WR0: CLR vsda

setb vscl

NOP

NOP

nop

nop

clr vscl

AJMP WLP1

rdbyt : mov 10h,#08h

rlp: setb vsda

setb vscl

mov c,vsda

rlc a

clr vscl

djnz 10h,rlp

nop

setb vsda

nop

nop

setb vscl

ret

WRITE: mov 15h,#4

mov 16h,#50h

mov r0,#60h

lcall sta

mov a,#0a0h

lcall wrbyt

mov a,16h

lcall wrbyt

wda: mov a,@r0

lcall wrbyt

;lcall de

inc r0

djnz 15h,wda

lcall stop

ret

read: mov 15h,#4

mov 16h,#50h

mov r0,#60h

ok: lcall sta

mov a,#0a0h

lcall wrbyt

mov a,16h

lcall wrbyt

lcall sta

mov a,#0a1h

lcall wrbyt

nop

lcall rdbyt

lcall stop

mov @r0,a

inc r0

inc 16h

djnz 15h,ok

ret mack: clr vsda

setb vscl

nop

nop

clr vscl

setb vsda

ret

mnack: setb vsda

setb vscl

nop

nop

clr vsda

clr vscl

ret

display:mov dptr,#tab1

mov a,60h;4

movc a,@a+dptr

mov 13h,a

mov dptr,#tab1

mov a,61h;3

movc a,@a+dptr

mov 12h,a

mov dptr,#tab1

mov a,62h;2

movc a,@a+dptr

mov 11h,a

mov dptr,#tab1

mov a,63h;高

movc a,@a+dptr

mov 10h,a

ACALL DISP RET

disp: clr p1.5

clr p1.4

MOV 16H,#4

mov r1,#13h

dir1x:acall shift;senddata

dec r1

djnz 16H,dir1x

setb p1.5;first finish

nop

NOP

clr p1.5

RET

shift: mov a,@r1;

mov 15H,#08h acall yw

RET

yw: RRC A

MOV P1.3,C

SETB P1.4

NOP

NOP

NOP

CLR P1.4

DJNZ 15H,yw

MOV 15H,#08H

RET

tab1: db 0fch,60h,0dah,0f2h,66h,0b6h,0beh,0e0h,0feh,0f6h

DE: MOV 40H,#08H

DE3: MOV 41H,#0a0H

DE2: MOV 42H,#01H

DE1: DJNZ 42H,DE1

DJNZ 41H,DE2

dJNZ 40H,DE3

RET

DLE1: MOV 40H,#08H

DE31: MOV 41H,#0FFH

DE21: MOV 42H,#0FFH

DE11: DJNZ 42H,DE11

DJNZ 41H,DE21

dJNZ 40H,DE31

RET

END

- 相关推荐

- 热点推荐

- 24c04

-

12864与24C04的原理和使用方法是什么2022-02-07 1155

-

使用24C04和1602LCD设计电子密码锁的详细资料说明2019-12-31 1586

-

24c04读写程序详解2017-11-03 18308

-

基于8051的Proteus仿真-24C04与1602LCD设计2016-09-06 883

-

24C04读取问题2014-05-05 4832

-

TCL 2969 24c04存储器数据2009-06-10 539

-

TCL 2101(24C04)存储器数据2009-06-04 406

-

康佳2109C(24C04)EPROM数据2009-05-27 466

-

24C04/25C04 pdf datasheet2008-10-07 990

全部0条评论

快来发表一下你的评论吧 !