74ls148工作原理

电子常识

描述

有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的于是就出现了74ls148优先编码器,先说一下他的基本原理。他允许同时输入两个以上编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

74LS148 是8 线-3 线优先编码器,共有 54/74148 和 54/74LS148 两种线路结构型式,将 8 条数据线(0-7)进行 3 线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

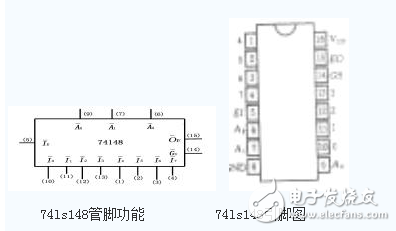

74ls148芯片管脚

0-7 编码输入端(低电平有效)EI 选通输入端(低电平有效)A0、A1、A2 三位二进制编码输出信号即编码 输 出 端(低电平有效)GS 片优先编码输出端即宽展端(低电平有效)EO 选通输出端,即使能输出端

74ls148管脚功能 74ls148引脚图

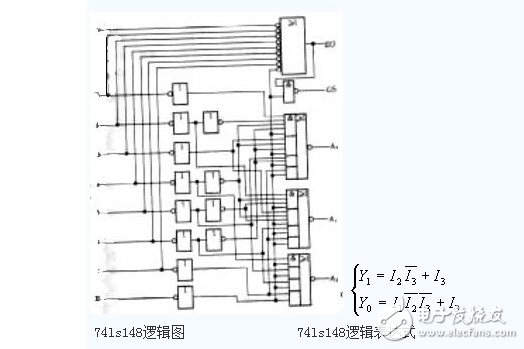

74ls148逻辑图 74ls148逻辑表达式

74ls148工作原理

使能端OE(芯片是否启用)的逻辑方程:

OE =I0·I1·I2·I3·I4·I5·67·IE

当OE输入IE=1时,禁止编码、输出(反码): A2,A1,A0为全1。

当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。

由74ls148真值表可列输出逻辑方程为:

A2 = (I4+I5+I6+I7)IE

A1 = (I2I4I5+I3I4I5+I6+7)·IE

A0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE

-

基于AT89C51单片机74LS148扩展中断Proteus仿真2023-05-04 898

-

设计分享|74LS148实现按键控制LED灯2023-01-04 5042

-

74ls148一定要拉高嘛?(新手喷轻点)2022-01-28 4534

-

74LS148扩展中断的程序和工程文件免费下载2020-05-27 1552

-

74LS148扩展中断的仿真电路图免费下载2020-03-20 2947

-

请问利用多片74ls148八-三编码器怎么完成88路数据输入的编码2019-03-11 5437

-

74ls147和74ls148有什么区别2018-05-07 36434

-

74ls148可以用什么代替2018-02-01 9336

-

74ls148做八路抢答器2017-11-07 54452

-

基于8051的Proteus仿真-74LS148扩展中断2016-09-06 950

-

proteus中74LS148的问题2013-01-24 9888

-

protens仿真74ls148零管脚触发问题2012-05-05 4477

-

74LS148扩展中断(基于8051+Proteus仿真)2010-07-06 1635

-

74ls148中文资料pdf下载2008-03-06 2312

全部0条评论

快来发表一下你的评论吧 !