uc3907引脚图及功能

集成电路

描述

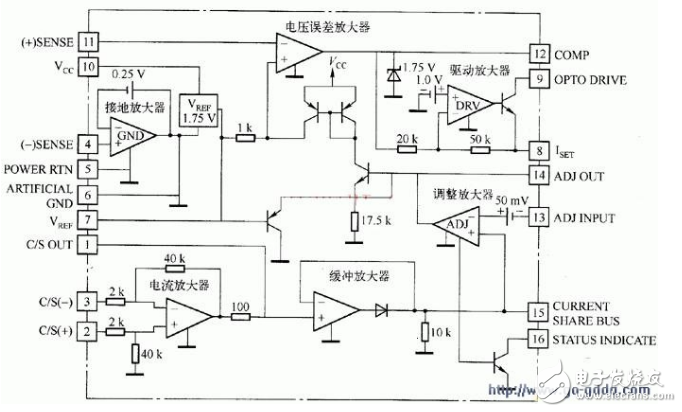

UC3907集成电路芯片的内部结构原理,工作电源V∝(10脚)的电压范围为4.5~35V;芯片内有一个基准电压源VREF,其值相对于ARTIFICIALGND(6脚)为1.15V,也可以从VREF(7脚)输出;ARTIFICIALGND是芯片的低阻地(参考地),它比(—)SENSE(4脚)的电位高0.25V,这一电压偏置为接地放大器的工作电流提供回路,而使电压采样负端(—)SENSE(即接地放大器的反相输人端)为高输入阻抗。

工作原理:电流采相信号由C/S(+)(2脚)和C/S(—)(3脚)差动输人到电流放大器,电流放大器是一个增益固定为20的低通差分放大器,允许共模输人电压范围为:最低值为功率返回线POWERRTN(5脚)电位,最高值为Ugp-2V,允许差模输人电压范围为50~500mV。电流放大器的输出,一方面经过缓冲放大器连接到均流母线CURRENTSHAREBUS(15脚);另一方面与均流信号一起,经过调整放大器生成环流信号,还可以通过STATUSINDICATE(16脚),输出主模块状态指示信号。

缓冲放大器输出到均流母线(15脚),各个并联电源模块与均流母线相连,以实现均流。均流母线对地短路或电位高于50 V时,保护电路动作,因此均流母线开路或短路,都不会影响各电源模块的独立工作。

输出电压采样信号由(+)SENSE(11脚)和(—)SENSE(4脚)差动输入到电压误差放大器,以实现电压放大和系统频率特性校正,电压环补偿网络跨接在电压放大器的反相输人端(11脚)和输出端COMP(12脚)。

驱动放大器是一个反相缓冲器,接在电压放大器之后,它的增益固定为2.5倍,通常驱动外接光耦将电压误差信号耦合到电源模块的PWM控制器,具体来说,UC3907的OPTODRIVE(9脚)接外部光耦的发光二极管负端(其正端接UCC),如图11- l6所示。吸人电流由接在ISET(8脚)与地之间的电流设定电阻决定,该电流最大允许值为20 mA。这时的调节极性是:光耦电流随着模块输出电压的上升而增大。在非隔离应用场合,可以直接利用8脚输出的电压信号(0.25~4.1 V),相应地调节极性是:8脚电位随着模块的输出电压上升而变高。

UC3907的5脚,一般接分流器的负端,该点的电位是最低的,它允许比(—)SENSE脚低0~5 V。

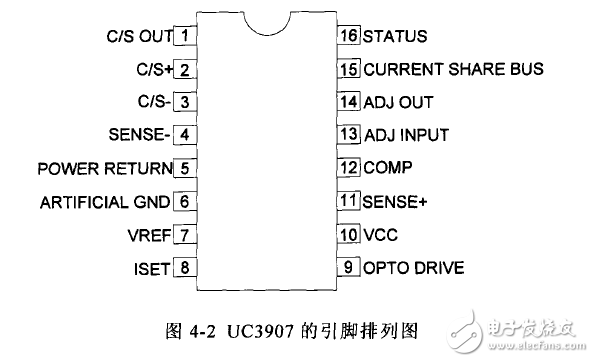

UC3907采用双列直插16脚封装,引脚赔礼如图所示,各引脚功能如表格所示:

-

关于UCC3895与UC3907一起使用问题2020-02-14 2224

-

UC3907 负载均分控制器2018-11-02 800

-

uc3842与uc3907配合使用2018-08-29 2300

-

uc3846工作原理(uc3846引脚功能_内部结构及应用电路图)2018-01-25 147385

-

UC3907实现民主均流控制电路2011-10-28 3249

-

利用UC3907设计的均流电路2009-07-09 7604

-

at89c52引脚图及管脚功能2008-06-17 86456

-

62256引脚图2008-04-01 25016

-

8031引脚功能图2008-03-06 4808

-

tda4661引脚功能图与引脚电压2008-01-16 1651

-

8259引脚图引脚功能2008-01-11 9164

-

uc3842引脚图 uc3842引脚功能2007-12-22 36958

-

74ls04引脚图 引脚功能2007-11-29 76369

-

ne555引脚图及功能2007-11-18 279735

全部0条评论

快来发表一下你的评论吧 !