od门电路线于原理漏极开路输出

电子常识

2685人已加入

描述

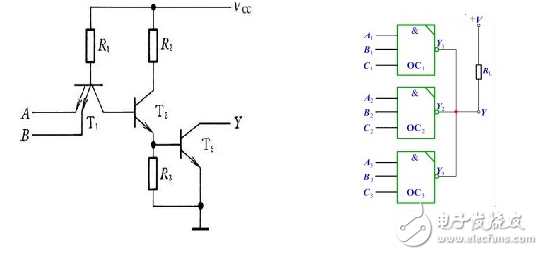

OD门(漏极开路的门电路)如同TTLOC门,CMOSOD门,可用来“线与”。

漏极开路门电路线于原理是什么

线与”逻辑是因为多个逻辑门的输出三极管(场效应管、二极管),共用一个上拉电阻,只要一个逻辑门输出低电平,即集电极(漏极)开路输出的管子导通,就把上拉电阻接地,输出低电平;只有全部输出管截止,输出端被上拉电阻置为高电平,这就是与逻辑的运算结果。

漏极开路输出

和集电极开路一样,顾名思义,开漏电路就是指从MOSFET的漏极输出的电路。典型的用法是在漏极外部的电路添加上拉电阻到电源如图所示。完整的开漏电路应由开漏器件和开漏上拉电阻组成。这里的上拉电阻R的阻值决定了逻辑电平转换的上升/下降沿的速度。阻值越大,速度越低,功耗越小。因此在选择上拉电阻时要兼顾功耗和速度。标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

很多单片机等器件的I/O就是漏极开路形式,或者可以配置成漏极开路输出形式,如51单片机的P0口就为漏极开路输出。在实际应用中可以将多个开漏输出的引脚连接到一条线上,这样就形成“线与逻辑”关系。注意这个公共点必须接一个上拉电阻。当这些引脚的任一路变为逻辑0后,开漏线上的逻辑就为0了。在I2C等接口总线中就用此法判断总线占用状态。

同集电极开路一样,利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经上拉电阻,再经MOSFET到GND。IC内部仅需很下的栅极驱动电流,因此漏极开路也常用于驱动电路中。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

OC门电路和OD门电路设计原理2022-12-25 9431

-

TTL门电路输入端简析2022-01-25 12575

-

集电极开路、漏极开路、上拉电阻、下拉电阻等接口相关基本概念2022-01-14 1415

-

什么是集电极开路(OC)?什么是漏极开路(OD)?资料下载2021-04-13 2033

-

什么是集电极开路/漏极开路?2021-03-10 3585

-

MOS管构成的缓冲器Buffer和漏极开路门OD门的详细概述2018-04-29 52695

-

集电极开路输出和漏极开路输出2017-11-09 37665

-

什么是漏极开路(OD)?2010-03-04 54392

-

OD门(漏极开路的门电路)2010-02-28 17737

-

开路漏极电路图2009-08-15 1192

全部0条评论

快来发表一下你的评论吧 !