sdr技术原理解析

无线通信电子电路图

描述

软件无线电(SDR)概念

软件无线电,即Software Defined Radio,SDR。通俗来讲,SDR就是基于通用的硬件平台上用软件来实现各种通信模块。

概念中有两个关键词,“通用硬件平台”和“软件”。“通用硬件平台”就是说我们能基于这个硬件平台实现各种各样的通信功能,而不是说一个硬件平台只能实现一种通信功能。“软件”来实现通信模块是相对于传统的无线电技术来讲的,传统的无线电通信模块都是用硬件电路来设计,一个通信电路只能完成一种通信功能,开发周期长,开发成本高,而且一旦设计好后功能就无法改变。软件化可以加快通信模块的开发速度,降低开发成本,便于调试和维护。

我们可以用图1来简单看看软件无线电基站与传统的无线电基站的区别。图片左边的是传统的大基站,图片右边的是基于软件无线电的小型化基站。传统的商用基站体积较大,需要设计很多专用的硬件电路;而SDR基站体积较小,大部分通信功能由软件实现。

图1 商用基站与SDR基站

SDR技术被誉为通信领域的第三次革命。第一次革命是1G通信系统,由有线通信到无线通信的革命;第二次革命是2G通信系统,由模拟通信到数字通信的革命。SDR是未来通信系统的发展趋势。

SDR系统原理

下面正式开始讲解SDR的系统原理。在上面的介绍中我们知道GPP-Based SDR系统一般都是包含一个GPP和一个外设。我们以一台笔记本电脑连接一个USRP B200为例来给大家讲解SDR系统内部的实现原理。

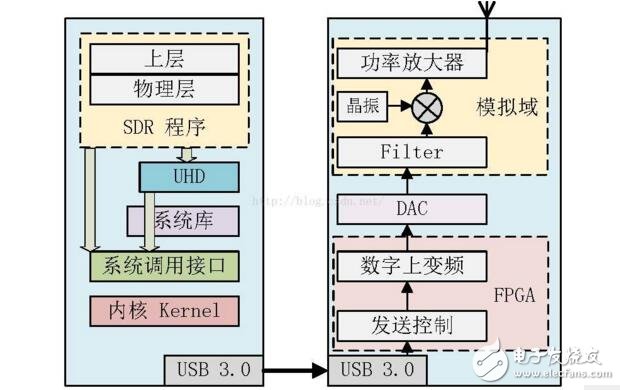

.1 发射机

首先我们来看发射端的系统原理图,即图7。图的左边是一台笔记本的示意图,右边的一个USRP B200的发射示意图。

首先看笔记本结构最上面的SDR程序。这个程序就是我们用软件来实现的通信模块,在笔记本上我们可以用各种高级编程语言来编写各种通信模块,例如Turbo编码模块,OFDM模块等。鉴于SDR系统对实时性要求较高,所以我们一般使用C或C++语言来编写SDR程序。SDR程序里面包含了通信系统完整的协议栈,如果我们写的是LTE系统,则包含PHY、MAC、RLC、PDCP、RRC、NAS甚至MME等;而如果我们的是WiFi系统,则包含PHY、MAC、LLC等。SDR程序的主要功能是处理系统的基带数据。

接下来UHD是USRP设备的驱动模块,不同的外设使用的驱动也不一样,因为我们是以USRPB200为例,所以驱动模块是UHD。UHD驱动的安装方式可以参见使用C或者C++调用UHD的库函数。

接下来是系统的各种系统库和系统调用的接口以及内核。强调一点,大部分SDR程序都是基于Linux来开发的,很少基于Windows开发。因为Linux系统开源,而且实时性较好。这一块主要涉及操作系统方面的知识,我们不在这里深入讨论。

USRP B200与GPP的接口是USB3.0。外设接口的选择也很重要,接口的传输速率必须快,不能成为整个系统的瓶颈。USRP早期的产品的都是用的USB2.0接口,因为当时通信系统的吞吐量较小,所以不会限制使用。现在大部分外设都是用USB3.0或者以太网网口作为外设接口。USB3.0的接口速度可以达到500MBps,基本能满足大部分通信系统的需求。

接着笔记本电脑通过USB3.0把数据传输给USRP B200。USRP最底下的两个模块是发送控制模块和数字上变频模块(DUC)。这两个模块是用FPGA里面实现的,用FPGA实现的好处是处理速度快。发送控制模块好理解就是用来控制整个USRP的发送行为,例如什么时候发送等。DUC模块是为了把电脑产生的基带数据上变频到中频。之后数字信号经过USRP的DAC之后转化为模拟域的数据,数模转化之后需要过一个低通滤波器使信号变的更加平滑。最后中频的模拟域数据在于晶振产生的信号相乘把我们的中频信号调制到制定的射频频点上。

最后射频信号再经过功率放大器把信号发射出去。信号放大器里面也有很多知识可以学习。例如信号放大器分为A类,B类和C类等,具体每一类的特征本文就不具体解释了。我们可以通过UHD提供的库函数来修改发射信号的发射增益,即tx_gain。tx_gain这个参数对信号的影响还是挺大的,tx_gain设置的太小导致信号功率太小,而如果设置的过大可能会导致系统的低噪上升,也有可能会影响其他通信系统的正常工作。

图2 SDR发射机原理图

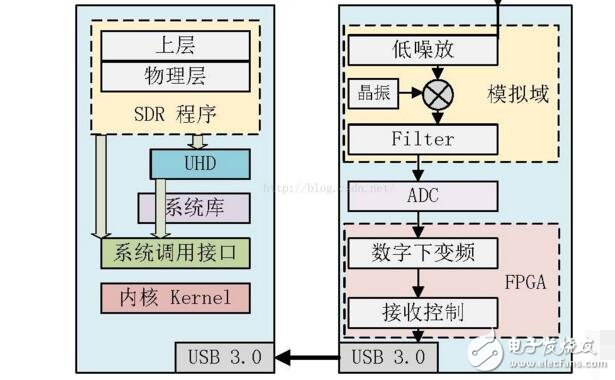

2 接收机

可能有人会问为什么要经过两次变频。我们以SDR接收机给大家讲解。如图8所示是SDR接收机的原理图。同样的,左边是笔记本的示意图,与发射机的一样;右边是USRP的接收示意图,USRP接收示意图与发射示意图稍有不同。

首先接收部分的放大器变成了低噪放,顾名思义,低噪放就是低噪声的放大器,本质上还是个放大器。因为接收的信号里面包含了信道的噪声,接收机不能把噪声放的过大。

信号经过低噪放后与USRP晶振产生的信号相乘把信号下变频到中频,同样地再经过一个低通滤波器把信号变得平滑。

之后中频信号经过ADC把模拟域的信号转到数据域。ADC是USRP里面很重要的一个部件。ADC主要由两个参数,采样精度和采样率。采样精度表示采样后的信号用多少bit来表示,例如USRP B200的ADC精度为12 bits,即采样后的每一个数据用12bits来表示。采样率就是系统的采样速率,USRP B200的采样速率为61.44MS/s。这也就是为什么大部分SDRLTE系统都采用USRP B系列作为外设的原因,61.44MS/s的采样率刚好是LTE系统最大采样速率30.72M的两倍。

同样地信号经过ADC之后,数字信号被送入FPGA模块处理。FPGA里面包含两个模块,数字下变频和接收控制。接收控制用来控制整个USRP系统的接收流程,例如什么时候开始接受等。数字下变频即DDC,用于把信号从中频下变频到基带。

图3 SDR接收机原理图

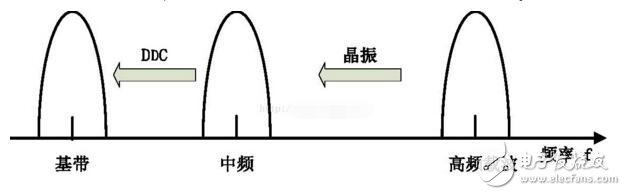

为什么要经过两次下变频呢?如图9所示,第一次变频是在模拟域通过晶振产生的信号与射频信号相乘把信号下变频到中频,这一次变频主要是为了后面做AD采样。我们知道采样需要满足奈奎斯特采样定律,采样的频率必须大于信号的最高频率的2倍,而射频信号的载波频率已经能都达到2.6GHz,甚至5GHz,根本无法做出载波频率两倍的采样速率的ADC。所以系统先把信号下变频到中频,然后再利用ADC对信号进行模数转化。因为USRP ADC的采样率为61.44MS/s,所以我们可以推出USRP对应的中频频率应该低于30.72MHz。

接着中频的数字信号被DDC下变频到基带。有人可能会问为什么不直接把信号一次变频到基带呢,这样的接收机叫做零中频接收机。如果载波频率高了,零中频的接收机设计会非常复杂,所以零中频接收机一般用于载波频率较低的系统里面。

图4 下变频原理示意图

数字信号经过USB3.0接口传输到笔记本电脑上后,电脑再把数据传输给SDR程序处理。物理层处理完后再把数据交给上层。这样SDR接收机的信号接收过程便完成了。

SDR发射机/接收机里面的每一个模块都对应一大片知识,知识的海洋是无穷的,这里的介绍只能起一个抛砖引玉的作用。如果大家想深入学习的话,还得要多查阅资料。

-

SDR_SDR是什么意思2011-12-07 12601

-

IN612 SDR API介绍橙群微电子 2023-03-03

-

手机通信原理解析2011-12-14 140032

-

介绍SDR的技术原理 以SDR LTE系统为例进一步解析SDR系统的工作流程2019-05-11 4553

-

ADC技术在SDR实现中有哪些挑战?2019-08-02 1731

-

定位技术原理解析2020-05-04 2265

-

工业互联网中的标识解析技术2023-09-19 977

-

电动汽车动力转向技术原理解析2010-03-17 2284

-

量子密码技术,量子密码技术原理解析2010-03-20 4468

-

虚拟存储器部件原理解析2010-04-15 3556

-

触摸屏的应用与工作原理解析2017-02-08 1426

-

sdr技术功能的特点2017-11-10 5263

-

SDR的技术原理介绍及案例分析2017-11-21 40054

-

软件无线电(SDR)的概念、分类及其工作原理2020-07-16 2018

-

电磁屏蔽技术的原理解析2024-03-06 5983

全部0条评论

快来发表一下你的评论吧 !