去耦电容的作用和原理

电容器

描述

去藕电容就是起到一个电池的作用,满足驱动电路电流的变化,避免相互间的耦合干扰。

电容退耦原理

采用电容退耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降 低电源分配系统的阻抗都非常有效。

对于电容退耦,很多资料中都有涉及,但是阐述的角度不同。有些是从局部电荷存储(即 储能)的角度来说明,有些是从电源分配系统的阻抗的角度来说明,还有些资料的说明更 为混乱,一会提储能,一会提阻抗,因此很多人在看资料的时候感到有些迷惑。其实,这两种提法,本质上是相同的,只不过看待问题的视角不同而已。

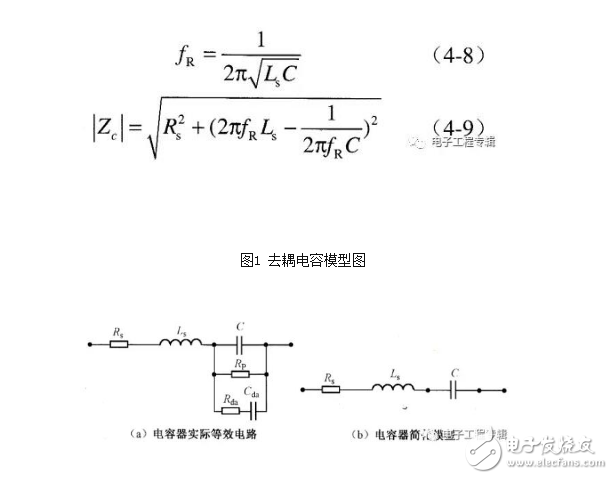

去耦电容在集成电路电源和地之间的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容值是0.1μF。这个电容的分布电感的典型值是5μH。0.1μF的去耦电容有5μH的分布电感,它的并行共振频率大约在7MHz左右,也就是说,对于10MHz以下的噪声有较好的去耦效果,对40MHz以上的噪声几乎不起作用。1μF、10μF的电容,并行共振频率在20MHz以上,去除高频噪声的效果要好一些。每10片左右集成电路要加一片充放电电容,或1个蓄能电容,可选10μF左右。最好不用电解电容,电解电容是两层薄膜卷起来的,这种卷起来的结构在高频时表现为电感。要使用钽电容或聚碳酸酯电容。去耦电容的选用并不严格,可按C=1/F,即10MHz取0.1μF,100MHz取0.01μF。

退耦原理: (去耦即退耦)

高手和前辈们总是告诉我们这样的经验法则:“在电路板的电源接入端放置一个1~10μF的电容,滤除低频噪声;在电路板上每个器件的电源与地线之间放置一个0.01~0.1μF的电容,滤除高频噪声。”在书店里能够得到的大多数的高速PCB设计、高速数字电路设计的经典教程中也不厌其烦的引用该首选法则(老外俗称Rule of Thumb)。

在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去耦电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法。去耦电容主要是去除高频如RF信号的干扰,干扰的进入方式是通过电磁辐射。

而实际上,芯片附近的电容还有蓄能的作用,这是第二位的。你可以把总电源看作密云水库,我们大楼内的家家户户都需要供水,这时候,水不是直接来自于水库,那样距离太远了,等水过来,我们已经渴的不行了。

实际水是来自于大楼顶上的水塔,水塔其实是一个buffer的作用。如果微观来看,高频器件在工作的时候,其电流是不连续的,而且频率很高,而器件VCC到总电源有一段距离,即便距离不长,在频率很高的情况下,阻抗Z=i*wL R,线路的电感影响也会非常大,会导致器件在需要电流的时候,不能被及时供给。而去耦电容可以弥补此不足。这也是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一(在vcc引脚上通常并联一个去藕电容,这样交流分量就从这个电容接地。)

配置原则如下:

电源输入端跨接一个10~100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会好。

为每个集成电路芯片配置一个0.01uF的陶瓷电容器。如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

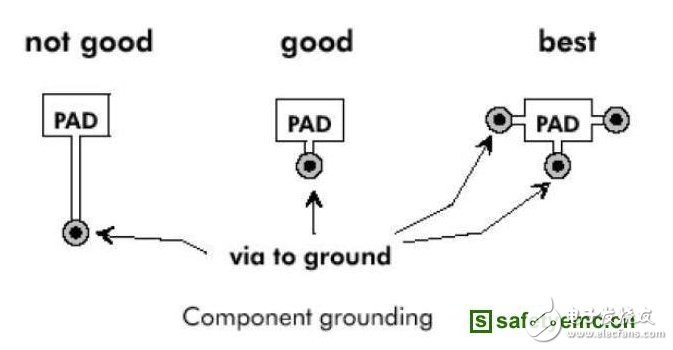

去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

-

旁路电容和去耦电容作用和区别介绍2024-03-01 4749

-

耦合和去耦有什么区别,耦合电容和去耦电容的作用分别是什么?2024-02-04 7391

-

去耦电容的作用及方法2023-08-07 2041

-

去耦电容的作用和选型2023-06-14 2940

-

去耦电容的作用是什么2023-02-02 1207

-

去耦电容的作用,为什么一个电容也会谐振?2022-08-02 1650

-

详解去耦电容的应用及作用2022-04-01 7220

-

去耦电容的作用及它在单片机中的应用资料下载2021-04-23 849

-

旁路电容和去耦电容的作用及选用2020-10-29 11586

-

去耦电容的作用2020-08-27 7248

-

耦合电容和去耦电容的作用分别是什么?2019-10-17 13676

-

详解去耦电容的作用2017-12-06 17090

-

旁路电容和去耦电容作用和区别2017-11-06 22134

全部0条评论

快来发表一下你的评论吧 !