LVDS静电放电防护方案

电子说

描述

LVDS静电放电防护方案

方案简介

LVDS是一种低压差分信号技术,该技术通过一对差分信号线(或平衡电缆)以极低的电压摆幅(约350mV)进行数据的传输,采用LVDS接口,可以使得信号在差分线或平衡电缆上以几百Mbps的速率传输,由于采用低压和低电流驱动方式,实现了低噪声、低串扰、低误码率和低功耗,LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用,常见于各电子设备的液晶显示屏中。

LVDS 接口拥有较高的数据传输速率,数据/图像传输率为 650Mbps 至 1.3Gbps。由于接口试图在保持高速的同时传输内容,因此选择线对线电容低的 ESD 保护器件对于确保信号完整性至关重要。普通的防护方案会对数据的传输造成一定影响。此方案高速差分信号部分采用集成低压四通道保护、超低容值、低漏电、低残压的ESD静电二极管防护器件,在不影响数据传输的前提下满足IEC61000-4-2 Level 4静电放电防护需求,让后端的电路得到有效防护。

LVDS工作原理

LVDS技术的基本工作原理是通过一个恒流源(通常约为3.5mA)驱动一对差分信号线。在接收端,由于接收器本身具有高直流输入阻抗(几乎不会消耗电流),因此几乎全部的驱动电流都流经100Ω的终端匹配电阻,并在接收器输入端产生约350mV的电压。当驱动状态反转时,流经电阻的电流方向改变,从而在接收端产生一个有效的“0”或“1”逻辑状态。

编辑

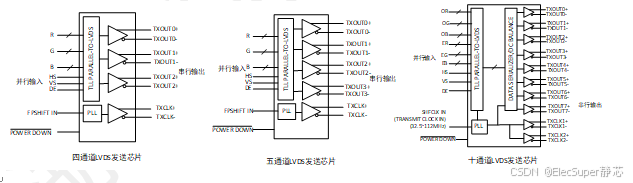

典型的LVDS发送芯片分为四通道、五通道和十通道几种,输入信号来自主控芯片,包含RGB数据信号、时钟信号和控制信号三大类。发送芯片将以并行方式输入的TTL电平RGB数据信号转换成串行信号后,直接送往液晶面板侧的接收芯片。LVDS发送芯片的输出是低摆幅差分对信号,一般包含一个通道的时钟信号和几个通道的串行数据信号。由于LVDS发送芯片是以差分信号的形式进行输出,因此,输出信号为两条线,分别输出正负信号。

应用示例

编辑

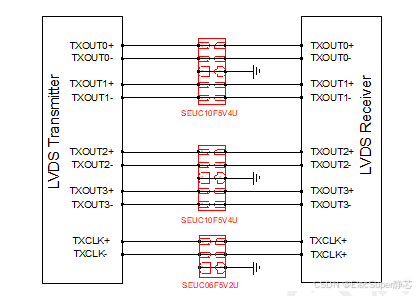

我们为LVDS接口提供了两种电气特性相似的ESD防护器件,专为保护差分线路而设计,其型号分别为SEUC10F5V4U和SEUC06F5V2U。器件的流通式封装设计简化了 PCB 布局,减少布线过程中的不连续性,促进了信号完整性和系统稳定性的提升。

SEUC10F5V4U为集成式十引脚ESD保护器件,结电容为0.6pF,钳位电压为12V,符合IEC 61000-4-2 (ESD) 规范,可在 ±17kV(空气)和 ±12kV(接触)下提供瞬变保护,可同时保护LVDS接口的两对数据传输高速信号差分线免受ESD静电放电干扰。

SEUC06F5V2U为集成式六引脚ESD保护器件,结电容为0.6pF,钳位电压为12V,符合IEC 61000-4-2 (ESD) 规范,可在 ±17kV(空气)和 ±12kV(接触)下提供瞬变保护,可保护LVDS接口的一对时钟信号差分线免受ESD静电放电干扰。

型号参数

| 规格型号 | 方向 | 工作电压(V) | IPP(A) | 钳位电压(V) | 结电容(pF) | Package |

| SEUC10F5V4U | Uni. | 5 | 4.5 | 12 | 0.6 | DFN2510-10L |

| SEUC06F5V2U | Uni. | 5 | 4.5 | 12 | 0.6 | DFN1610-6L |

电气特性表

At TA = 25℃ unless otherwise noted

| Parameters | Symbol | conditions | Min. | Typ. | Max. | Unit |

| Reverse stand-off voltage | VRWM | 5.0 | V | |||

| Reverse Breakdown Voltage | VBR | IT= 1mA | 6.0 | V | ||

| Reverse Leakage Current | IR | VRWM=5V | 1.0 | uA | ||

| Peak Pulse Current | IPP | TP=8/20us@25℃ | 4.5 | A | ||

| Clamping Voltage | VCL | IPP=1A; TP=8/20us | 9.0 | 11.0 | V | |

| Clamping Voltage | VCL | IPP=4.5A; TP=8/20us | 12.0 | 15.0 | V | |

| Junction capacitance | CJ |

I/O pins to ground; VR=0V; f = 1MHz |

0.6 | pF | ||

| Between I/O pins; | ||||||

| VR=0V; f = 1MHz | 0.3 |

表1 SEUC10F5V4U电气特性表

| Parameter | Symbol | Conditions | Min. | Typ. | Max. | Units |

| Reverse Stand-off Voltage | VRWM | 5 | V | |||

| Reverse Breakdown Voltage | VBR | IT=1mA | 6 | 9.5 | V | |

| Reverse Leakage Current | IR | VRWM=5V | 1.0 | uA | ||

| Clamping Voltage | VC | IPP=1A; tp=8/20us | 8.5 | 10.0 | V | |

| Clamping Voltage | VC | IPP=4.5A; tp=8/20us | 12.0 | 15.0 | V | |

| Junction Capacitance | CJ | I/O to GND; VR=0V; f=1MHz | 0.6 | 0.8 | pF | |

| Between I/O; VR=0V; f=1MHz | 0.3 | 0.4 | pF |

表2 SEUC06F5V2U电气特性表

总结与结论

LVDS接口不仅常用于消费电子类产品的显示器中,还广泛应用于汽车中的视频显示系统,所以保证其可靠性和稳定性极为关键。ELECSUPER SEMI研发各种低电容低钳位电压的ESD保护器件,可按照客户需求性能与封装提供定制化开发服务,为各种高速接口及通信线路提供值得信赖的保护器件。以上解决方案是保护LVDS接口的优选之策,确保设备能够高效、可靠地运行。

审核编辑 黄宇

-

时源芯微ESD防护ANT静电防护方案2025-05-09 1069

-

CAN静电放电防护方案2025-01-17 1695

-

Microphone静电放电防护方案2024-09-19 2094

-

分享几种不同的静电防护方案2024-03-26 3962

-

静电防护方案的保护电路介绍2022-10-19 4372

-

低压差分信号(LVDS) 接口静电防护,DW05-4R2P专用保护元件2020-12-29 2651

-

LVDS接口静电保护设计2020-10-30 2405

-

天线接口的静电防护解决方案2020-10-29 3498

-

LIN总线ESD静电防护方案设计图2020-09-24 2858

-

关于静电放电及防护的全面介绍2019-07-02 4490

-

静电放电及防护基础知识2017-11-23 2223

-

关于高清信号口的静电防护方案你了解吗?2017-11-15 4204

-

RGB接口静电放电防护方案2017-04-21 4696

-

避免闸极过度耦合效应的静电放电防护电路设计2011-11-30 1050

全部0条评论

快来发表一下你的评论吧 !