高速缓冲存储器在电脑硬件中的位置分析

缓冲/存储技术

描述

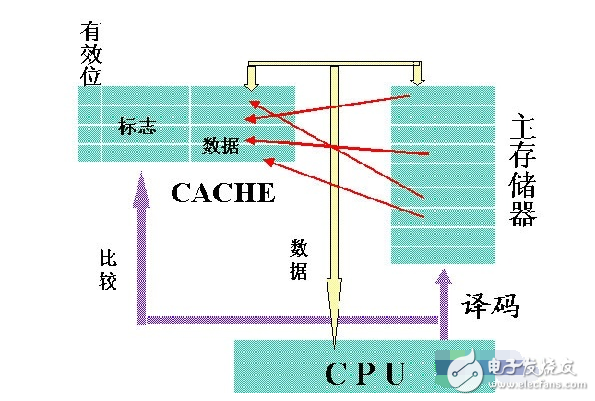

高速缓冲存储器通常由高速存储器、联想存储器、替换逻辑电路和相应的控制线路组成。在有高速缓冲存储器的计算机系统中,中央处理器存取主存储器的地址划分为行号、列号和组内地址三个字段。于是,主存储器就在逻辑上划分为若干行;每行划分为若干的存储单元组;每组包含几个或几十个字。高速存储器也相应地划分为行和列的存储单元组。二者的列数相同,组的大小也相同,但高速存储器的行数却比主存储器的行数少得多。

联想存储器用于地址联想,有与高速存储器相同行数和列数的存储单元。当主存储器某一列某一行存储单元组调入高速存储器同一列某一空着的存储单元组时,与联想存储器对应位置的存储单元就记录调入的存储单元组在主存储器中的行号。

当中央处理器存取主存储器时,硬件首先自动对存取地址的列号字段进行译码,以便将联想存储器该列的全部行号与存取主存储器地址的行号字段进行比较:

若有相同的,表明要存取的主存储器单元已在高速存储器中,称为命中,硬件就将存取主存储器的地址映射为高速存储器的地址并执行存取操作;若都不相同,表明该单元不在高速存储器中,称为脱靶,硬件将执行存取主存储器操作并自动将该单元所在的那一主存储器单元组调入高速存储器相同列中空着的存储单元组中,同时将该组在主存储器中的行号存入联想存储器对应位置的单元内。

当出现脱靶而高速存储器对应列中没有空的位置时,便淘汰该列中的某一组以腾出位置存放新调入的组,这称为替换。确定替换的规则叫替换算法,常用的替换算法有:最近最少使用算法(LRU)、先进先出法(FIFO)和随机法(RAND)等。替换逻辑电路就是执行这个功能的。另外,当执行写主存储器操作时,为保持主存储器和高速存储器内容的一致性,对命中和脱靶须分别处理。

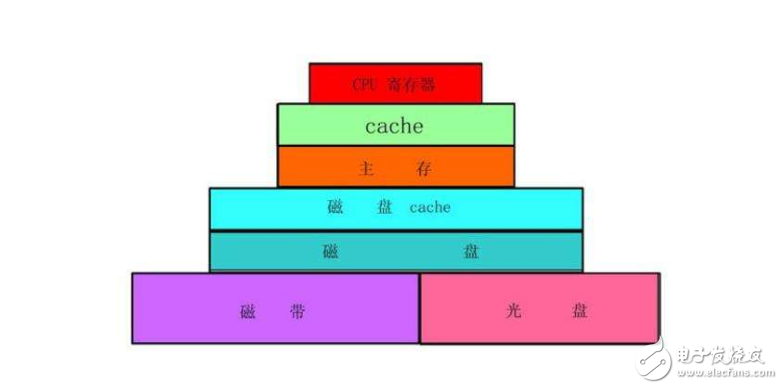

高速缓冲存储器存储层次

主-辅存存储层次 由于计算机主存容量相对于程序员所需要的容量来说总是太小,程序与数据从辅存调入主存是由程序员自己安排的,程序员必须花费很大精力和时间把大程序预先分成块,确定好这些程序块在辅存中的位置和装入主存的地址,而且还要预先安排好程序运行时各块如何和何时调入调出,因此存在存储空间的分配问题。

操作系统的形成和发展使得程序员尽可能摆脱主、辅存之间的地址定位,同时形成了支持这些功能的“辅助硬件”,通过软件、硬件的结合,把主存和辅存统一成了一个整体,如图所示。这时,由主存、辅存形成了一个存储层次,即存储系统。从整体看,其速度接近于主存的速度,其容量则接近于辅存的容量,而每位的平均价格也接近于廉价的慢速的辅存平均价格。这种系统不断发展和完善,就逐步形成了现在广泛使用的虚拟存储系统。

在系统中,应用程序员可用机器指令地址码对整个程序统一编址,如同程序员具有对应这个地址码宽度的全部虚存空间一样。该空间可以比主存实际空间大得多,以致可以存得下整个程序。这种指令地址码称为虚地址(虚存地址、虚拟地址)或逻辑地址,其对应的存储容量称为虚存容量或虚存空间;而把实际主存的地址称为物理地址、实(存)地址,其对应的存储容量称为主存容量、实存容量或实(主)存空间

高速缓冲存储器在电脑硬件中的位置分析

固化在CPU中的高速二级缓存这个硬件是固化在CPU中的,你在外面是看不到的。CPU档次的高低有相当一部分依赖于其二级缓存的大小。

CPU内

也就是所谓的L1 Cache, L2 Cache, L3 Cache

L应该是Level的缩写吧

速度以L1最快,L3最慢

不过就算是L3,速度也比内存快很多很多很多

购买的时候有关心这个啊

比如说到CPU缓存,一般指L2和L3 Cache

因为L1是用来存储短指令的,比较小,也没必要做很大

但是不同公司的CPU按照架构不同,对L2和L3依赖程度不一样

比如Intel的CPU就是L2, L3越大,性能越好

而AMD 的某些型号CPU就取消掉了L3,但是性能不见得比同级别Intel的来得差

自从酷睿时代开始以后,Intel的CPU就没有那么依赖L2,L3了,但是在奔4时代以前,L2,L3对超长流水线架构的CPU是很重要的

-

高速缓冲存储器是内存还是外存,高速缓冲存储器是为了解决什么2025-01-29 3244

-

EE-271: 高速缓冲存储器在Blackfin处理器中的应用2025-01-07 264

-

高速缓冲存储器有什么作用2024-09-10 4245

-

中央处理器与高速缓冲存储器之间的联系2022-02-10 1232

-

EE-271: 高速缓冲存储器在Blackfin®处理器中的应用2021-03-21 750

-

高速缓冲存储器的作用是什么_有什么特点2017-12-06 21812

-

高速缓冲存储器的作用解析2017-11-15 7944

-

高速缓冲存储器的分类及概述2017-10-17 3034

-

低功耗的高性能四路组相联CMOS高速缓冲存储器2017-01-19 748

-

高速缓冲存储器部件结构及原理解析2010-04-15 5019

-

存储器.ppt2009-04-11 872

全部0条评论

快来发表一下你的评论吧 !