分频系数是什么怎么计算?

电子常识

描述

分频系数是什么?

受外部周期信号激励的震荡,其频率恰为激励信号频率的纯分数,都叫做分频。实现分频的电路或装置称为“分频器”。(纯分数:只有分数部分,即小于1的分数,如3/4就是,而一又五分之四(1+4/5)就不是。)电路中的分频。

1、分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频。实现分频的电路或装置称为“分频器”。这里的分频上针对单频信号而言的。如把33MHZ的信号2分频得到16.5MHZ的信号,3分频得到11MHZ的信号,10分频得到3.3MHZ的信号。

这种分频一般指在数字电路。

2、分频是对信号中不同频率成分的各种信号分开,分成几个频率段。实现分频的电路或装置称为“分频器”。

这里的是针对由很多不同频率成分组成的混合信号而言的。

如将一个由20HZ-20KHZ组成的混合信号,分成小于20HZ-1KHZ和1KHZ-20KHZ两部分叫二分频,分成20HZ-500HZ、500HZ-2KHZ和2KHZ-20KHZ三部分的叫三分频。

这种分频一般指音响电路

分频系数么怎么计算?

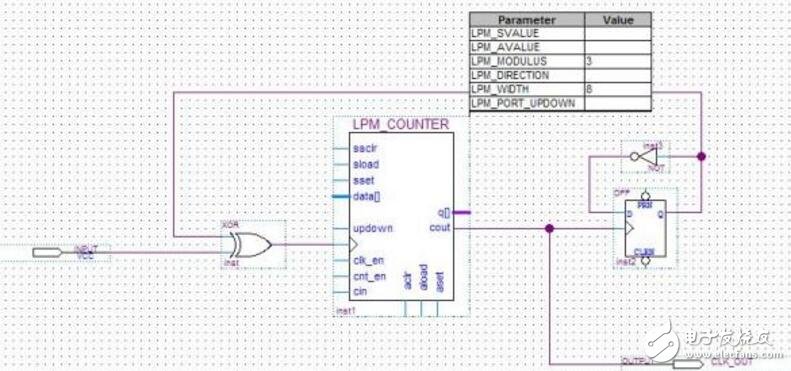

多个不同频率的信号可通过对某个基准频率进行分频器获得。由于各个音符的频率多为非整数,而分频系数又不能为小数,故必须将计算机得到的分频系数四舍五入取整。若基准频率过低,则分频系数过小,四舍五入取整后的误差较大。若基准频率过高,虽然可以减少频率的相对误差,但分频结构将变大。实际上应该综合考虑这两个方面的因素,在尽量减少误差的前提下,选取合适的基准频率。若选取750KHz的基准频率。由于现有的高频时钟脉冲信号的频率为12MHz,故需先对其进行16分频,才能获得750KHz的基准频率。对基准频率分频后的输出信号是一些脉宽极窄的尖脉冲信号(占空比=1/分频系数)。为提高输出信号的驱动能力,以使扬声器有足够的功率发音,需要再通过一个分频器将原来的分频器的输出脉冲均衡为对称方波(占空比=1/2),但这时的频率将是原来的1/2。

BCLK = 2 * word_select_size * fs;

假如word_select_size = 32; fs = 44100;bclk=2.8224M;

bclk一般从一个master时钟分频下来,假如叫做mclk;

如果mclk由主控的pll或者其他时钟源提供,那么mclk由此pll分频或者倍频得到;

假如pll=22.5792M,需要得到bclk为2.8224M的频率;提供如下一组分频系数(也有可能是其它分频系数)供参考:

mclk = pll/4 = 5.6448M;bclk=mclk/2=2.8224M;

mdiv = 4;bdiv = 2;

over_samplerate = 5.6448M/44.1k = 128

mclk:有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的128倍,256倍或384倍,也叫过采样(over_samplerate);

lrck_period的配置:

pcm mode:number of bclks within(left+right) channel width;

i2s/left-justified/right-justified mode:number of bclks within ech individual channel width(left or right)

N+1:

n=7; 8 bclk width

。。.

n=1023; 1024 bclks width;

- 相关推荐

- 热点推荐

- 分频器

-

adi_sport_ConfigClock的时钟分频系数和pcg clk的分频系数有什么关联?2023-11-28 563

-

STM32时钟分频系数的知识点汇总,绝对实用2021-12-15 2714

-

将系统的时钟分频器系数以及PLL的倍频系数配置好2021-08-23 1742

-

定时器时钟分频因子和预分频系数区别2021-08-09 4495

-

如果去设置独立看门狗预分频系数2021-08-02 1931

-

请问SPI通信的分频系数应该如何确定2018-12-28 10678

-

S8424构成的分频系数可变的分频器2018-10-03 816

-

一文详解分频器的计算和调整方法2018-05-29 137606

-

单机片预分频系数是什么怎么确定的2017-11-15 31633

-

任意分频系数小数分频器相关文档及源代码2009-08-03 695

-

分频系数可变的分频器2009-04-11 1552

-

多级放大器噪声系数的计算2009-03-12 18015

-

反馈系数计算公式2008-11-30 30494

全部0条评论

快来发表一下你的评论吧 !