系统级芯片六个优化方面详解

技术周刊

描述

***积体电路制造公司(简称为台积电(TSMC))最近宣布了其第四个28nm工艺进入了量产 - 28HPC Plus(即28HPC +)。台积电(TSMC)的前两项28nm工艺(聚氮氧化硅28LP和高K 金属闸28HP / 28HPL / 28HPM)已生产了数百万个生产晶片。台积电(TSMC)已利用28HPC优化了移动和消费设备在性能和成本之间的平衡需求,然后开发了28HPC +,从而进一步提高性能和降低泄漏。设计人员通过结合这些新工艺技术和专为这些工艺而设计的高质量标准单元逻辑库,可实现其性能、功耗和面积目标,同时减小设计进度风险。

本文介绍了六个方面,设计人员可以利用这些采用新工艺的最新逻辑库技术来优化其系统级芯片(SoC)的性能、功耗和面积。

首先,台积电(TSMC)28HPC/HPC+工艺相对于28LP/HP/HPL/HPM,能更好的控制全局慢速和全局快速(SSG,FFG)工艺角,因此可以提高系统级芯片(SoC)性能。改良的性能可以使用较低驱动(较小的)逻辑单元来满足关键时序路径。

其次,台积电(TSMC)对28HPC工艺进行更严格的工艺控制,可以减少对应工艺角中的20%漏电来降低功耗。

第三,28HPC +提高了15%性能,降低了25%漏电。

第四,28HPC和28HPC +都能减少面积,灵活的工艺规则,使得逻辑库设计者可以设计出更小的可布线性更好的逻辑单元。

第五,这些相同的灵活规则使得能够得到相对于28HPM工艺更长的沟道长度,从而减少最高50%的漏电,而不需要使用高成本的基于光刻的闸极偏置。

第六,在28HPC工艺引入的新的逻辑库功能,如多重延迟、多重建立时间和多位触发器(MBFF),可帮助设计人员优化处理器内核的性能和功耗。

创新工艺技术和逻辑库设计功能的结合,以及最新的EDA工具创新和流程,使系统级芯片(SoC)设计人员能够利用他们的设计技能,设计出最高性能、 最低成本、最低功耗的产品。

1.通过全局工艺角签核来提升系统级芯片(SoC)性能

传统开发的逻辑库,包括总工艺角工艺、电压、温度(PVT)模拟试验,可反映典型的P沟道和N沟道晶体管性能,统计学上性能最慢的(slow-slow或SS在3 sigma)和性能最快的(fast-fast或FF在3 sigma)。这些工艺角用于模拟典型的预期性能、最慢情况(用于触发器setup)和最快情况(用于触发器hold),且包括预期die和die之间、wafer和wafer之间以及lot和lot之间的变化,从而确保良率。

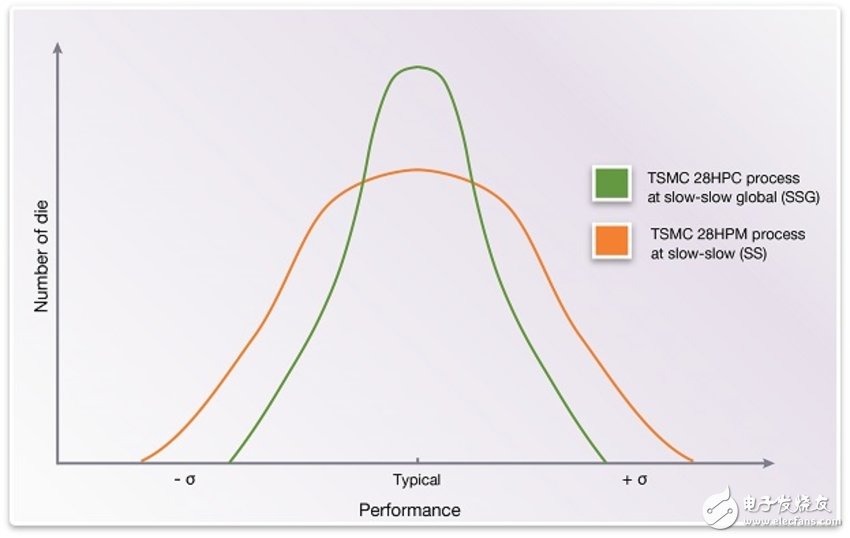

由于工艺变异性的降低,台积电(TSMC)能够提供高良率的新工艺角,称之为slow-slow global(SSG)。与之前的28HPM工艺相比提高了10-15%的性能,这需要更保守的SS 签核 (图1)。工艺变异性改进可使处理器运行速度提高10-15%,因此,28HPC逻辑库必须能够支持在更高的速度下电路的额外动态功耗和电迁移要求。

图1. 台积电(TSMC)28HPC SSG工艺角和28HPM SS 工艺角

2. 随着工艺变异性减小,闸门漏电流也减少

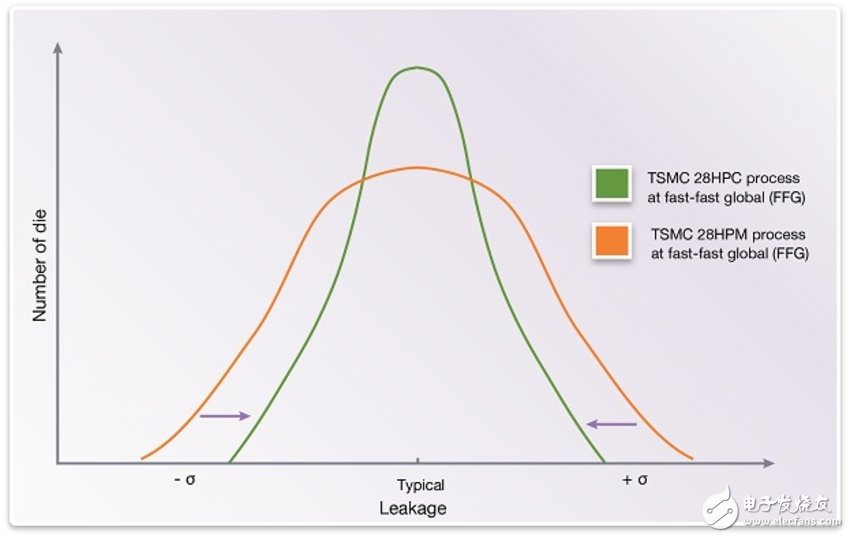

HPC工艺变异性的改进降低了晶体管泄漏,因此根据不同的工艺选项和条件,28HPC工艺将比28HPM减少约20%的漏电量(图2)。

图2. TSMC 28HPC FFG工艺角和28HPM FFG工艺角

3.使用28HPC +改进工艺秘诀

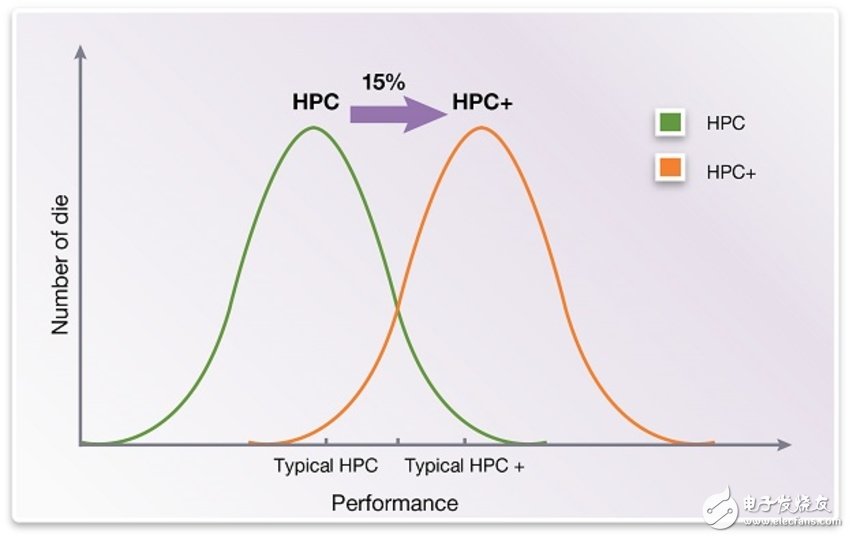

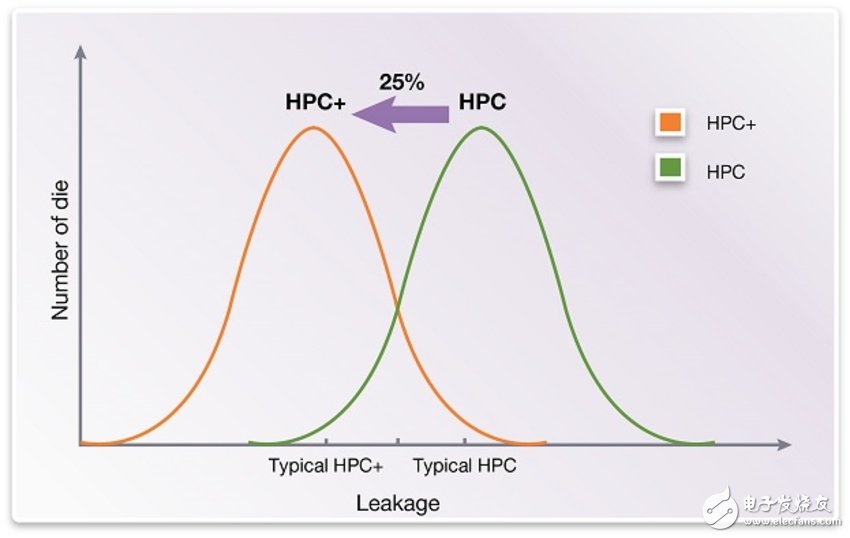

台积电(TSMC)利用28HPC +改善了28HPM和28HPC上使用的高K金属工艺,具有新的掺杂特性,并从高K金属闸上分离了一些原子,提高了15%的性能和降低25%的漏电流。

图3.左边的曲线显示了28HPC的性能分布,右图显示了28HPC +的性能分布。请注意,这些曲线比较了相同的SSG工艺角

图4.右侧曲线显示28HPC的漏电分布,左侧显示28HPC +处的漏电分布。请注意,这些曲线比较了相同的FFG工艺角

因为这是工艺中心的平移,而不仅仅是工艺的加强,现有的电路块或其它IP块至少需要重新验证是否存在违例,或重新进行综合以利用改良的性能和漏电。

4.更长的沟道长度减少漏电

工艺改进带动了台积电(TSMC)设计规则的变化,使得逻辑库相对于TSMC 28HPM可以有更多的栅极长度范围。

同时,新的灵活设计规则去除了一些光刻步骤,使得以30nm,35nm和40nm绘制的单元格能够以稍大的栅极间距来改善性能或漏电。

图5.上面的图显示,与下面的28HPM工艺相比,TSMC 28HPC / HPC +工艺的140nm间距和3个栅极长度,为连接提供了更多空间

更宽范围的栅极长度和相关的光刻简化,使设计人员能够使用28HPC优化的逻辑库,以及综合和布局布线工具中最新的漏电优化功能,得到更广泛的性能与漏电折中范围。

5.灵活的设计规则加强高密度

台积电在28HPC / HPC +工艺中的灵活设计规则和更高的性能,使设计人员能够在逻辑库中使用更矮的单元格高度,以便在一些能满足时序要求的block设计中,得到更小的芯片面积。使用较矮的逻辑库和实现更高速度之间存在一个折中,因为较矮的逻辑库需要更大的驱动单元,从而有可能抵消面积节省。 每个逻辑库在单元高度和性能之间都具有“最佳点”,以此来提供优化结果 ,但是采用更低高度的单元并不总是最好的办法。

图6:在较低的频率下,较矮的逻辑库可以是某些block的最优选择

也就是说,台积电的灵活设计规则使更矮的单元变得更容易绕线,如果逻辑库设计者利用布局和布线工具中的最新功能来设计逻辑库,则可通过更好的连接可能性来得到更高的利用率。

6.可大幅改良PPA的逻辑库设计创新

结合TSMC 28HPC / HPC +工艺与创新的逻辑库设计和优化布局的优点,可以帮助设计工程师通过综合和布局布线完成RTL数字逻辑设计。 使用优化的逻辑库电路(如组合逻辑,多重建立、多重延迟触发器和多位触发器(MBFF))以及TSMC 28HPC / HPC +工艺来获得面积及性能优势。

组合单元

优化寄存器到寄存器路径需要丰富的标准单元库,其中包含适当的功能,驱动强度和设计变化。需要合成优化功能(与非、或非、与、或、反相器、缓冲器、异或、同或、多路选择器、加法器、压缩器等),以创建最佳综合效果,优化的布局技术需要最大限度地利用最新的绕线算法来消除拥塞。先进的综合和布局布线工具可以利用不同的驱动强度,以最佳地处理由单元之间的设计拓扑和物理距离产生的不同扇出和负载。

时序单元

触发器的建立时间加上延迟时间有时被称为“死区”或“黑洞”时间。 像时钟不确定性一样,该时间可以侵蚀每个时钟周期,而该周期内本可以进行一些有用的计算工作。 需要各种类型的高性能触发器来对这死区时间进行优化处理。延迟优化的触发器(多重延迟触发器)快速地将信号发送到关键路径逻辑中,而建立时间优化的触发器(多重建立时间触发器)则可以更快的捕获寄存器。综合和绕线优化工具可以有效利用这些多重建立或多重延迟触发器组,从而提高15-20%的性能。

图7:时序单元用于解决高性能核心设计挑战。多重触发器可实现定向优化

图8:将两个单位触发器组合成具有共享时钟的双触发器

多位触发器提供了一组额外的触发器,已经针对功耗和面积进行了优化,在性能和布局灵活性方面进行了轻微的折中。触发器共享一个公共时钟引脚,这便降低了多位触发器单元中N个触发器的总时钟负载,减少相应的漏电功耗,并明显降低时钟树上的动态功耗(双重触发高达50%,四重或八重会降低更多)。

多位触发器通常用于不在最高芯片工作频率的关键路径模块中。它们的范围从小型的面向总线的系统级芯片(SoC)配置数据寄存器(仅在上电时计时)到每个周期都计时的、同时之间有多种变量的主要数据路径。系统级芯片(SoC)设计人员使用替换比率,通过设计中标准触发器的被替代的数量来衡量,和其产生的PPA改进结果,以确定其整体芯片功率和面积节省量。多位触发器和被替代的单位触发器也必须具有相同的功能(时钟边沿、置位/复位和扫描配置)。

图7显示了一个32位处理器,该处理器用TSMC 28HPM(蓝线)的逻辑库综合,且再次用TSMC 28HPC(橙色线)逻辑库综合,您可以发现会得到更小的面积以及更高的性能。而使用Synopsys高性能核心设计套件中的创新逻辑单元将使系统级芯片(SoC)设计人员在更小的面积内实现给定频率或者得到更高的频率,如红色和蓝色虚线所示。使用28HPC +工艺将该曲线向右移动15%。

图9:使用Synopsys逻辑库将28HPM工艺与28HPC工艺进行比较,并添加Synopsys HPC设计工具库,通过时序约束来设计32位处理器,直到该库无法使时序收敛

与最新数字EDA工具功能结合

TSMC 28HPC/HPC+工艺的逻辑库必须通过数字EDA工具来进行综合,布局,绕线,验证和优化以获得最优的性能,功耗和设计规则兼容性。数字EDA工具和流程使设计人员能够充分利用电路创新,如多位触发器和紧凑布局设计成最有效的逻辑库。

总结

台积电(TSMC)的28HPC高K金属闸工艺改进了工艺规则和可变性,以利用更少的功耗实现更小的设计,更高的性能。 台积电(TSMC)的新型28HPC +工艺进一步推动了其发展,并提供了令人难以抗拒的平台。如果他们拥有合适的逻辑库,并充分利用这些新的流程功能,领先的综合、布局和绕线工具可以最大利用这些工艺的改进来满足严格的设计规范要求。采用TSMC 28HPC / HPC + 工艺的Synopsys逻辑库和领先的EDA工具,旨在使系统级芯片(SoC)设计人员能够追求性能、面积和功耗的极限,并充分利用这些新工艺的功能。

-

新型开关电源优化设计与实例详解 ( 六 )2012-04-09 2013

-

请教一下,一个六个脚的芯片上面丝印字是AMBK,请问是什么2012-11-14 4438

-

有六个仿真器,想处理掉!2016-11-07 2593

-

关于六个自由度座椅的控制2017-01-13 3722

-

sd可以实现六个面对应六个不同文件夹sd音乐吗?2020-08-12 1339

-

六个电视游戏电路2009-01-17 912

-

六个有关RoHS的检测方法标准2009-08-12 1558

-

六个数码管轮流显示数字2016-05-11 980

-

学习PLC编程技巧的六个方面的经验分享2018-08-26 14280

-

PCB设计的六个检查阶段2019-05-15 4806

-

PROTEL DXP的六个实验指导教程2019-10-29 1431

-

算法:计算Fibonacci number的六个方法2020-06-22 3361

-

六个方面了解嵌入式的硬件构架资料下载2021-04-14 896

-

射频脉冲信号典型的六个知识点2022-09-19 5890

-

汽车电源设计的六个基本原则2023-11-13 492

全部0条评论

快来发表一下你的评论吧 !