使用PAM4实现印刷电路板的优化

电路板测试

描述

随着物联网(IoT)和5G行动宽带应用的兴起,预计总体数据流量将会迅速增长,400G以太网络(400GbE)作为新一代有线通讯标准,能够有力支持这一趋势。在400GbE通讯的实施中,其电气接口在8信道上传输4电平脉冲幅度调制(PAM4)讯令。每信道50Gbps,总共8个信道结合起来,使以太网络的总带宽可以达到400Gbps。IEEE802.3bs定义了使用50Gbps(即25GBaud)PAM4讯令的400GbE的电气规范。

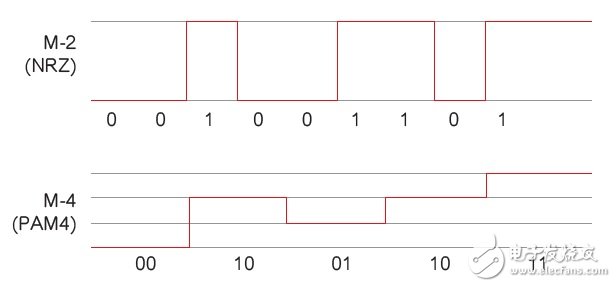

PAM4具有4种数字幅度电平,如图1所示。与NRZ相比,PAM4的优势是每个电平或符码都包含两个信息bit,在相同的波特率下,吞吐量是NRZ的两倍。

图1 NRZ与PAM4的对比。在相同的波特率下,PAM4的吞吐量是NRZ的两倍。

考虑电源完整性的关键设计实现

一旦PDN上的开关噪声耦合至收发器集成电路(IC)的电源层,传输讯号中将感应到抖动,这可能会增加接收IC中的bit误码率。为了让噪声波纹保持在较小水平,符合设计规范,PDN阻抗应低于目标阻抗。目标阻抗由公式1决定。

公式中: Vripplemax = 电源轨上的最大波纹; Imax = 由集成电路载入的最大电流。

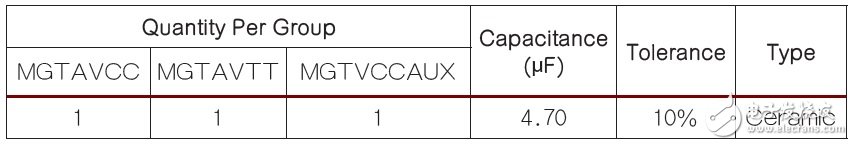

为了最大限度降低PDN阻抗,要特别关注去耦电容、互连电感和电源平面电容等印刷电路板(PCB)组件。去耦电容应安装在靠近高速收发器电源接脚的位置,以减少PDN阻抗,进而在噪声耦合进收发器IC封装电源平面之前,减少来自外部源(如稳压器和其他开关IC)的噪声,高速收发器电源接脚的噪声将低于10mVpp。为赛灵思(Xilinx)FPGA上的高速收发器电源接脚推荐的最小电容数量如表1所示,在靠近每个高速收发器电源组(即MGTAVCC、MGTAVTT和MGTVCCAUX)的位置都安装了1个4.7μF陶瓷电容器。

表1 为Xilinx FPGA上的高速收发器电源接脚推荐的电容数量。

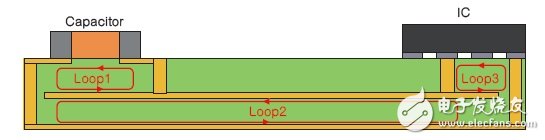

当互连电感减少时,PDN阻抗会相应降低。互连电感主要由走线(连接电容的贴装焊盘与过孔)的寄生电感引起。根据图2所示的印刷电路板的剖面图,每个互连回路(图中标示为回路1、2、3)中都会形成互连电感。去耦电容器要尽量安装在靠近IC电源接脚的位置,以最大限度减少互连电感。

图2 印刷电路板内的互连电感。

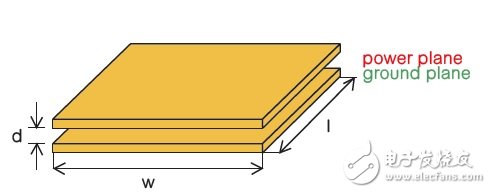

当印刷电路板迭层中的电源平面和接地面之间形成的平面电容增加时,PDN阻抗会降低。参见图3所示的平面电容基础模型和公式2,透过缩小平行面之间的厚度,增加电源平面与接地面之间并行面的面积,或使用具有较大介电常数的基片,电容会相应升高。

公式中: εr = 基片的介电常数; εo = 真空介电常数; w = 铜片宽度; l = 铜片长度; d = 基片厚度。

图3 印刷电路板迭层中的平面电容基础模型。

实现考虑讯号完整性的关键设计

根据指南,印刷电路板上走线长度达到8英吋的PAM4通道在14GHz和28GHz分别具有低于10dB和20dB的插入损耗,从而在收发器之间实现无缝数据通讯。以下将从讯号完整性的视角讨论7个关键设计实践。

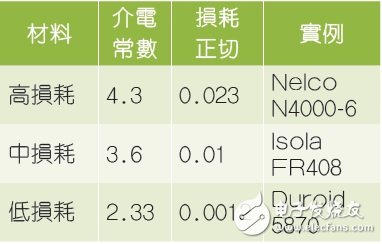

1.为印刷电路板基片选择低损耗材料 根据介电特性(例如损耗正切和介电损耗),印刷电路板基片介电材料可以分为3类。

如表2表示,高损耗材料(如Nelco N4000-6)的损耗正切值超过0.02,介电常数超过4;中等损耗材料(如Isola FR408)的损耗正切值约为0.01,介电常数在3和4之间;低损耗材料(如Duroid 5870)的损耗正切值约为0.001,介电常数低于3。介电衰减与损耗正切和介电常数的平方根成正比,如公式3所示。

介电衰减 = 0.91×.×损耗正切 ×√εr dB/cm (3)

公式中: εr = 介电常数(Dk); f= 频率(GHz)

表2 介电材料种类。

利用公式1在14GHz频率和8英吋走线长度条件下进行计算,从结果可见,高、中和低损耗材料的介电衰减分别为12.35dB、4.91dB和0.47dB。之前已经提到,在14GHz频率、8英吋走线长度条件下,插入损耗低于10dB,应选择较低损耗的材料,以便为其他通道损耗留出裕量。

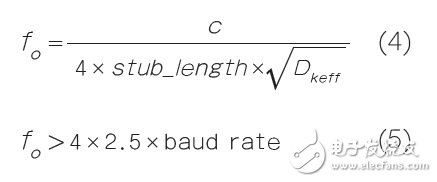

2.最大限度减少过孔残桩 当使用过孔来连接印刷电路板走线至IC时,应使用盲孔或反钻孔(如图4所示),以最大限度减少残桩长度,进而提高1/4波谐振频率,增加物理层链路的带宽。参考公式4,1/4波谐振频率与残桩长度成反比。重新排列公式4和5,对于使用低损耗材料的印刷电路板上的50Gbps(即25GBaud/s)PAM4传输,Dkeff为2.33,最大残桩长度可以达到大约16mil。

公式中: fo = 1/4波谐振频率(Hz); c = 光速(约12英吋/ns); 残桩长度(英吋); Dkeff=有效介电常数。

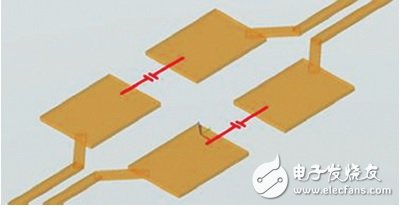

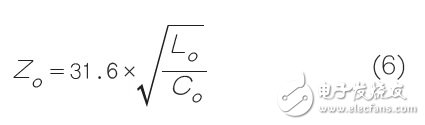

3.最大限度减少交流耦合电容表面贴装焊盘造成的阻抗失配 与印刷电路板走线相比,交流耦合电容表面贴装焊盘使用的铜片更宽。例如,0402封装中的电容贴装焊盘宽度为20mil,而0603封装的焊盘宽度为30mil。图5显示与100Ω差分走线(differential trace)串联的电容器表面贴装焊盘的3D模型,从图中可以看出,沿着这些6mil宽的铜片走线传播的讯号,一旦到达更宽的铜片焊盘(例如0603封装的30mil宽度),会遇到阻抗不连续性。根据公式6和7,铜片的横截面积越大,电容就越大,导致传输线特征阻抗出现电容不连续性(如下降)。

图4 盲孔或反钻孔。

图5 使用Keysight EMPro建模电容表面贴装焊盘与差分走线串联。

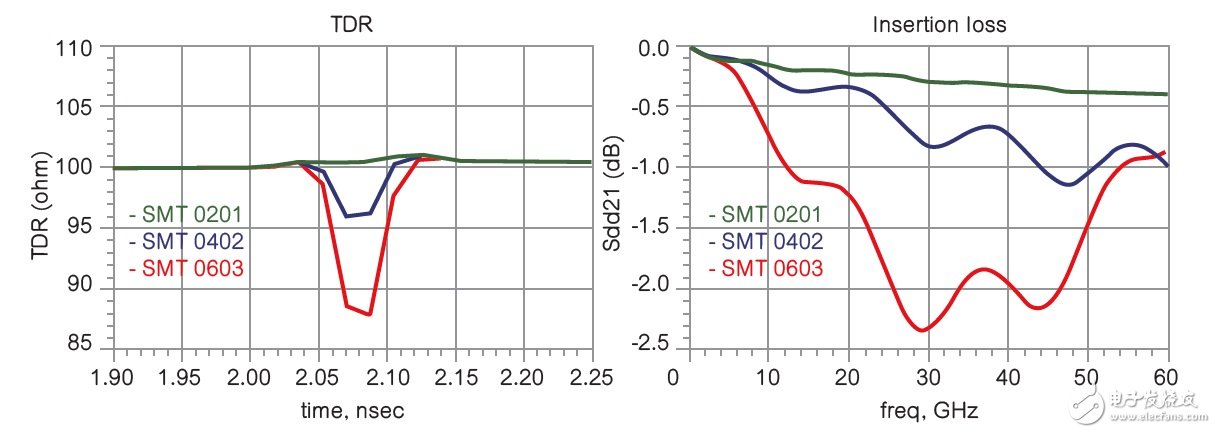

从图6的时域反射计(TDR)和Sdd21曲线可知,焊盘越宽,阻抗不连续性就越大,这种不连续性会产生更严重的讯号反射,进而引起更大的插入损耗。0603和0402在14GHz时的衰减分别为1.2dB和0.4dB,至少两倍于0201(即0.2dB)的情况。因此,设计师应该使用封装更小的电容器,例如0201(即10mil宽焊盘)来最大限度减小不连续性。

公式中: Lo = 传输线单位长度的固有回路电感(nH/cm); Co = 传输线单位长度的固有电容(pF/cm); Zo= 特征阻抗(Ω);

公式中: C = 电容(pF); Εr = 基片的相对介电常数; εo = 真空介电常数; w = SMT焊盘宽度(cm); l = SMT焊盘长度(cm); d = SMT焊盘和参考面底部之间的距离(cm)。

图 6及7 使用Keysight EMPro模拟不同表面贴装焊盘宽度的TDR和Sdd21与500mil长的印刷电路板走线串联。

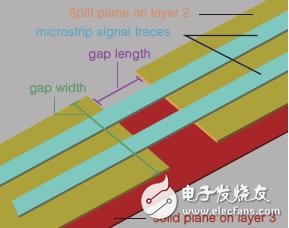

4.提供连续参考面 当印刷电路板走线跨越2个分离平面之间的间隙时(图7粗黑线所示),会遇到电感阻抗不连续性或瑕疵参考。这一现象可用公式6和8分别确定。为了研究瑕疵参考的影响,在EMPro中建立并模拟跨越分离平面的传输线3D模型,如图8所示。微带差分走线跨越了100mil长和250mil宽的间隙,间隙深度为微带差分走线与第三层固体面的间距,跨越间隙时,走线与参考底面之间的距离会增加(即电流返回路径变长),导致电感升高,从而引起间隙的走线阻抗增加。

图8 印刷电路板俯视图—讯号跨越分离面。

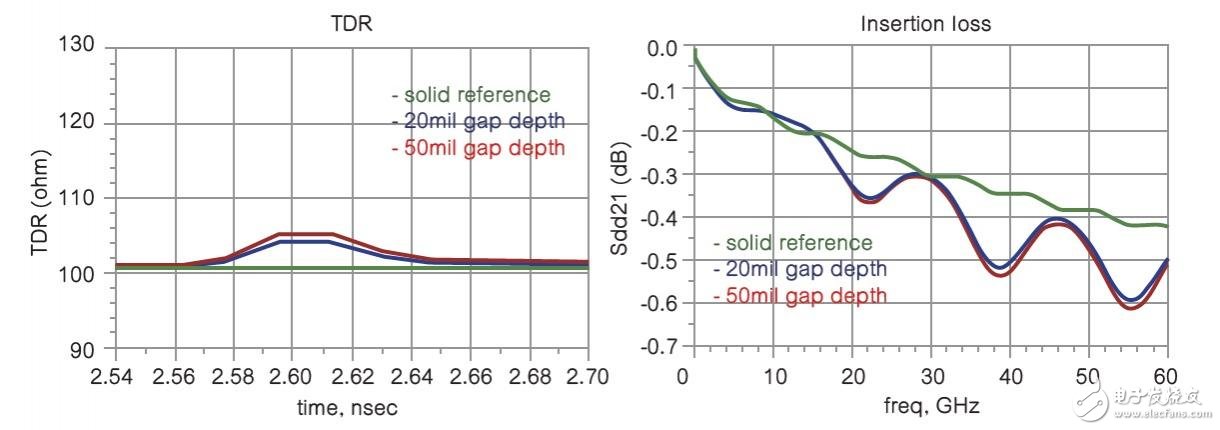

图9中的TDR和Sdd21曲线证实了非固体参考面对讯号完整性的负面影响,跨越分离面会产生更大的电感阻抗不连续性,进而导致更高的插入损耗。因此,确保固体参考面覆盖整个走线长度路径十分重要。

公式中:L = 铜走线的寄生电感(nH); d = 铜走线和参考底面之间的距离(cm); w = 铜走线宽度(cm); t = 铜走线厚度(cm); x = 铜走线长度(cm)。

图9 Keysight EMPro中差分走线跨越分离面的模型。

5.最大限度减少讯号串扰 串扰会引起受扰讯号出现噪声感应,从而导致接收集成电路的误码增加。因此,带状在线使用非交叉布线,因为FEXT相比NEXT更低;而在微带在线使用交叉布线,因为与FEXT相比NEXT更低。除此之外,差分对间间隔应至少是走线宽度的三倍。

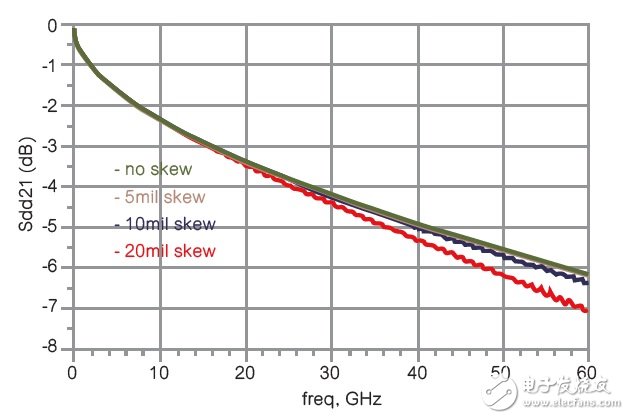

6.差分对内偏移 印刷电路板走线中的差分对内偏移会带来更高的插入损耗,从而增加物理层链路的误码率。由于反相和非反相讯号的相位并不是正好相差180度,所以差分模式中的眼图高度会变小。图11中的Sdd21曲线显示了差分对内偏移对讯号完整性的影响,偏移越大,插入损耗越高。因此,每个物理层链路的差分对内偏移都应限制在5mil以内,以减少传输损耗,可以使用蛇形布线技术来最大限度减少偏移。

图10 使用Keysight EMPro模拟、带固体参考面并跨越分离面的500mil长印刷电路板走线的TDR和Sdd21。

图11 使用Keysight ADS模拟、具有不同差分对内偏移的8英吋长印刷电路板走线的Sdd21。

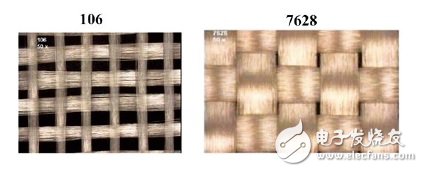

7.光纤编织 印刷电路板介电基片由编织玻璃纤维与环氧树脂结合组成。图12是使用显微镜看到的、采用纤维编织样式106和7628制成的印刷电路板基片的俯视图,浅棕色粗线是玻璃纤维编织部分;黑色的方块是环氧树脂。编号更高的玻璃纤维样式,如7628,可以实现更密集的玻璃纤维编织。

图12 印刷电路板的介电基片是利用玻璃纤维样式106和7628编织的纤维织物。

玻璃纤维与环氧树脂的介电属性截然不同。例如,NE玻璃纤维的介电常数(Dk)和损耗正切(Df)分别为4.4和0.0006;E玻璃纤维的Dk和Df分别为6.6和0.0012,而环氧树脂的Dk为3.2,远远低于玻璃纤维的对应值。当使用较为稀疏的纤维编织做基片时,印刷电路板走线能够更频繁地穿过树脂和玻璃纤维的不同区域,结果就是,讯号沿着走线从发送端传输到接收端,其速度或传播延迟经常会发生变化。它们之间的关系可以透过公式9来说明。

公式中:V = 讯号在印刷电路板上的速度(英吋/ns); C = 光速(约12英吋/ns); Dk = 介电常数。

这种情况为50Gbps讯号传输带来了巨大挑战。例如,在最坏情况下,非反相讯号走线可能穿过玻璃纤维但没有穿过环氧树脂,而反相讯号的走线可能穿过很多树脂区域。结果,由于反相讯号遇到不断变化的传播延迟,非反相讯号与反相讯号之间的相位差在接收端一般会远远小于180o。上升端和下降端之间的大偏移或错位,导致眼图宽度和高度减少,而且,接收端会出现高误码率。因此,解决办法就是采用更密集的纤维编织。

布局后的通道仿真

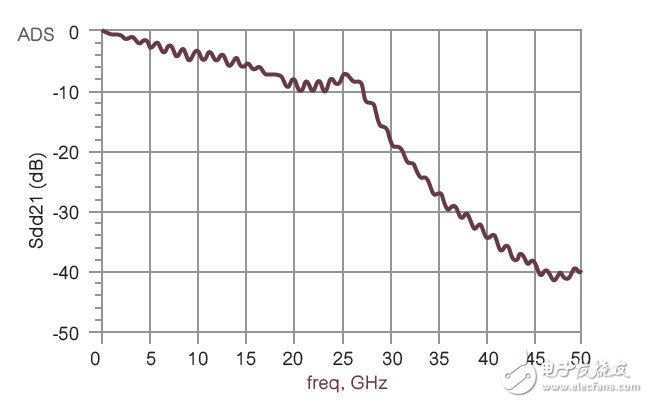

一旦按照上述关键实践完成了印刷电路板布局设计,布局档将导入Keysight EMPro进行3DEM模拟。选择图13中突出显示的8英吋长差分走线进行s参数抽取,将其导入Keysight ADS进行布局后PAM4通道仿真。图14中的插入损耗曲线显示提取的差分走线符合规定的阈值,即在14GHz时低于10dB;在28GHz时低于20dB。

图13 选择差分走线用于3DEM模拟。

图14 印刷电路板上所选PAM4差分走线的插入损耗曲线。

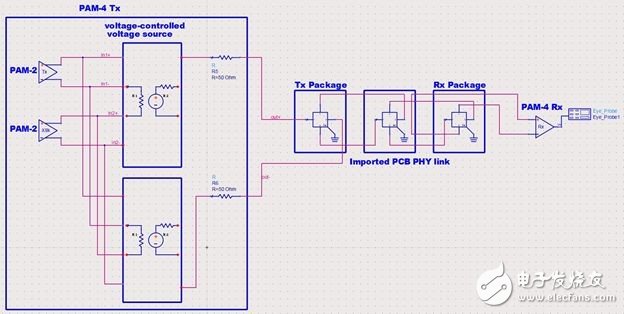

图15显示使用Keysight ADS生成的通道分析拓扑,两个25GBaud/s的PAM2讯号注入压控电压源以生成PAM4讯号。PAM4波形的传播路径为:发射端封装、8英吋PCB走线(即图13中显示的传输线)、接收端封装,最后是接收端。在发射端,讯号幅度和上升/下降时间分别为1.2Vpp和16ps。

图15 使用Keysight ADS在25GBaud/s下进行布局后PAM4通道仿真。

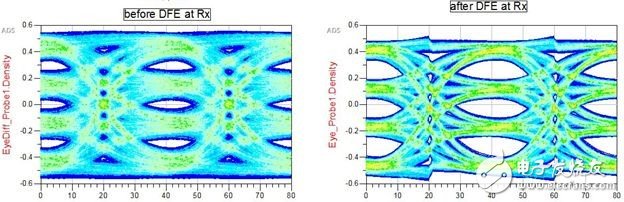

PAM4讯号的最小眼宽和眼高分别为1/4单位间隔(即25GBaud/s数据速率下为10ps)和50mV。如图16所示,PAM4眼图有4个数字幅度电平,因此有3个眼图。在启用决策回馈均衡(DFE)前,接收端讯号的眼高和眼宽分别为60mV和14ps,一旦启用接收端的6接头DFE,眼图几乎变大一倍(即140mV眼高和23ps眼宽),结果符合指南中的技术指针。均衡方案的选择和接头的调节很大程度上取决于通道的插入损耗或频率响应。本文进行了多次尝试来获得更好的开眼结果。

图16 从图15中的通道仿真结果得到的接收端眼图。

结论

实施50Gbps PAM4物理层链路时必须严格要求,确保在高速收发器之间实现稳定的通讯。

- 相关推荐

- 热点推荐

- 电路分析

-

印刷电路板图设计的基本原则2014-05-15 3215

-

印刷电路板设计原则2008-07-13 1242

-

印刷电路板的设计与制作2010-02-11 1042

-

什么是柔性印刷电路板?2006-04-16 1840

-

印刷电路板图的识图方法2008-11-08 5708

-

印刷电路板2009-09-30 1859

-

印刷电路板设计的基本原则2009-11-17 730

-

什么是单面印刷电路板?2009-12-09 2752

-

Protel设计印刷电路板应考虑的问题2010-04-16 1102

-

印刷电路板设计基础课程2017-01-05 1019

-

印刷电路板设计2018-03-28 972

-

印刷电路板图设计的基本原则和要求2019-04-12 4247

-

什么是PCB助焊剂?印刷电路板焊接的目的2020-11-23 5302

-

如何设计和创建自己的印刷电路板2020-10-20 2981

-

印刷电路板专用阻焊剂有哪些特点2020-11-17 4660

全部0条评论

快来发表一下你的评论吧 !