创建工程项目并使用三种方法下载工程项目到Basys3 FPGA开发板上教程

FPGA/ASIC技术

描述

概述

Basys 3 支持以下三种方式配置/下载程序:

. JTAG

. Quad SPI Flash

. USB Flash Drive

此教程旨在告诉初学者如何开始创建工程项目以及分别通过以上三种方法下载工程项目到Basys3 FPGA开发板上。

前期准备

硬件

. Basys3 FPGA开发板

. Micro-USB线

软件

. Vivado Design Suite 2017.1

Ø 新版或旧版Vivado均可使用,但是步骤可能有些许不同

源文件

. basys3_sw_demo.zip

教程

1. 创建工程项目

首先,我们要创建一个工程项目

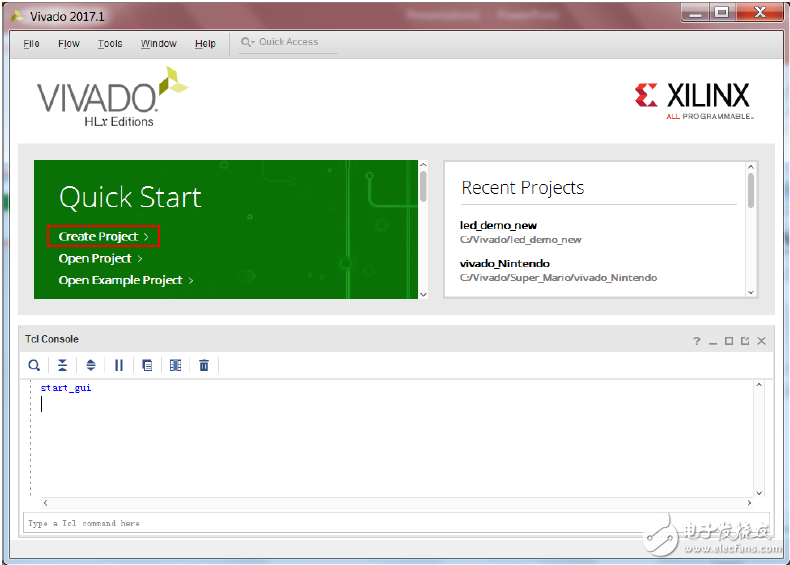

1.1 打开Vivado,在初始界面单击‘Create Project’。

1.2 在新弹出的窗口中单击‘Next’。

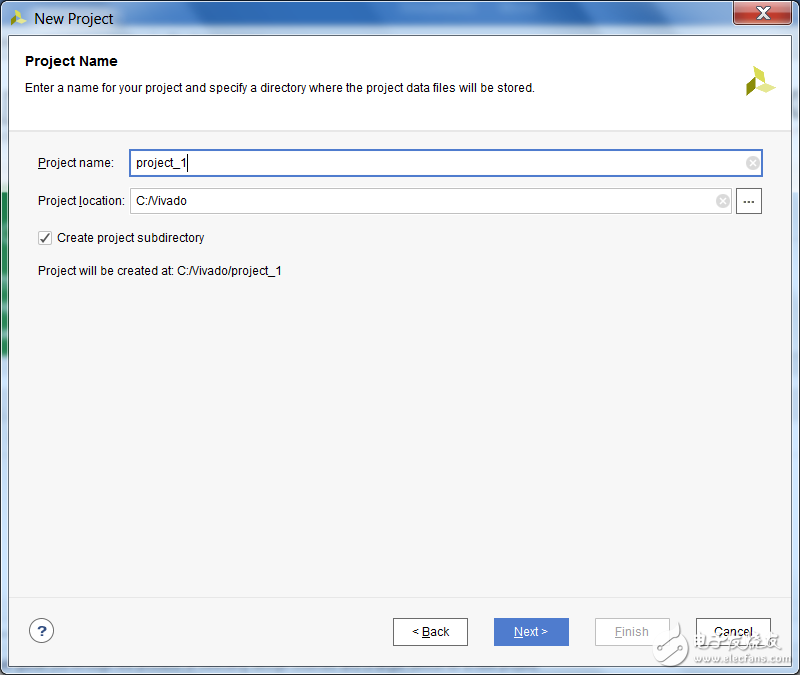

1.3 输入创建的项目名称,选择项目的保存路径,然后单击‘Next’。

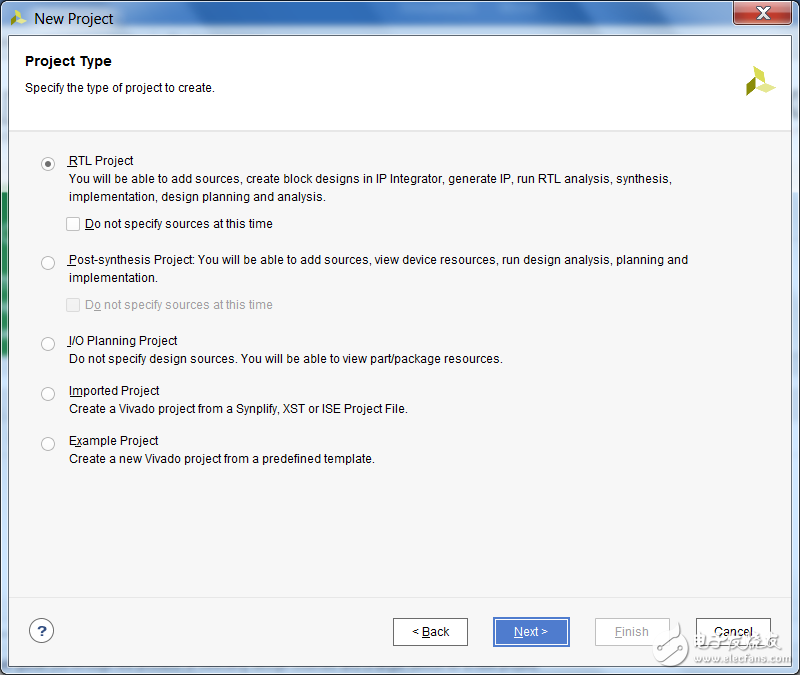

1.4 我们将从底层开始完整的创建一个项目,所以这边我们选择创建一个‘RTL Project’,然后单击‘Next’。

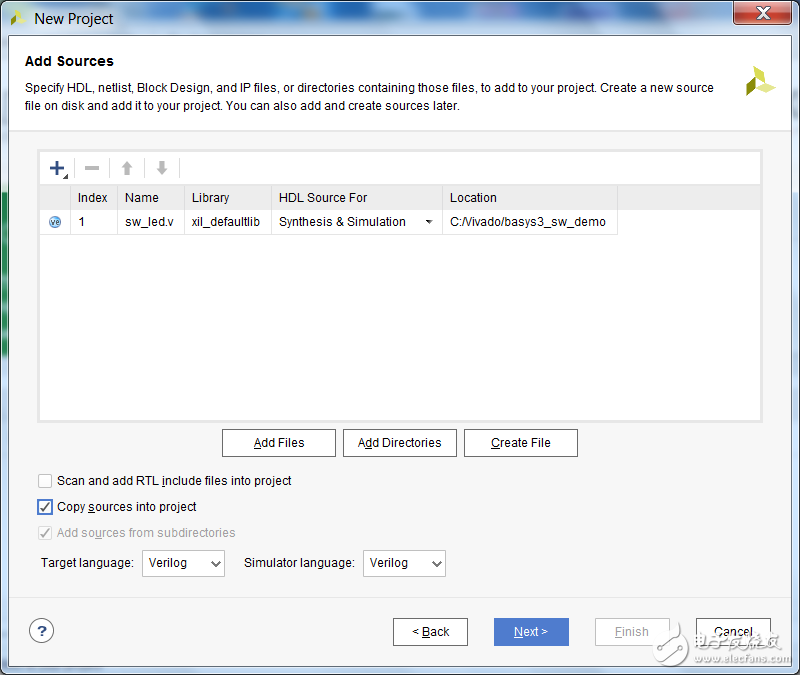

1.5 在这个窗口中,我们可以添加任何项目中需要用到的源文件或者文件夹,创建新的空文件,选择目标编程语言和模拟器语言。在这个教程中,我们只需要添加压缩包中已经编辑好的源文件即可。单击窗口左上角的26.png选择‘Add Files…’或者直接单击窗口中间的‘Add Files’,找到解压文件夹中的‘sw_led.v’文件,单击‘OK’。需要勾选‘Copy sources into project’, 这样Vivado会复制一份源文件到创建的工程项目文件夹中。否则,Vivado不会复制源文件到项目文件夹中,而是直接读取/修改源文件。单击‘Next’。

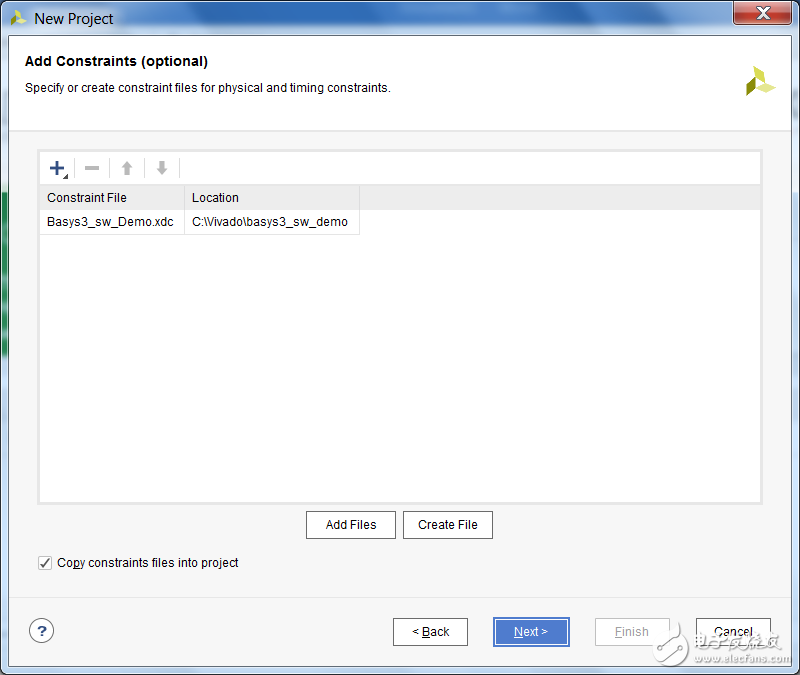

1.6 在这个窗口中可以添加约束文件(.xdc),在这个样例中仿照上一步找到解压文件夹中‘Basys3_sw_Demo.xdc’文件添加即可。单击‘Next’。

>

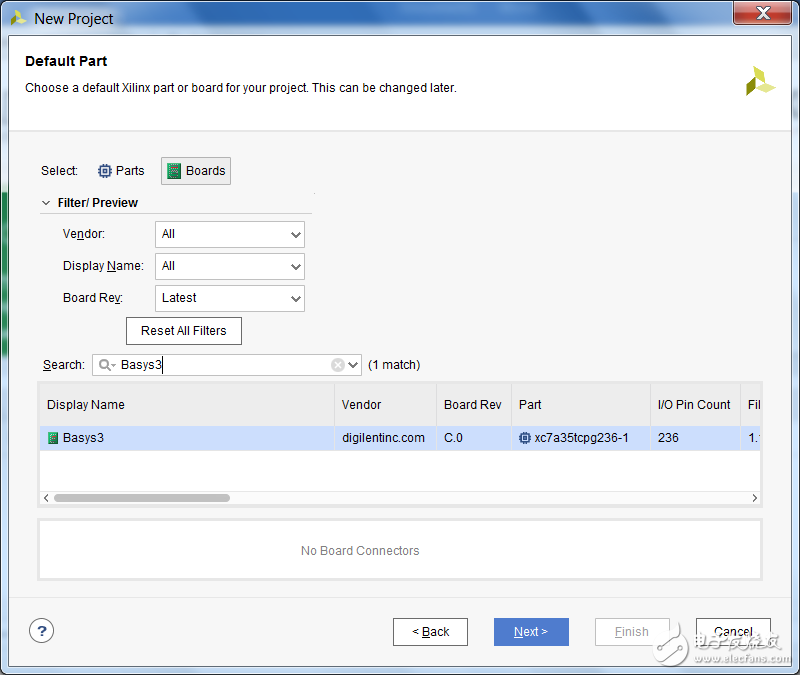

1.7 在这个窗口中,我们要选择Basys3开发板。单击‘Board’,搜索‘Basys3’,选中Basys3开发板,单击‘Next’。

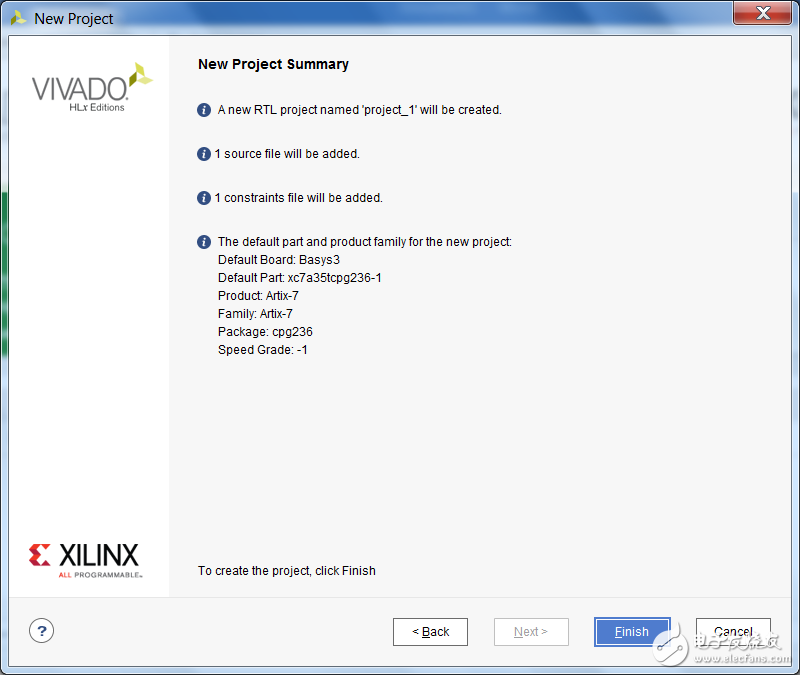

1.8 这个窗口是创建新的工程项目的总结信息,单击‘Finish’。

2. 创建下载文件(Program File)

Basys3 FPGA可以使用三种方式将文件下载到Basys3 FPGA开发板上,有两种支持的文件类型,.bit文件和.bin文件。.bit文件可以通过JTAG下载线或者标准USB存储设备下载到Basys3 FPGA。.bin文件将在每次通电时自动通过Quad SPI下载到Basys3 FPGA。接下来将会介绍配置Basys3的准备步骤:

2.1 Vivado默认只会生成.bit文件,之后将介绍通过Quad SPI配置Basys3 FPGA,所以需要通过如下步骤生成.bin文件。

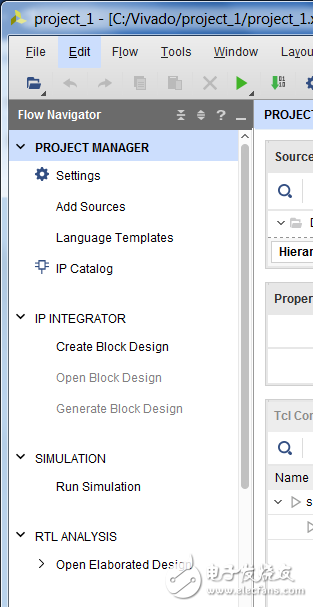

在‘Project Manager’中单击‘Settings’

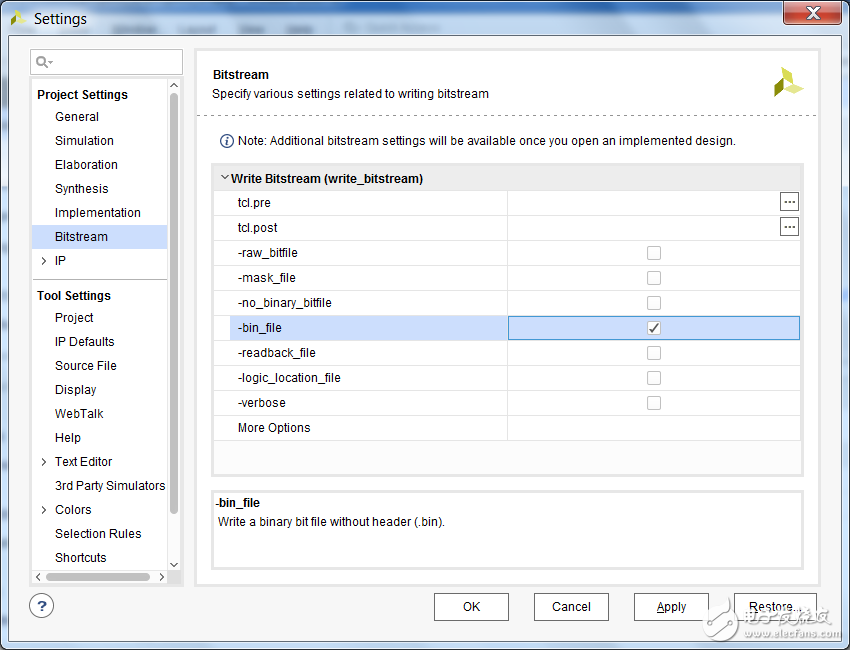

在‘Project Settings’中单击‘Bitstream’,勾选‘-bin_file’选项,单击‘OK’。

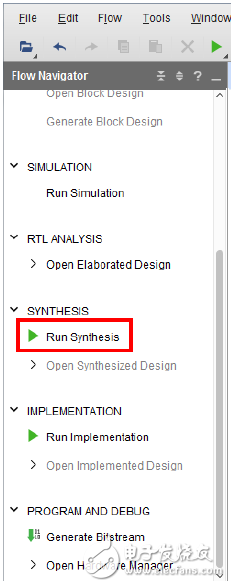

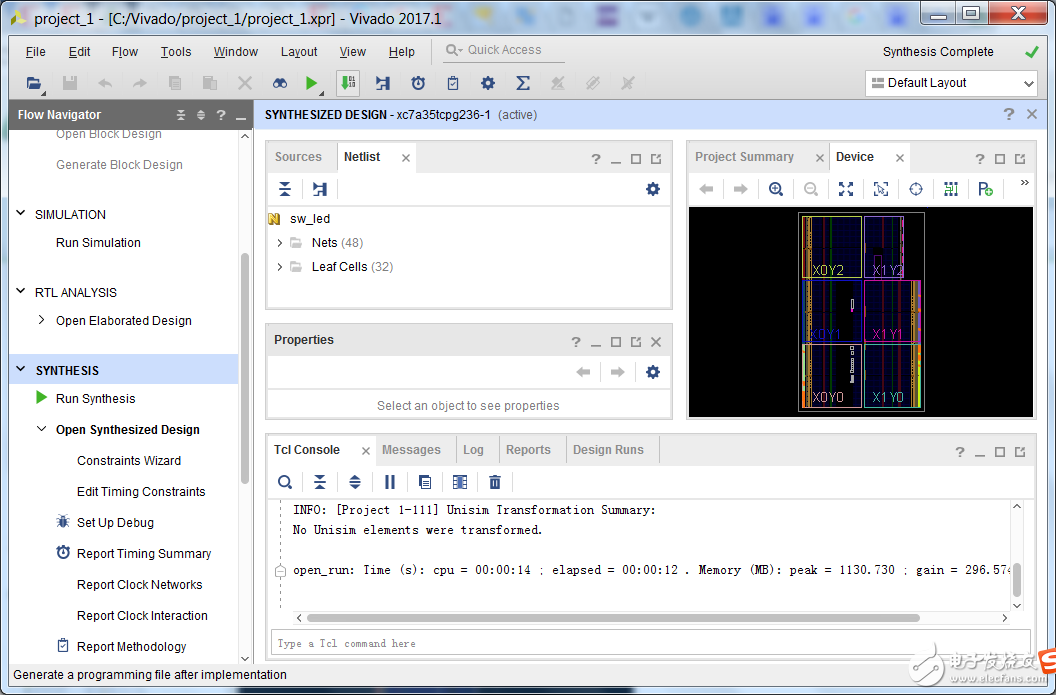

2.2 接下来,我们需要对工程项目进行综合,单击主界面左侧‘Flow Navigator’中的‘Run Synthesis’。使用默认路径保存综合和实现文件,单击弹出窗口中的‘OK’。

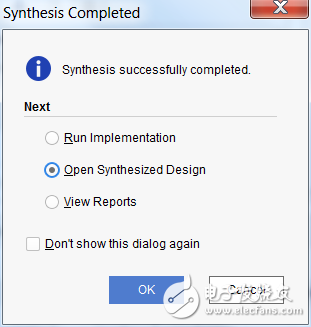

2.3 综合完成后会弹出窗口,选中‘Open Synthesized Design’,单击‘OK’查看综合结果。

2.4 我们可以在窗口右侧看到工程项目在Basys3 FPGA上的综合结果。

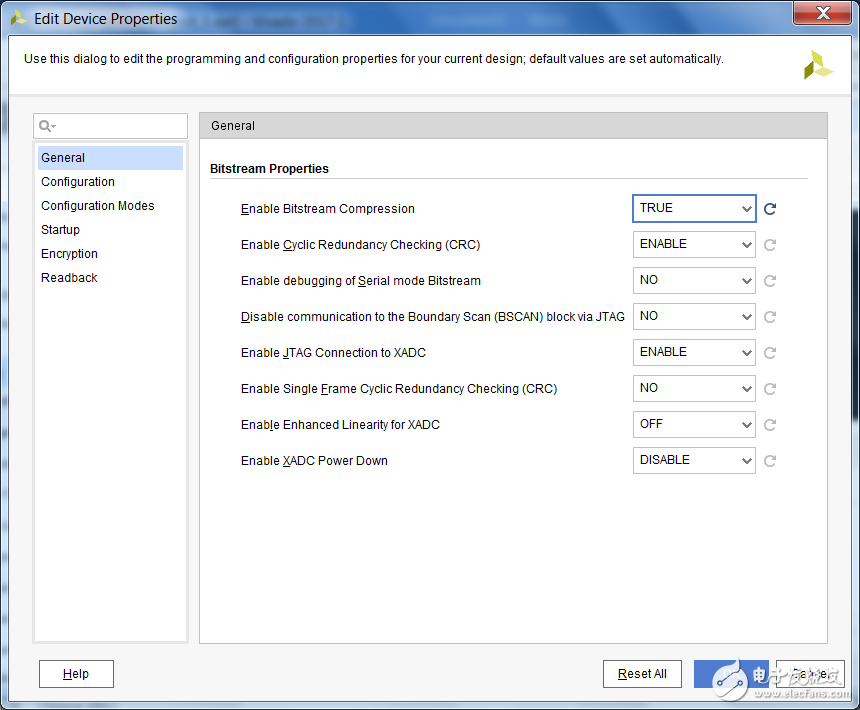

2.5 为了提高.bin文件的下载速度,需要设置Vivado使其允许对比特流进行压缩。单击主工具栏中的‘Tools’>单击‘Edit Device Properties…’。在弹出窗口的General一项中,将‘Enable Bitstream Compression’设置为‘TRUE’。

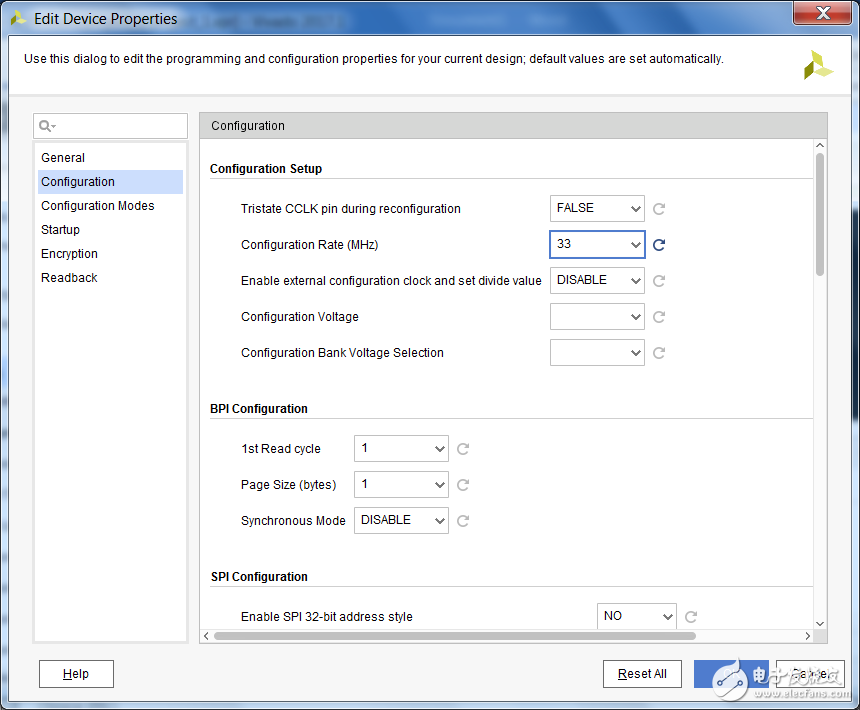

2.6 在Configuration一项中将‘Configuration Rate (MHz)’设置为33 MHz。

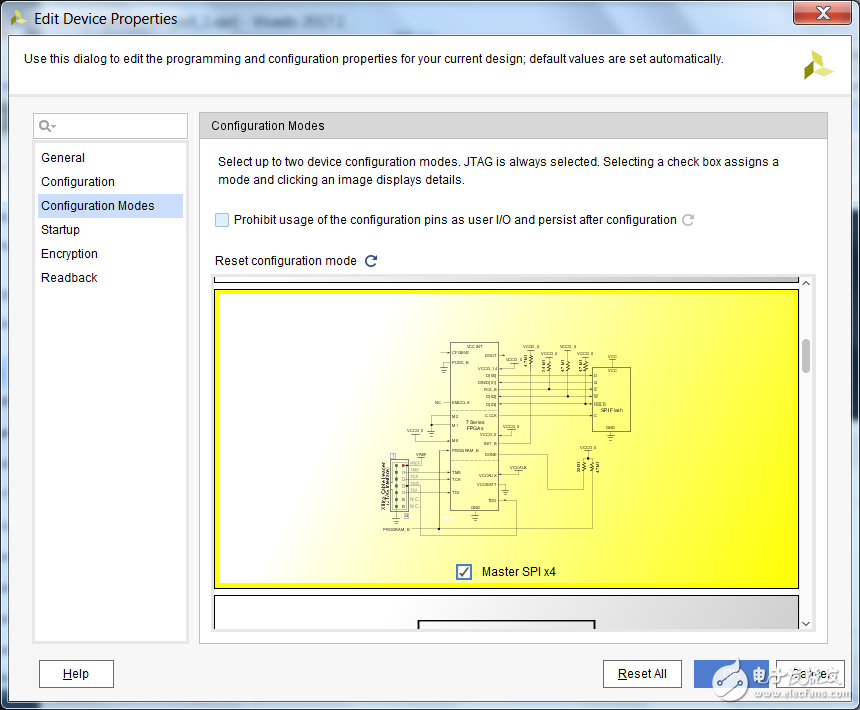

2.7 在Configuration Modes一项中勾选‘Master SPI x4’。单击‘OK’。

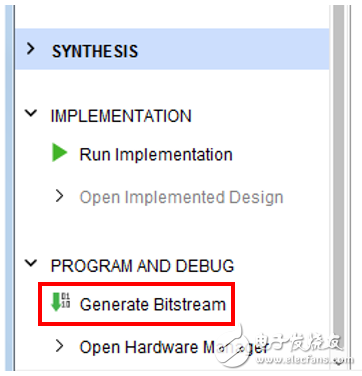

2.8 对之前的设置进行保存(Ctrl+S)。Vivado会提示需要更新约束文件,单击‘OK’即可。在‘Flow Navigator’中展开‘Program and Debug’,单击‘Generate Bitstream’。

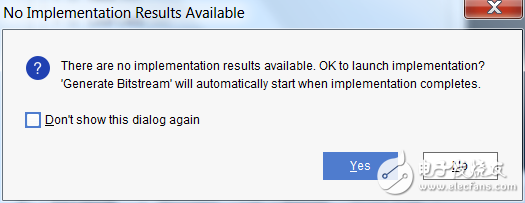

2.9 Vivado会提示还没有对项目进行仿真实现(Implementation),如下图单击‘Yes’,Vivado会先进行实现,然后生成比特流文件(.bit和.bin),将文件保存在默认路径下,单击‘OK’。

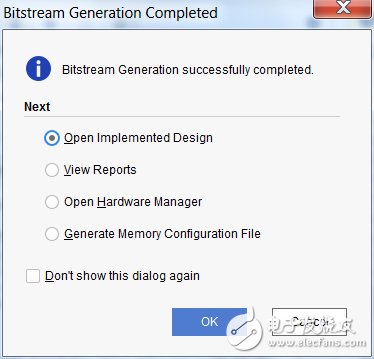

2.10 Vivado会开始生成.bit文件和.bin文件。完成后,会弹出如下窗口,我们可以选择‘Open Implemented Design’查看实现的结果,或者选择‘View Reports’查看完整的设计报告。

至此,我们已经完成了将工程项目下载到Basys3 FPGA开发板的准备工作。接下来,将分别介绍通过三种方式下载/配置Basys3 FPGA。

3. 通过JTAG下载/配置Basys3

JTAG是通过micro-USB端口和PC进行通信的,主要用于下载,调试和端口探测。这使得Basys3 不仅可以通过micro-USB端口供电,而且可以通过micro-USB端口进行下载和调试。

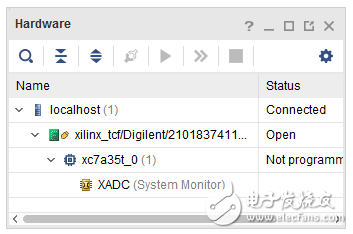

3.1 首先,将模式跳线JP1设置成JTAG模式,将Basys3通过micro-USB连接到PC的USB接口,打开电源。在‘Flow Navigator’中,单击‘Open Target’,选择‘Auto Connect’。在Hardware窗口中,我们可以看到Basys3 FPGA已经完成了和PC的连接。

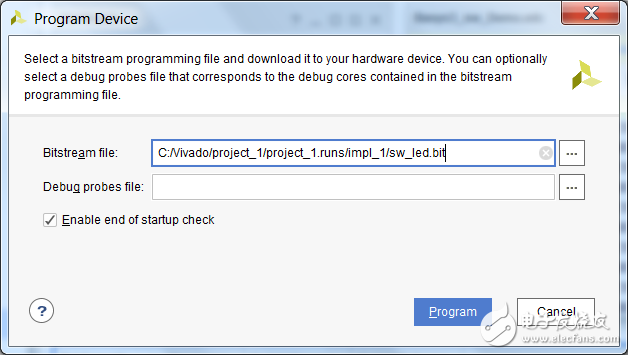

3.2 单击顶部绿色条中的‘Program device’或者‘Open Hardware Manager’中的相同选项。选择之前生成.bit文件路径,单击‘Program’。

当Basys3 FPGA开发板右上角的DONE LED灯亮起时表示下载完成。在这个设计样例中我们可以通过使用Basys3下方的拨码开关来控制对应的LED灯。

4. 通过USB闪存设备下载/配置Basys3

需要注意的是,通过USB设备下载/配置Basys3只支持FAT32格式。而且USB设备必须是空白的,不能有其他文件或文件夹。我们可以通过以下步骤使用USB设备下载.bit文件到Basys3:

4.1 将模式跳线JP1设置成USB模式。

4.2 将U盘格式化成FAT32文件系统。

4.3 复制.bit文件(路径 C:/Vivado/project_1/project_1.runs/impl_1/sw_led.bit)

4.4 粘贴.bit文件到USB设备的根目录。

(注意:USB设备的根目录中只能有此次需要下载.bit文件)

4.5 从PC安全移除USB设备并插入Basys3的USB接口。

4.6 通过micro-USB端口连接PC为Basys3提供电源。

4.7 打开Basys3电源,Basys3将立即从USB设备中下载.bit文件。

4.8 DONE LED灯亮起表示下载完成,可以进行调试。

5. 通过Quad SPI闪存下载/配置Basys3

Quad SPI闪存是一种非易失性的存储介质,Basys3 FPGA芯片在每次启动(上电)时都会读取里面的内容。这就意味着Basys3只要通电就会自己从Quad SPI闪存中下载/配置,配置的速度非常快,适用于已经完成的设计项目的最终展示或演示使用。Quad SPI闪存支持重复烧写,下一次烧写会擦除上一次烧写的内容。通过Quad SPI闪存下载/配置Basys3仅支持.bin文件或.mcs文件,具体步骤如下:

5.1 将模式跳线JP1设置成QSPI模式。

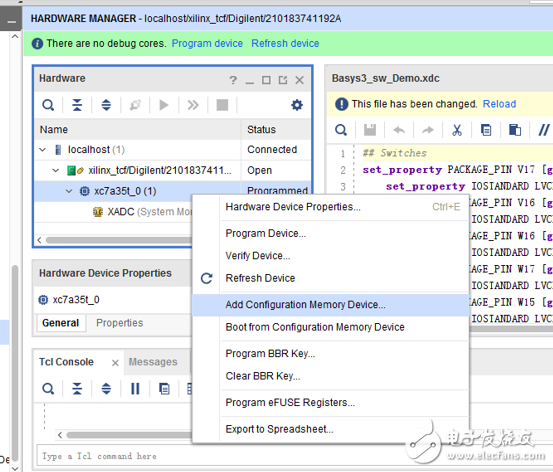

5.2 在Hardware Manager窗口中的Hardware下右键已经连接的设备(xc7a35t_0),选择‘Add Configuration Memory Device…’

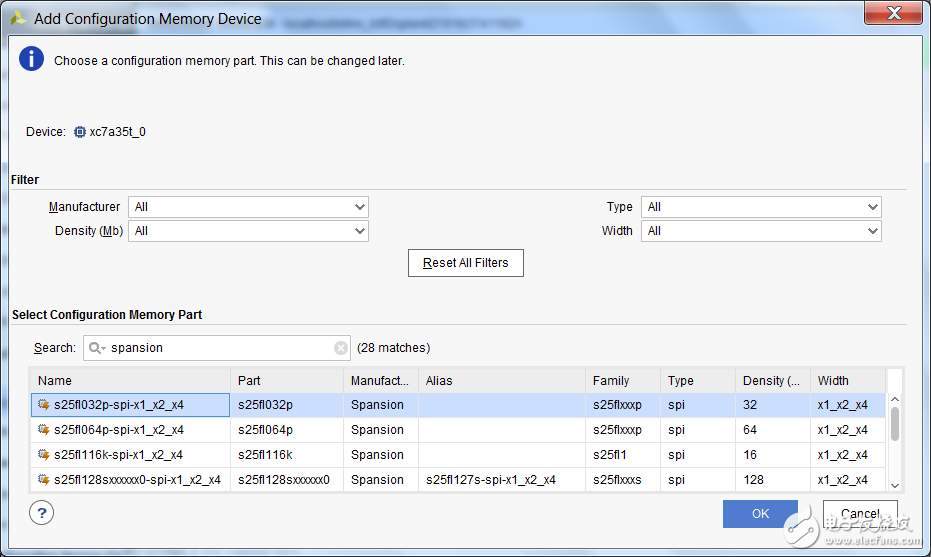

5.3 在弹出的窗口中搜索‘spansion’,选择32位的设备(如下图所示)。单击‘OK’。弹出提示窗是否需要现在下载,单击‘OK’。

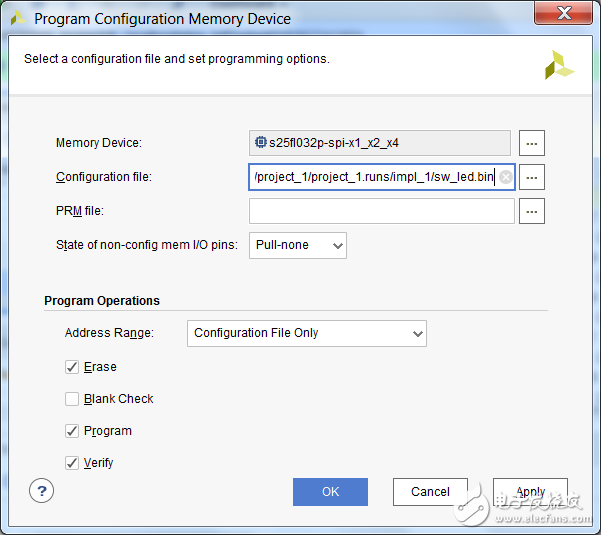

5.4 在Configuration file一栏中添加.bin文件,单击‘OK’。

Vivado会开始擦除上一次烧写在Quad SPI闪存中的配置文件,然后将新的配置文件(.bin文件)烧写到闪存中,之后Basys3开发板只要通电就会自动从闪存中配置开发板。

-

招聘工程项目经理2015-03-27 2077

-

基于FPGA vivado 17.2 Basys3 示波器实验设计2017-12-22 9641

-

stm32如何新建工程项目2019-08-28 2556

-

创建基于HAL库的STM32工程项目2021-08-23 1438

-

如何把libview集成到其他web工程项目?2022-07-18 27884

-

基于 FPGA Vivado 信号发生器设计(附源工程)2023-08-15 996

-

基于 FPGA Vivado 示波器设计(附源工程)2023-08-17 2131

-

防爆工程项目质量现状与对策措施2009-01-06 676

-

CC&CRM产品工程项目管理手册2009-08-04 789

-

基于Vivado 的Basys3开发板的解码教程2016-08-03 1822

-

Basys3开发板的MicroBlaze串口实验2017-02-08 1381

-

工程项目成本/投资控制及管理资源下载2021-06-03 888

-

大型工程项目的可视化需求提高2021-09-09 2473

-

工程项目采集方案的基本框架 隧道监测方案,信号补偿数据采集传输2023-07-03 1106

-

工程项目防雷检测技术应用方案2025-04-14 941

全部0条评论

快来发表一下你的评论吧 !