百度云RSA编译和性能及安全测试

云通信与安全

描述

RSA算法是一种最广为使用的“非对称加密算法”,一般公钥/私钥长度越长,安全性就越好,计算也越复杂。百度云https改造中应用了RSA 2048加解密算法,针对高计算复杂度的RSA解密任务,我们运用FPGA上的并行计算资源和定制化的数据通路,提供了高达45000QPS的解密能力(是CPU单线程吞吐率的75倍以上,媲美商用ASIC加解密卡的吞吐率),同时还将提供独具特色的私钥管理方案,令系统安全性得到了质的提升。

软件调用API执行

编译

执行lspci | grep -i Xilinx,输出非空,证实FPGA已被正确透传给虚拟机。

编译驱动,进入rsa-driver目录,执行make。

如提示“No such file or directory”,请修改Makefile中的KERNELDIR变量,使之指向正确的内核编译目录,一般为/usr/src/kernels/$(uname -r)。

如编译时提示符号重定义,请删除源文件中的PDE_DATA、file_inode、kvalloc、kvfree等符号。

加载驱动,执行insmod fpga_drive.ko。

检查/dev/fpga0的权限是否为0666,如过不是,请执行chmod 666 /dev/fpga0。

在openssl系统engine目录创建到rsa-api/output/so/libfpga_rsa_cpp.so的软链接,即执行ln -s /path/to/rsa-api/so/libfpga_rsa_cpp.so /usr/lib64/openssl/engines/libfpga_rsa_cpp.so。

通过openssl标准engine接口使用RSA加速功能,在正确加载并初始化engine后即可通过RSA_private_encrypt、RSA_private_decrypt进行RSA私钥加解密。

FPGA支持密钥长度在2048 bits以下的RSA私钥加解密。如给定密钥长度超出此范围,engine会转交CPU计算,此时性能等同于直接使用CPU处理。

#include ‹openssl/rsa.h›

#include ‹openssl/engine.h›

#include ‹openssl/err.h›

OpenSSL_add_all_algorithms();

ERR_load_crypto_strings();

ENGINE_load_dynamic();

/* load engine */

ENGINE *engine = ENGINE_by_id("fpga_rsa_cpp");

if (engine == NULL) {

LOG(WARNING) ‹‹ "Could not Load fpga_rsa_cpp Engine!";

return 1;

}

LOG(INFO) ‹‹ "fpga_rsa_cpp Engine successfully loaded";

/* init engine */

int init_ret = ENGINE_init(engine);

int set_ret = ENGINE_set_default_RSA(engine);

LOG(INFO) ‹‹ "engine name = " ‹‹ ENGINE_get_name(engine);

LOG(INFO) ‹‹ "init_ret = " ‹‹ init_ret;

LOG(INFO) ‹‹ "set_ret = " ‹‹ set_ret;

if ((init_ret != 1) || (set_ret != 1)) {

LOG(WARNING) ‹‹ "Failed to init engine";

return 1;

}

/* use engine */

RSA_private_decrypt(flen, from, to, rsa, padding);

性能测试

qps

执行openssl speed rsa2048 -engine fpga_rsa_cpp -multi 36,在"sign/s"一栏中可以看到qps。正常情况应在40000/s以上。

latency

执行openssl speed rsa2048 -engine fpga_rsa_cpp -multi 1,在"sign"一栏中可以看到latency。正常情况应在700us左右。

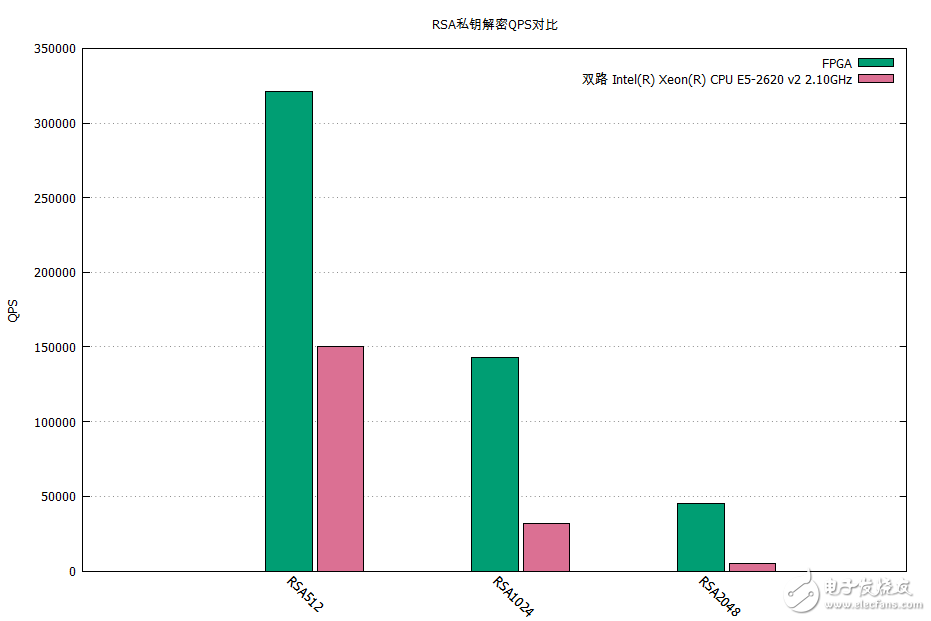

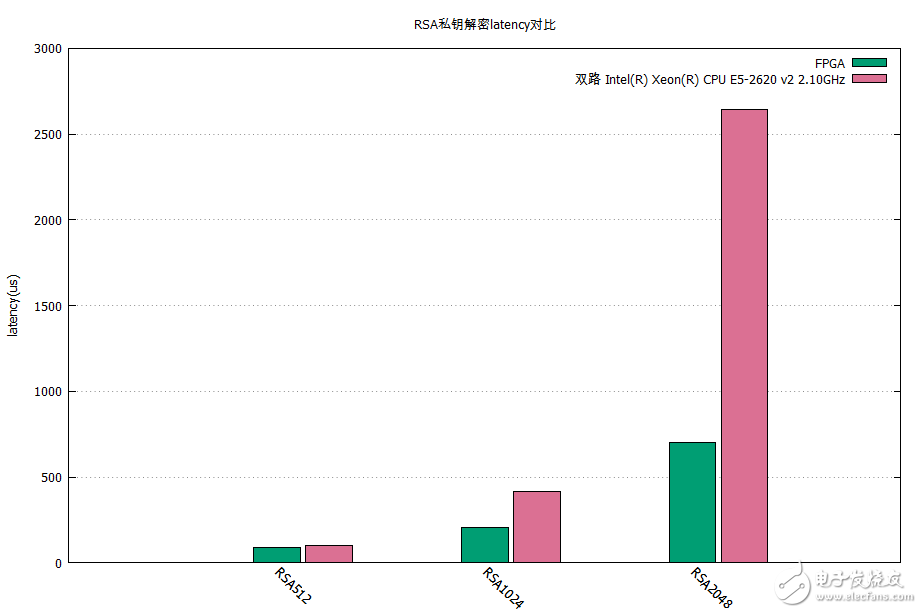

RSA私钥解密QPS对比

FPGA解决方案与使用双路Intel Xeon E5-2620 v2服务器(超线程开启,共24核)进行纯CPU计算相比,性能优势十分明显,如下图所示。当RSA密钥长度为512 bits、1024 bits和2048 bits时,前者的私钥解密QPS分别是后者的2.13、4.52和9.36倍,latency仅为后者的89%、50%和27%。

-

百度云和百度开放云是什么关系?愚人节不能不说的秘密。2016-03-29 4163

-

机械,求ADMAS软件的百度云盘资料,有的兄弟快快分享下,谢谢2017-02-28 4123

-

百度智能云有什么计划?2019-09-11 3709

-

百度云服务器怎么使用nfs ,tftp2020-04-24 2800

-

百度“天智平台”发布 开放百度大脑能力2016-12-01 1118

-

百度云网盘下载入口2018-06-29 2623

-

百度正式推出百度云ABC 3.0,与各行业结合实现产业变革2018-09-05 5567

-

百度进军全球云存储市场胜算如何2019-08-19 687

-

新基建时代 百度如何加速百度智能云发展2020-11-11 2477

-

百度云手机产品用户数已突破300万2020-11-30 4239

-

百度王海峰:自研云端AI通用芯片百度昆仑1已实现量产2020-12-18 3380

-

对于openEuler的发展,百度智能云还有什么样的期待?2021-06-16 2860

-

2022百度世界大会—百度AI助力电力安全流淌2022-07-21 891

-

国产ChatGPT=百度智能云+文心一言?“文心一言”将通过百度智能云对外服务2023-02-18 3148

-

GTC 2023:百度智能云DPU落地实践2023-03-24 4649

全部0条评论

快来发表一下你的评论吧 !