7系列FPGA GTX/GTH 收发器用户指南说明

FPGA/ASIC技术

211人已加入

描述

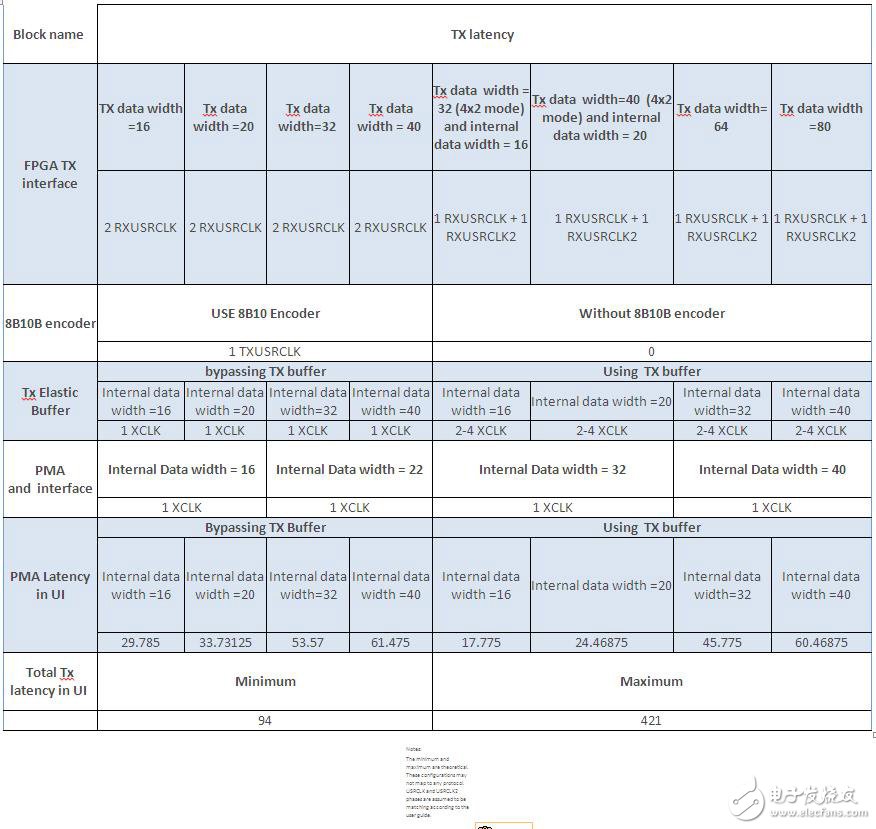

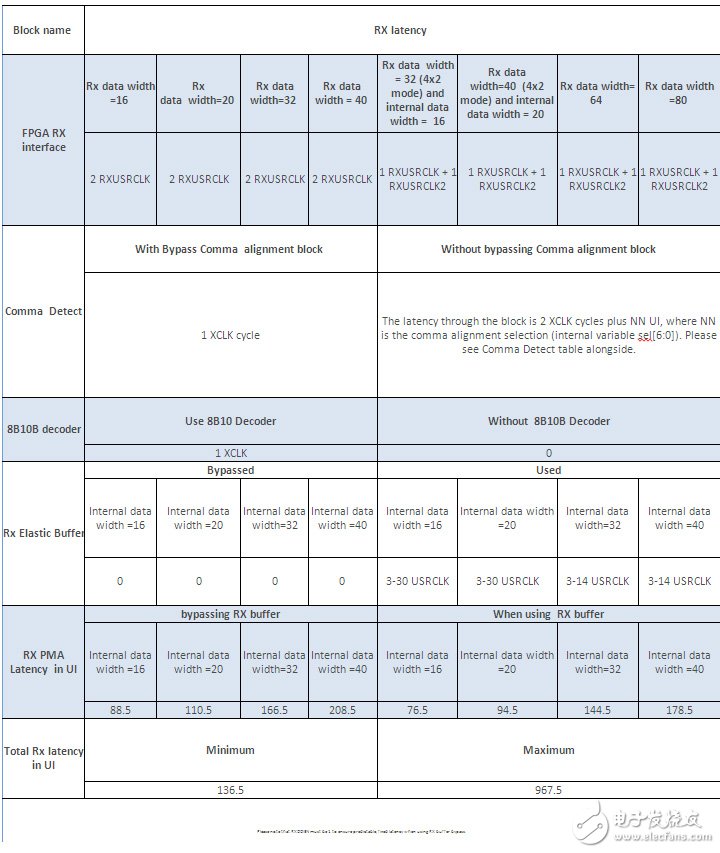

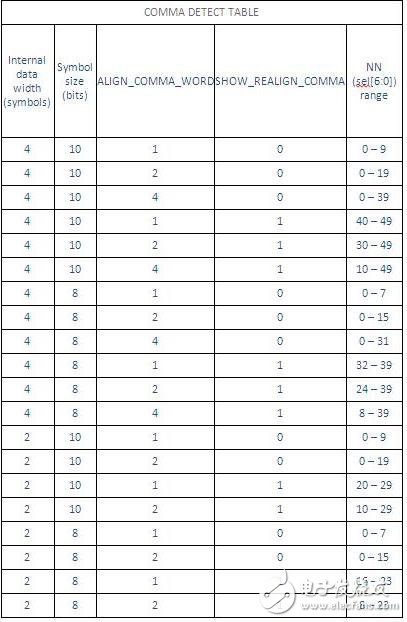

本文提供用于 7 系列 FPGA GTX 收发器的 TX 和 RX 时延值。这些表将被添加到 7 系列 FPGA GTX/GTH 收发器用户指南 (UG476)。

注:

1. 最低和最高为理论值。这些配置可能不会映射到任何协议。USRCLK 和 USRCLK2 相位假定为根据用户指南匹配。

2. TX 时延表上有打字错误。时延体现为 RXUSRCLK 周期,但应该是 TXUSRCLK。

注意:请注意,RXDDIEN 必须为 1,这才能确保使用 RX 缓冲旁通时有可预见的固定时延。

注 1: 通过 TX 架构接口的时延会取决于时延的精确定义。如果时延定义为从把数据放在 TXDATA 上的时钟边缘到离开Fabric接口(PCS 内部)数据第一部分计时的时钟边缘,那么上表中的项目就是准确的,忽略从Fabric到 GT 的时钟插入时间。

注 2: 离开复位时,通过弹性缓冲的时延为:

2 RXUSRCLK cycles

+ CLK_COR_MIN_LAT byte times

+/- 0.5 RXUSRCLK cycles

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- F

-

FPGA设计之GTP、GTX、GTH以及GTZ四种串行高速收发器2020-11-20 21681

-

怎么为VC709板生成GTH收发器2019-03-11 1410

-

7系列设备中的GTX收发器如何获得最佳功耗?2020-07-19 1799

-

介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题2021-11-11 2156

-

Virtex-7 GTH 收发器对决 Altera Stratix V GX 收发器2018-06-06 4528

-

比较 Xilinx® Virtex®-7FPGA GTH收发器和Altera Stratix V GX收发器的均衡能力2018-05-23 4992

-

Xilinx 7系列GTH收发器运行演示2019-01-03 4901

-

virtex-6 FPGA GTH收发器的用户指南资料免费下载2019-02-20 1177

-

UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法2020-11-04 9559

-

GTX/GTH收发器时钟架构应用介绍2021-03-29 8323

-

Xilinx 7系列FPGA收发器架构之硬件设计指导(一)2021-11-06 1194

-

Xilinx FPGA平台GTX简易使用教程(一)2022-03-01 6324

-

GTX/GTH/GTY/GTP/GTZ/GTM有什么区别2022-08-02 10506

-

UltraScale架构GTH收发器用户指南2023-09-15 655

全部0条评论

快来发表一下你的评论吧 !