555芯片设计占空比可调的方波信号发生器

IC应用电路图

描述

1、555电路的工作原理

(1)555芯片引脚介绍

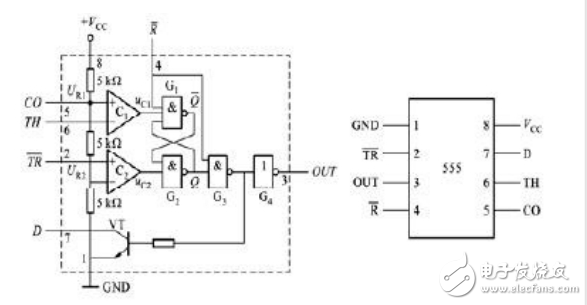

图1 555电路芯片结构和引脚图

555定时器是一种应用极为广泛的中规模集成电路,该电路使用灵活、方便,只需外接少量的阻容原件就可以构成单稳、多谐和施密特触发器。因而广泛用于信号的产生、变换、控制和检测。

1脚:外接电源负极或接地(GND)。

2脚:TR触发输入。

3脚:输出端(OUT或Vo)。

4脚:RD复位端,移步清零且低电平有效,当接低电平时,不管TR、TH输入什么,电路总是输出“0”。要想使电路正常工作,则4脚应与电源相连。

5脚:控制电压端CO(或VC)。若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。

6脚:TH高触发端(阈值输入)。

7脚:放电端。

8脚:外接电源VCC(VDD)。

(2)555功能介绍

555定时器的功能主要是由两个比较器C1和C2的工作状况决定的。由图1可知,当V6》VA、V2》VB时,比较器C1的输出VC1=0、比较器C2的输出VC2=1,基本RS触发器被置0,TD导通,同时VO为低电平。

当V6《VA、V2》VB时,VC1=1、VC2=1,触发器的状态保持不变,因而TD和输出的状态也维持不变。

当V6《VA、V2《VB时,VC1=1、VC2=0,故触发器被置1,VO为高电平,同时TD截止。

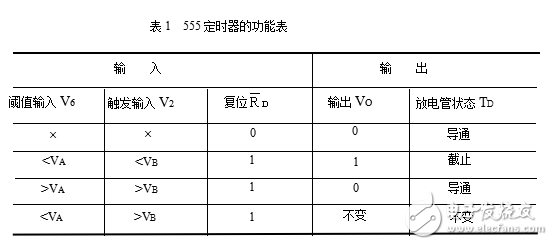

这样我们就得到了表1 555定时器的功能表。

2、占空比可调的方波信号发生器

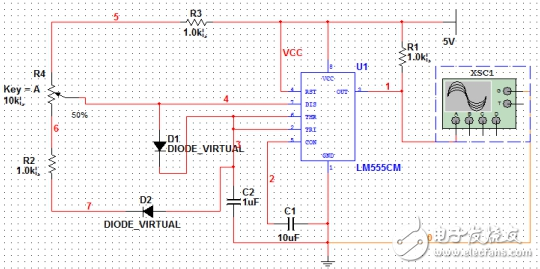

(1)占空比可调的方波信号发生器电路图

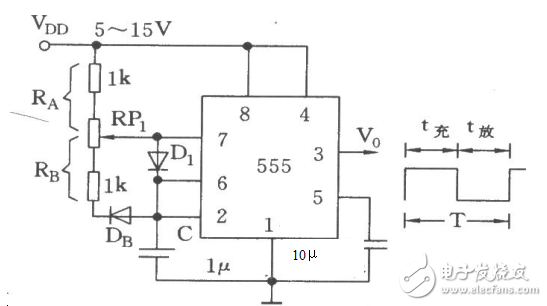

图2 利用555定时器设计方波电路原理图

(2)占空比可调的方波信号发生器分析

3、实验数据

(1)仿真电路图

图3 Multisim电路图

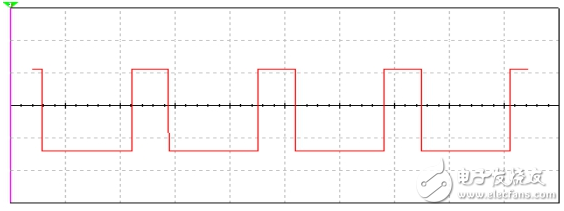

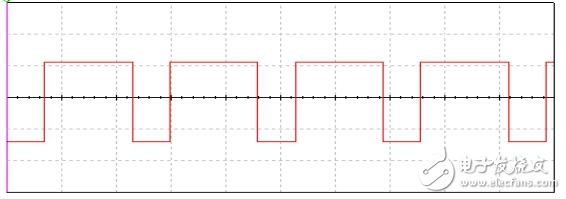

(2)仿真电路结果

图4 占空比为50%的方波波形

图5 占空比小于50%的方波波形

图6 占空比大于50%的方波波形

-

10428

2017-12-05

0 回复 举报学习了,找了很久才找到这个资料 收起回复

10428

2017-12-05

0 回复 举报学习了,找了很久才找到这个资料 收起回复

-

信号发生器输出方波的占空比调整技巧2025-04-02 1920

-

基于555电路的频率发生器2024-11-12 2804

-

proteus信号发生器怎么设置方波2024-02-23 17138

-

信号发生器的占空比是什么 信号发生器占空比怎么设置2023-12-21 6245

-

使用555定时器设计的函数信号发生器2022-03-31 2333

-

频率占空比可调方波发生器电路图2021-08-09 2430

-

信号发生器PWM方波输出 占空比频率可调节2020-11-02 16987

-

占空比可调方波发生器电路及其原理分析2017-11-21 71850

-

555可调PWM发生器2016-06-07 1871

-

NE555构成的占空比可调的方波产生器电路2016-01-20 5047

-

时基集成电路组成可调占空比的方波信号发生器电路图2010-09-28 2227

-

相位和占空比可控的方波发生器2009-07-17 1185

-

频率可调的方波信号发生器设计及电路2009-05-31 15412

-

占空比和频率独立可调脉冲发生器2009-04-20 2966

全部0条评论

快来发表一下你的评论吧 !