采用多相位插值算法实现视频图像缩放及其在FPGA硬件平台的验证

视频技术

描述

摘要:传统的插值算法在视频图像缩放尤其是输出高分辨率的视频图像时,对细节方面的处理性能较差。采用多相位插值算法实现视频图像缩放,主要阐述算法的原理及算法实现的硬件结构。其中硬件电路控制部分使用Xilinx公司的Spartan6系列FPGA芯片,系统可以实现将四路摄像头采集的视频信号从任意通道放大到1 920x1 080@60 Hz的分辨率显示,结果表明输出视频图像的实时性和细节保持良好。

0引言

视频图像缩放又可以称为视频图像分辨率的转换、视频图像的重采样、视频图像的尺度变换等,是数字视频图像处理技术中的关键技术之一,直接影响着视频图像输出质量效果和视觉体验。目前视频图像缩放技术广泛应用于医学图像、工程学、多媒体、视频会议等领域[1]。

传统的视频图像缩放插值算法有最近邻插值、双线性插值、双立方插值等,其他的插值算法还有边缘插值、B样条插值、自适应插值等,其中基于线性模型的算法在应用于图像处理时高频信号会叠加到低频信号区域,导致输出视频图像出现混叠情况,尤其是视频图像输出分辨率要求较高时细节方面的处理会带来较差的视觉体验效果。多相位插值算法也是一种常用的视频图像缩放方法,其相对于传统的插值算法而言,在细节保持上具有较好的性能,也被广泛用于工业界。

1算法原理

视频图像缩放的基本原理是将分辨率为(M,N)的原图像转换成分辨率为(X,Y)的目标图像。用数学定义可以描述为:已知(M,N)个像素点,Pixelin(i,j)(i=1,2,…,M;j=1,2,…,N),其中i,j为原图像的像素点坐标,Pixelin(i,j)为原图像像素值。现在希望通过一个数学关系式的映射,利用已知像素点求得输出像素点,Pixelout(x,y)(x=1,2,…,X; y=1,2,…,Y),其中x,y为目标图像的像素点坐标,Pixelout(x,y)为目标图像像素值。那么输入输出图像的像素值对应函数关系可以表示为:Pixelout(x,y)=f(i,j, Pixelin(i,j)),多相位插值的本质就是根据函数的映射关系求解目标图像的像素值。

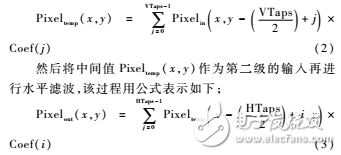

根据上述分析知,目标图像像素值并不能直接从原图像获取,而是需要通过原图像相关的位置坐标、像素值等信息计算得出。由于图像内容的局部相关性,输出目标图像的像素值和相应空间位置邻近的输入原图像像素值相关性较大,与空间位置较远的像素值相关性较小。一般的视频图像缩放处理是典型的二维滤波的过程,可以用公式表示[4]如下:

Pixelout(x,y)=

∑HTaps-1i=0∑VTaps-1j=0Pixelinx-HTaps2+i,y-VTaps2+j×

Coef(i,j)(1)

式中HTaps和VTaps为两个二维滤波器在水平和垂直方向上的抽头数,Coef(i,j)为对应滤波器的系数,这个系数代表了参与运算的输入像素值对输出像素值的权值大小。它的值确定了相应位置输入像素值对输出像素值的影响并直接决定缩放的效果,系数的确定取决于滤波器低通和抗混叠等需求。

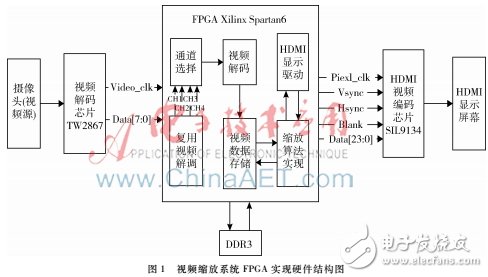

图1视频缩放系统FPGA实现硬件结构图二维结构在数据运算时比较复杂,为了简化运算一般将二维滤波器进行拆分,使用两个一维滤波器级联来实现二维特性,即水平滤波器和垂直滤波器。首先第一级进行垂直滤波输出中间值Pixeltemp(x,y),该过程用公式表示如下:

通过以上分析可知,简化运算前后需要的乘法器个数从(VTaps×HTaps)减少为(VTaps+HTaps)个,运算量大大降低,这种方式非常有利于实现实时性要求较高的硬件系统。同时这个思路也是各种视频图像缩放算法硬件实现的基本模型,即在水平方向和垂直方向分别进行缩放处理,这样问题就成了一维信号采样率变化的分析处理过程。

2系统硬件结构

系统硬件结构如图1所示,使用Xilinx公司的Spartan6系列FPGA芯片对多相位插值缩放算法进行验证。系统采用四路模拟摄像头采集视频信号作为输入源,通过TW2867多路视频解码芯片将模拟视频信号转化成数字视频信号送给FPGA芯片进行数据处理,FPGA首先对输入的数据信号进行一定的预处理,由于采集的图像与输出显示的图像刷新率不一致,为了保证数据处理时读写速率的匹配,需要将图像数据写入DDR3然后读取数据进行缩放处理再输出,输出的信号需要符合HDMI标准时序,最后通过SIL9134视频编码芯片将输出数据信号编码成视频流传输到屏幕显示并查看输出的效果。

2.1相关芯片介绍

2.1.1视频解码芯片

TW2867是Techwell半导体公司生产的一款芯片,主要功能是将模拟的复合视频信号转换成数字视频信号,便于进行显示、存储和传输等数字化视频信息处理。芯片包括视频解码器和音频编码器,其中视频解码器每个通道包含有数字化输入模拟视频信号的ADC(模数转换器)。TW2867芯片I2C信号线引脚与STM32芯片I2C信号线引脚连接,TW2867芯片寄存器的参数通过STM32芯片进行配置。

2.1.2视频编码芯片

SIL9134是SILicon Image半导体公司生产的一款芯片,支持HDMI1.3接口规范,可以将符合时序标准的数据信号编码成HDMI视频流。它还能传输高清晰度的音频和视频信号,最高支持1 080P@60 Hz分辨率的视频输出。SIL9134芯片I2C信号线引脚与STM32芯片I2C信号线引脚连接,SIL9134芯片寄存器的参数通过STM32芯片进行配置。

2.2主要模块介绍

根据上述系统硬件结构的介绍,FPGA输入部分是摄像头采集的模拟视频源,它是四路复用的BT656格式视频信号,分辨率为720×576@25 Hz。输出部分视频分辨率为1 920×1 080@60 Hz,视频信号的格式是HDMI。在处理过程中由于视频数据的格式存在变化,首先要将复用的四路视频信号进行解调,然后选择任意一路视频信号进行解码;解码后的视频信号写入数据存储模块,然后读取视频信号进行缩放处理,最后将处理完的数据与相应分辨率的时序信号进行整合输出。

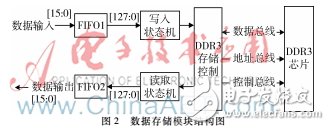

2.2.1视频数据存储模块

视频数据存储模块的实现思路如图2所示。输入数据位宽是16位,如果往DDR3写入的数据也是16位,则效率太低,而DDR3的接口是最高支持128位的双向端口,因此选择最大位宽以提高数据处理速度,这里需要使用FIFO来进行速率转换。视频数据的处理是以帧为单位的,每帧的处理又是以行为单位的,对每行数据处理时采用乒乓处理方式,当FIFO的数据达到半行时就开始将输入数据写入DDR3同时继续接收剩余半行的输入数据。其中DDR3存储地址也是按照上述思路来计算的。

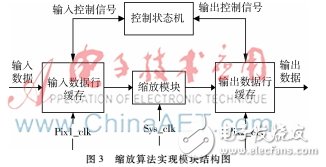

2.2.2缩放算法实现模块

缩放算法实现模块的结构图如图3所示。视频数据按照自左向右、自上而下逐行逐像素的扫描顺序进行显示,在缩放计算时也是依据此顺序进行。先将进入到缩放模块的数据进行输入缓存,经过缩放处理后再对数据进行输出缓存,然后根据特定的时序从缓存区域读取数据输出。一般而言输入和输出的数据时钟及缩放模块的时钟是不一致的,前者的时钟由输入输出视频的分辨率决定,后者采用单独的时钟以适应不同采样率变换的缩放要求。

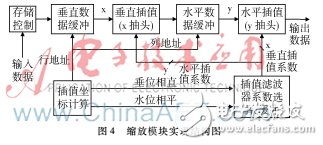

图4缩放模块实现结构图如图3所示,数据缓存的实现是利用双口RAM异步存储机制,不同模块之间的数据调用、参数计算、模式选择和输出格式等都是通过状态机进行控制的。其中缩放模块的实现思路如图4所示。基于前文的理论分析,将二维图像的插值简化成一维的水平插值和垂直插值方式处理。硬件实现时滤波器的抽头数越多输出图像的性能越好,同时消耗的资源也越多。实际运算时垂直方向需要预先缓存多行数据,这样带来的运算量必然会非常大,如果垂直方向滤波器抽头数太多就会造成数据存储的压力而增加硬件实现的成本,因此设计时垂直方向使用更少的滤波器抽头数,减少系统的行缓存数量[5]。综合对性能和资源的考虑,根据行缓存最少需求,采用固定垂直滤波器5Taps和水平滤波器7Taps电路结构。

2.2.3乘法器的流水线实现

算法实现过程中运算量和资源开销主要集中在乘法器,因此为了提升电路性能就要对乘法器进行转化。通过对乘法运算原理的分析,采用加法器和选择器代替乘法器实现乘法运算[6],并且使用流水线结构提高数据处理速度。

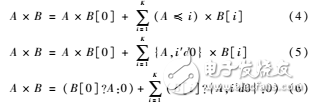

例如两个K位数据A、B的乘法运算转化过程如式(4)~(6)所示,通过硬件语言描述时可用选择器和加法器表示。

为了使每位数据运算时序对齐添加D触发器实现流水线结构,这里的流水线级数不宜太多,否则功耗会加大。本文处理的数据是RGB格式,三通道数据分离同时运算再合并,主要采用K=8的电路形式。

3实验结果

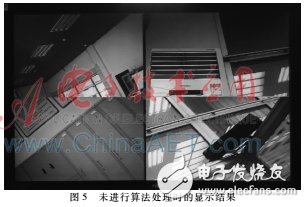

系统在没有进行算法处理时,直接将四个通道采集的视频数据缩小同时输出到同一显示器屏幕,如图5所示。系统进行算法处理时,可以将任意通道采集的视频数据放大后输出在显示器屏幕,分辨率信息为1 920x1 080@60 Hz。如图6所示,默认放大显示第一通道采集的视频,通过按键实时切换任意通道采集的视频。

4 结论

本文采用多相位插值算法实现视频图像的缩放,并且在FPGA硬件平台验证,放大后的视频图像信息过渡平缓,细节保持良好,切换放大任意通道视频图像信号显示迅速,采集的视频图像信息内容变化显示同步实时变化。多相位插值算法对放大后视频图像内容信息保持较好,但对边缘部分未能做较好的处理,虽然这没有带来什么影响,但为了进一步提升放大后视频图像的性能,在今后的研究中可以考虑融合多种性能良好且互补的插值算法,比如融合多相位插值和边缘插值两种算法,这样缩放后输出的视频图像性能保持会更加优异。

-

如何使用FPGA实现图像缩放算法的研究设计2021-04-02 1727

-

如何使用FPGA实现数字X线图像的实时缩放模块2021-03-18 986

-

如何使用FPGA实现高分辨实时监控图像缩放的设计2021-02-05 1015

-

使用FPGA实现视频图像缩放显示的设计论文说明2021-01-25 1019

-

如何利用FPGA硬件实现固定倍率的图像缩放?2018-08-18 5140

-

实时图像插值算法2018-01-17 490

-

改进的红外图像增强算法及其在FPGA上的实现2017-12-22 1014

-

一种新颖的图像缩放算法进行FPGA硬件实现2017-12-12 1144

-

基于FPGA的视频图像缩放与叠加融合技术的设计方案及实现2017-11-22 5562

-

基于双线性插值原理实现图像缩放算法2017-11-07 1150

-

基于双线性插值的图像缩放在GPU上的实现2017-01-08 924

-

FPGA实现的视频图像缩放显示2016-08-29 686

-

图像处理中的插值和缩放研究2011-09-28 540

全部0条评论

快来发表一下你的评论吧 !