三种使用PCI Express IP的节能技术

FPGA/ASIC技术

描述

摘要

将PCI Express用于计算应用(服务器、组网、笔记本电脑等)的连通性方面在一段时间内相当流行,同时,在较小的、电池动力装置(电话、平板电脑、手表等)内的使用正变得更加广泛。由于计算应用环境下设备之间数据通信量的增加,产生较大的功率要求,正是由于该原因,设计人员致力于寻找降低其SOC在低强度或空闲时期功率的方法。较小的、电池动力装置常处于空闲和深度睡眠模式,但对于这类深度节电模式,其代价是,切换回正常工作模式时恢复时间较长。

对于使用PCI Express的设计人员,通过将PCI Express IP集成在其SOC中,对其目标应用的功率产生了积极的影响,这是因为除了协议所提供的节能技术之外,还有高级功率管理技术可以控制功耗。采用时钟门控技术可以处理动态功耗事宜,但对静态功耗无任何作用。电源门控技术是实现最大程度节能的理想选择,这是因为它能降低因缩小的特征尺寸而导致更大的静态功耗。在深度节电模式下,电源门控PCI Express IP在典型情况下需要PCI Express链路再训练或再配置,并将延长恢复时间,这在很多情形下是不希望的,所以是一项重大挑战。

在本文中,以PCI Express IP为例,介绍了三种节能技术,以及设计人员如何使用协议和设计工具的功率管理特性来为需要快速恢复的装置提供高能效SoC的方法。

1. 时钟门控技术:综合工具

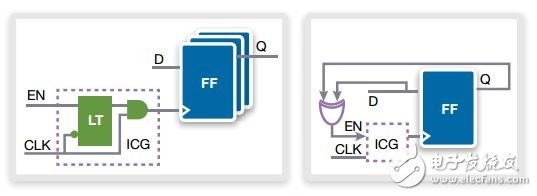

现代综合工具提供了数种时钟功率管理技术,如传统的时钟门控和自门控。在传统时钟门控方面,综合工具寻找条件,将其组合在一起以形成时钟使能(EN),这样可以关断时钟到触发器的通路。这里介绍集成式时钟门控(ICG)单元,使用EN,对系列触发器的时钟进行关断,如图1所示。对于自门控技术,如果触发器的输入不变,将关断触发器时钟;触发器的的输出与输入异或,用作ICG中的时钟使能(EN)。

图1. 传统的时钟门控(左)与自门控(右)

本策略导致了高能效CE,但由于额外的逻辑开销,面积略有增大。综合工具通常在插入传统时钟门后使用自门控,以增强CE,针对面积权衡,进一步降低能耗。使用功率分析工具,可对该自动方法进行评估和优化,它能通报已有时钟门的效率,并揭示进一步插入时钟门的机会。对于数种使用情形,这类报告可用于进一步优化时钟门插入。

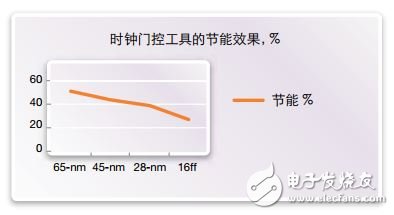

优化的传统时钟门控和PCI Express IP能实现至少40%的节能效果,并会将28纳米技术节点上的面积降低约9%。

传统时钟门插入之后的自门控策略能够降低至少5%的能耗,并会使面积增大约1%。在16纳米FinFET (16FF)技术节点上,综合工具时钟门控(传统时钟门控+自门控)能达到25%的节能效果。图2。

图2. 时钟门控工具的节能效果

2. 时钟门控技术: PCI Express IP

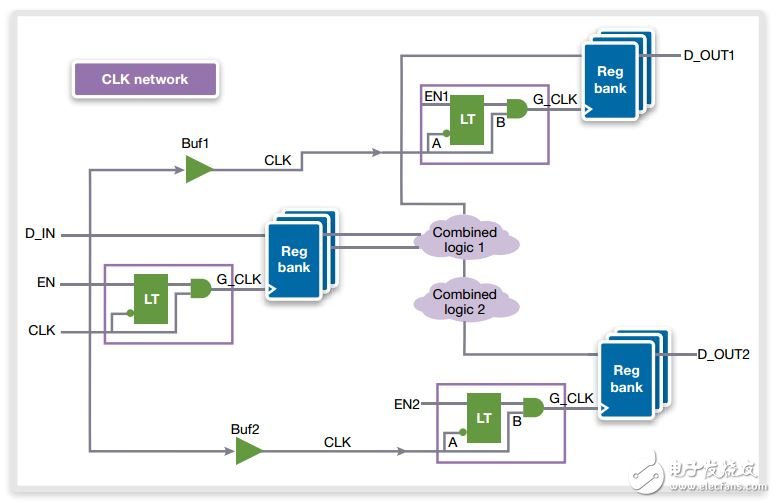

虽然工具插入式时钟节能技术能够显著降低功耗,它们并未完全考虑设计层次。从设计方面获取的CE仅作用于触发器上,仅在每一触发器的时钟输入处选通时钟,如图3所示。存在这方面的抱怨,工具插入式时钟门控过于“细微”,未考虑穿过整个层次的时钟树。

时钟树包括分布在整个设计中的时钟驱动和时钟门控单元,切换与驱动逻辑无关。对于高度复杂的设计,时钟树会消耗至少25%的待机功耗。在层次结构的根部关断时钟,可降低功耗,原因在于时钟树切换,这是一种需要考虑到架构的设计决定。

图3. 时钟脉冲门插入后的典型设计

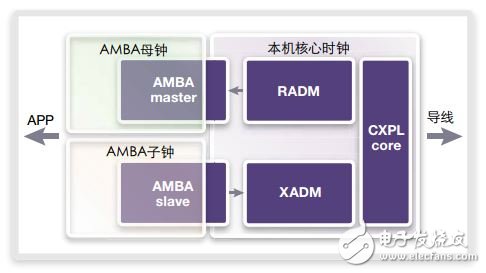

作为示例,考虑PCI Express IP设计和ARM® AMBA®接口以及3个时钟域,如图4所示。AMBA主设备接收PCI Express请求,并将其转换为AMBA事务,所述事务将被发送至AMBA主时钟上的应用层。AMBA从设备处理从应用层传出的AMBA事务,在AMBA从时钟上将其转换为PCI Express请求。剩余块执行具体的PCI Express功能,对在核时钟或参考时钟线上的往返请求进行处理。

图4. PCI Express IP和3个时钟域

存在多种具有AMBA主/从空闲的场景,完全独立于PCI Express链路状态:

1. 对于从线路来的入站请求,需要本地核时钟域和AMBA主时钟域,以保持运行,同时关断AMBA从时钟。

2. 对于来自应用层的出站请求,需要AMBA从时钟和本地核时钟域保持运行,同时关断AMBA主时钟。

3. 对于不需要应用逻辑干预的入站/出站请求,仅需要本地核时钟域,与此同时,可关断AMBA主和从时钟。

结构模块中的时钟门控不需要遵守PCI Express的链路功率管理状态。如果在特定方向上没有未决请求,可断开待机结构模块的时钟。在AMBA主从时钟块中,可在根部关断时钟,从而降低特定时钟树消耗的功率。对于情形3,在PCI Express IP中实施相同方案能够节省至少10%的功率,并将待机处理效率提高至少10%。

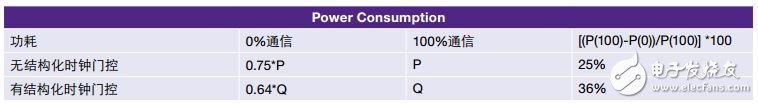

在表1中,介绍了满负荷通信和待机状态下的功耗,采用和未采用结构化时钟门控实施。

表1. 关于结构化时钟门控实施的功耗比较

3. 时钟门控和电源门控技术:PCI Express协议

PCI Express协议允许实施功率优化,其方式是通过更精细的链路状态实现,L0、L1(子状态)和L2/L3,根据规范将其定义为功率管理状态。要想退出L2和L3状态,需恢复电源并再次对链路进行训练,从而导致更长的恢复时间。在L0和L1(子状态)下,采用时钟门控技术以便将恢复时间降至最低。考虑在章节2中介绍的PCI Express IP设计,在L0下,可选通AMBA主从时钟,具体情况取决于L0下的路径方向,而在L1子状态下不需要参考时钟。因此,即使在不停止锁相环(PLL)的情况下也能断开本地核心时钟,PLL可生成核心时钟以避免重启PLL时的延迟。该情形下的功耗是所有时钟门控技术中最低的,仅在数字和模拟电路中存在泄漏功率。

如果能够容忍高至5倍的恢复时间,就能在L1.1子状态下断开PLL和发送器/接收器,与仅具有时钟门控的L1.1子状态相比,可实现高至97.5%的节能效果。如果能够容忍高至15倍的恢复时间,在L1.2子状态下甚至能断开共模电压,将功耗降至0.05%。

PCI Express提供了基于消息的系统功率处理协助技术,如延迟容许通报(LTR)和优化缓冲清除/填满(OBFF)。使用LTR,能够将下游装置容许的最大延迟传递到上游,使得主机软件能够了解无缝链路操作所需的恢复时间。使用OBFF,主机软件能够将系统状态传输至具有主线总控能力的下游装置,使用它们来优化传输排程,并使系统在节能模式下工作的时间更长。例如,如果系统处于低功率状态,例行DMA传输会出现延迟。对于从LTR收集的信息,它能用于决定将待机时间延长多少,以便允许更高的貌似可行的节能。

结论

在具有预期快速恢复时间的零散通信和待机过程中,功率管理对于装置尤为重要。采用基于工具的设计相关和协议相关时钟门控技术,对于诸如PCI Express的接口IP设计,可实现最大节能。当需要近乎为零的恢复时间时,时钟门控解决方案可达到优异的结果。通过避免PCI Express链路再训练和再配置,可实现最大节能和更快的恢复时间。

对于Synopsys针对PCI Express技术的DesignWare IP解决方案,它利用了基于工具的时钟门插入技术的优点。

包括依赖并独立于PCI Express链路功率状态的结构化时钟门控块;

支持L1子状态下的PCI Express时钟功率管理;

提供电源门控解决方案,以及针对L1.2子状态的功率岛和寄存器保持方法(避免链路再训练),支持功率管理协助特性,如延迟容许通报(LTR)和优化缓冲清除/填满(OBFF)。

支持所有的PCI Express功率管理功能,包含更长的恢复时间,如动态上下链路配置和L2/L3功率门控。

使用支持这些特性的PCI Express IP,可帮助设计人员提供高能效SoC。

https://www.synopsys.com/Company/Publications/DWTB/Pages/dwtb-L1-substat...

-

IP_数据表(I-22):Configurable PCI Express 4.0 Link Controller2023-03-15 494

-

PCI Express的IP编译器用户指南2022-09-29 581

-

设计的带嵌入式收发器的Gen1×1硬核IP的 PCI Express IP编译器2021-07-30 1093

-

PCI Express接口标准的特点及在FPGA中的应用2021-06-18 3951

-

如何去设计一种PCI Express接口?2021-05-21 1712

-

PCI Express标准技术性概述2019-05-10 1469

-

PCI Express IP设计的过程与仿真介绍2018-11-28 3278

-

PCI Express系统中DMA的基本功能介绍2018-11-22 5917

-

PCI Express IP核应用参考设计2016-06-07 852

-

PCI-Express技术2015-11-13 818

-

什么是PCI Express接口2009-12-25 3048

-

PCI Express总线技术白皮书2009-10-04 1486

-

PCI Express插槽,什么是PCI Express插槽2009-04-26 5593

-

pci express总线概念2006-12-25 2325

全部0条评论

快来发表一下你的评论吧 !