FAST:基于FPGA的SDN交换机开源项目(二)

FPGA/ASIC技术

描述

FAST的目标是面向SDN的教学与科研,基于开源方式开发出一套以FPGA为核心的SDN交换机实现代码,包括FPGA硬件源码以及交换机中CPU上运行的相关软件源码。

参与SDN科研与教学的研究人员、教师和学生不但能够直接利用这些源码,在FAST支持的FPGA交换平台上生成可运行的SDN交换机,并与通用SDN控制器,如floodligjt,ODL等,互连组建自己的SDN网络;而且能够直接参与到FAST交换机的开发中,编写并提交自己的FPGA功能模块或软件程序,扩充现有FAST交换机的功能。

一、FAST的代码组成

FAST项目代码主要有三个来源。一是2011-2015年期间,国防科大计算机学院研究生参加《路由器原理与设计》实验课中基于NetMagic08平台的课程设计成果;二是2012年以来,国防科大、香港理工大学、北京邮电大学、东南大学、中科院计算所等单位基于NetMagic08和NetMagic Pro平台进行的互联网测量、SDN交换和软件定义的实验床等相关开发成果;三是湖南新实网络科技有限公司基于NetMagic08开发的网络教学案例NetEXP的设计代码。

这些来自多个FPGA交换项目的代码包括FPGA硬件设计代码(Verilog程序),交换机上CPU运行的控制软件代码,以及组成相关demo需要的其他代码(如基于RESTAPI编写的APP代码),详细组成如下表所示。

硬件代码

IPv4/IPv6/LISP协议报文的分析代码;

精确匹配查表算法实现代码;

支持掩码的查表匹配算法(Stride BV算法)实现代码;

静态/动态缓冲区管理代码;

基于令牌桶的流量控制代码;

优先级调度代码;

分组分片和重组代码;

LISP隧道实现代码;

Netmagic访问控制协议(NMAC)硬件实现代码;

可靠传输协议(OpenVAS)硬件实现代码;

软件代码

交换机侧的openflow通道代码;

交换机侧的流表管理代码;

BV算法的规则变换代码;

令牌桶控制器代码;

本地配置界面代码;

计数器显式代码;

虚拟网络接口代码;

NMAC控制端代码;

可靠传输协议(OpenVAS)控制端代码;

实现的典型交换机和网络设备

自学习L2交换机

支持Openflow1.0的SDN交换机

支持openflow1.3的SDN交换机

IPv4路由器

LISP XTR路由器

软件定义隧道交换机(用于软件定义实验床构建)

支持NETEXP网络教学案例的NetLabs平台

虽然目前这些代码只在NetMagic08和NetMagic Pro平台上,但实际上大多数代码都是与平台无关的。因此FAST软硬件架构中都显式区分了平台的相关代码和平台无关的代码,便于SDN交换机的软硬件实现代码的跨平台移植。

二、FAST代码树结构

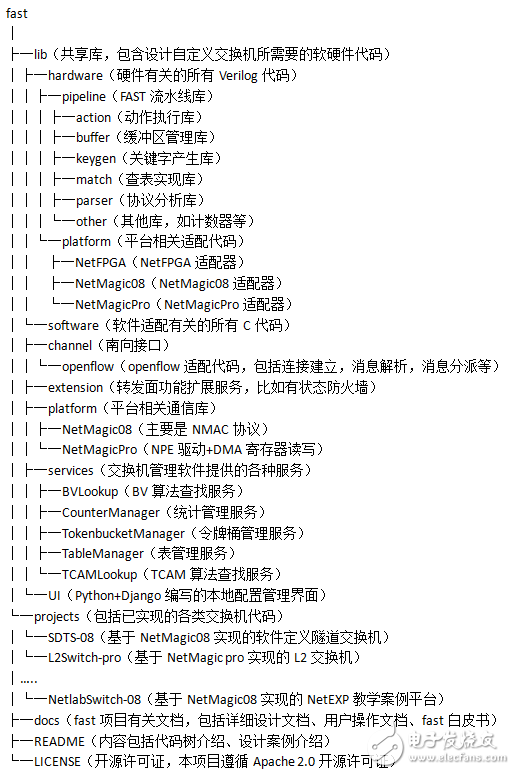

FAST项目在github( https://github.com/FAST-Switch/fast )上的代码树结构如下,在顶级目录中,主要包含lib、Project、docs三个子目录和按照github要求提供的README和LICENSE文件。

Lib目录中包含所有平台相关及与平台无关的软硬件代码,其分类组成如代码树各目录后面的注释所示。所有FPGA设计代码被分为pipeline和platform两类。pipeline是平台无关的代码,对应openflow转发流水线的实现逻辑,包括转发动作action、buffer、keygen、match、parser和other几个目录,分别放入相应额代码。例如Stride BV算法实现放在match目录中,IPv6协议分析放在Parser目录中,令牌桶实现放在action中。平台相关代码包括网络接口分组收发代码,接口CRC校验实现代码,FPGA与CPU通信代码,FPGA访问外围存储器,如DDR、TCAM等的控制器代码等。在NetMagic08和Pro平台中,用户模块(UM)之外的代码都是平台相关代码。

Lib目录中software子目录包含交换机CPU上执行的软件代码,同样分为平台无关代码和平台相关代码。平台无关代码包括openflow控制通道实现代码,表管理代码,算法相关代码,数据平面服务扩展(如实现的有状态防火墙)代码等;平台相关代码包括NetMagic08控制终端Cpu上运行的NMAC协议软件,NetMagic Pro自带Cpu上运行的PCIe驱动软件,多接口虚拟驱动软件等。平台相关软件对上层应用采用相同的API接口,使用虚拟地址空间的思想对软件可访问的硬件资源进行抽象和标识。虚拟地址空间是FAST实现的重要概念,在后续文章中会有详细介绍。

Project中包含了目前实现的各种FPGA交换机的实例,包括L2交换机,软件定义的隧道交换机(用于软件定义实验床构建),各类SDN交换机等。Doc目录包含FAST代码相关的各种文档资料等。

图1 FAST代码结构

需要注意的是,在Project的每个实例目录中,并不包含相关的源代码,而是包含了硬件FPGA的工程配置文件(如altera FPGA平台对应的.qsf文件)和软件编译需要的makefile文件。在这两个文件中,分别通过相对路径包含了本项目实现需要的所有硬件源文件和软件源文件。因此用户通过这两个文件可以索引到本项目所有的源文件,通过FPGA开发环境(如Quartus II)对工程配置文件直接编译和映射即可生成FPGA配置文件,通过编译makefile文件即可获得软件的执行映像。

如何获取和使用github上的FAST代码将在后续的文章中详细介绍。

三、FAST代码的优化与整合

目前FAST已经在github上初步建立了代码树结构,各类FPGA交换机设计代码和文档正在陆续上传。在这些代码和文档上传结束后,还有大量的代码优化与整合工作要做,主要包括两方面。

一方面是代码的清理与测试验证。当前FAST代码主要来自研究生,质量层次不齐,风格五花八门,因此需要删除或重写严重不符合质量要求的代码,同时对代码的功能进行重新测试,发现bug及时进行修复和更新。在初步的代码清理和测试验证后,FAST可基本达到类似于NetFPGA项目的开源效果,即实现代码仓库功能。用户可通过查找相应的project目录,更加方便地获取相应的软硬件设计代码,在自己的FPGA平台上运行和测试,利用github进行bug报告提交,促使源文件的不断完善和更新。

另一方面,与NetFPGA项目不同,FAST希望做到与平台无关,因此需要将软硬件代码分别分成与平台无关和与平台相关的两部分,对不同工程中大量重复的与平台无关的代码,如令牌桶控制代码和转发查表代码等,需要最大程度采用参数传递的方式进行重新实现,以减少相同功能模块实现副本的数量,简化后续版本管理的压力。

希望通过上述工作,能够将当前FAST项目中多套完全独立的代码逐渐发展成为一套功能齐全,质量较高的代码,同时吸引更加广泛的科研人员加入到FAST的开发中,使FAST真正成为支持SDN科研和教学的平台。

-

二层交换机和三层交换机有什么区别2024-08-07 4919

-

SDN交换机如何实现2023-11-10 544

-

全国产交换机、军用交换机与普通交换机到底有啥区别?2023-07-07 3763

-

千兆交换机和百兆交换机应该如何选择?2023-06-18 7466

-

二层交换机和三层交换机的区别2023-06-12 14178

-

网络交换机2023-04-28 1693

-

基于Linux的虚拟交换机Open vSwitch项目2022-06-22 3700

-

接入层交换机、汇聚层交换机和核心层交换机的区别2021-06-04 8057

-

SDN中交换机控制代理拒绝服务攻击方法2021-06-01 1005

-

项目中如何选择交换机?2021-01-12 2114

-

核心交换机、汇聚交换机与普通交换机的区别介绍2020-03-19 14220

-

FAST:基于FPGA的SDN交换机开源项目(一)2017-11-16 5335

-

SDN交换机的设计与实现中交换模式和背板设计等技术的介绍2017-10-31 962

-

二层交换机,三层交换机,四层交换机的区别2009-08-01 2221

全部0条评论

快来发表一下你的评论吧 !