构建 MicroBlaze 系统降低系统的 SWAP-C

FPGA/ASIC技术

描述

在嵌入式系统中,很容易在系统核心找到 FPGA。这是因为 FPGA 能同时并行执行多个功能,并具有确定性的响应。很多嵌入式系统还包含一个处理器,用来处理通信任务、内务管理、调度任务以及通常在软件中执行的其他任务。

这种 FPGA 与处理器的组合会增加系统的 SWAP-C。SWAP-C 是指解决方案的尺寸、重量、功耗和成本。显然,同时使用处理器和 FPGA 不仅会增加材料成本,同时还会增加偶生工程成本(NRE)。此外,设计与验证工作变得更加复杂。两个器件还需要更多板级空间,这会增大解决方案的尺寸和重量。电源结构也比只用一个器件时复杂,这进一步影响 SWAP-C。

尽管难以用软件驱动的处理器来实现通常由 FPGA 执行的功能,但在 FPGA 内部实现处理器,通常能让设计大受裨益。

对于在赛灵思 FPGA 中实现处理器,我们有多个选择:

PicoBlaze– 8 位高确定性微控制器(见赛灵思中国通讯 54 期,“充分发挥 PicoBlaze 微控制器的优势。”)

MicroBlaze– 32 位 RISC(精简指令集计算机)处理器,可针对众多应用在性能和面积方面进行定制。

Zynq UltraScale MPSoC 和 Zynq-7000 SoC将硬化的嵌入式 ARM 处理器和可编程逻辑完美集成在单个芯片上。(如需了解有关 Zynq-7000 SoC 使用方面的信息,敬请查阅MicroZed Chronicles)

本文中,我们将深入了解如何在 FPGA 设计中实现赛灵思 MicroBlaze 处理器以减小 SWAP-C。

什么是 MicroBlaze

MicroBlaze 是 32 位软核处理器。这意味着它是一款可先定制,然后综合,最后布局布线到目标 FPGA 的逻辑资源中的软 IP 核。每个 MicroBlaze 处理器实例都是自定义的,包含 FPU(浮点单元)、MMU(存储器管理单元)以及指令与数据缓存这样的高级特性。

用户可在 MicroBlaze 处理器上运行一系列操作系统,包括 FreeRTOS、Micrium uc/OSiii 和 Linux。用户还可以运行裸机代码。实例的软特性可确保不存在过时问题。简而言之,MicroBlaze 处理器是一款功能非常强大的嵌入式系统开发工具。

创建 MicroBlaze 系统

在设计中实现 MicroBlaze 处理器是赛灵思 Vivado HL WebPACK 版本的一项标准功能。

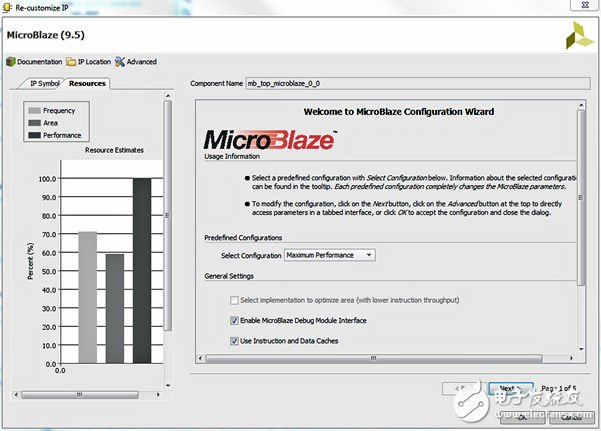

首先要做的是在 Vivado 中创建新项目,并添加一个新的方框图。然后,我们可以从 IP Catalog 中选择添加 MicroBlaze 处理器核。一旦我们将 MicroBlaze 处理器放在方框图中,应针对所需的性能对其进行自定义。打开要自定义的 MicroBlaze 处理器后,会出现五个处理器自定义页面中的第一个。在第一页中,我们可以为处理器核选择所需的性能,如图 1 所示。本例中,我们将开发一个高性能 MicroBlaze 处理器。

图 1:选择 MicroBlaze 的配置。

要创建一个基础的系统,我们需要以下 IP 核:

MIG(存储器接口生成器)– 提供 DDR 存储器接口

AXI UART lite – 双击它可设置 RS232 选项。默认设置是 9600bps,无奇偶校验位,一个停止位。

AXI 定时器

AXI 中断控制器 – 需要一个连接模块驱动来自定时器和 AXI UART lite 的中断。

用于 AXI 数据和指令缓存的 AXI BRAM 控制器和 BRAM

用于输出 166.667MHz 时钟和 333MHz 时钟的时钟向导

MicroBlaze 调试模块

用于连接定时器和 UART 的 AXI 外设互连

用于连接 MIG (DDR) 和 AXI BRAM 控制器的 AXI 存储器互连

针对 MicroBlaze 时钟域的处理器复位系统

针对存储器接口生成器时钟域的处理器复位系统

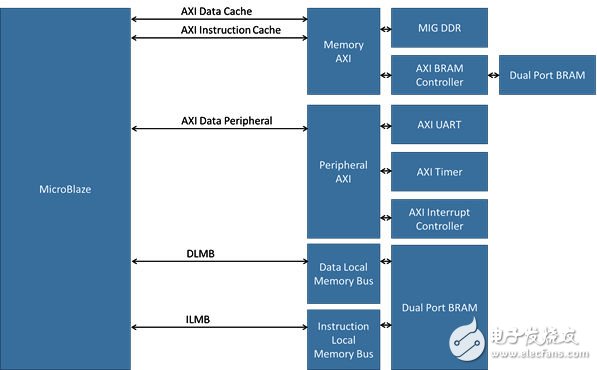

这些模块的连接架构如以下的图 2 所示:

图 2:高级方框图

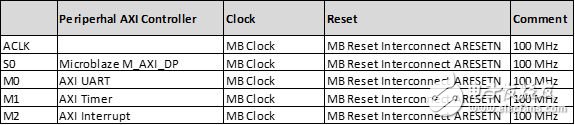

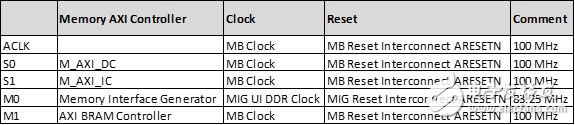

我们将 100MHz 时钟作为时钟向导的输入,该向导利用 MMCM(混合模式时钟管理器)生成 100MHz、166.667MHz 和 200MHz 的时钟。MicroBlaze 处理器将采用 MMCM 的 100MHz 输出来运行,而其他时钟将被用于存储器接口生成器。下面的表 1 和表 2 给出了 AXI 互连的配置:

表 1:外设 AXI 互连,时钟和复位配置

表 2:存储器 AXI 互连,时钟和复位配置

配置 DDR 存储器

我们正在开发高性能 MicroBlaze 系统,因此我们希望能从 DDR SDRAM 执行我们的程序,并且还能使用更多特殊功能(包括 DMA),这样 MicroBlaze 处理器能够处理所捕获的数据。DDR 存储器接口由于其复杂的驱动要求而难以实现,但是赛灵思 MIG 可以自动生成 AXI 总线与 DDR SDRAM 之间的 DDR 接口。

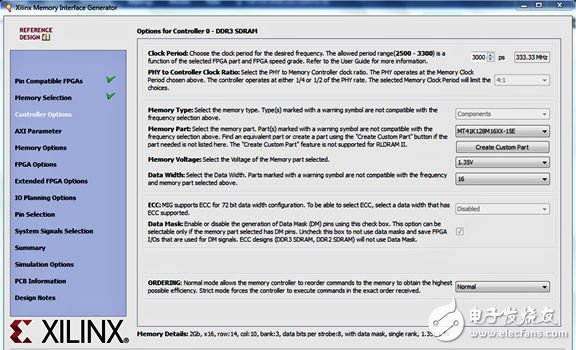

MIG 在 IP Catalog 中提供,通过对它进行自定义,我们可以选择想要的时钟频率、目标存储器设备、存储器选项、终止计划以及引脚分配。图 3 给出了目标 DDR 设备的选择。尽管开始看起来比较复杂,但其实很容易上手和使用,而且运行快速。

图 3:MIG 选择目标设备

根据应用需求对接口进行自定义后,本例中我们需要提供两个时钟:200MHz 参考时钟和 166.667MHz 系统时钟。

设计中所有模块都根据需求进行了自定义,我们可以创建 RTL 包装器并重新生成输出,这样就能构建系统并开发第一个应用。

开发软件

完成项目实现并获得数字文件后,我们可以打开实现后的设计,并将 HDF 和数字文件导出至 SDK。现在,我们已准备好创建软件应用。

如果是第一次打开 SDK,那么软件会询问你想使用哪个工作空间。工作空间是存储项目和相关软件项目文件(例如板支持包 (BSP) 和硬件定义)的区域。

要启动并在 SDK 中运行,我们需进行以下操作:

创建硬件定义项目

为硬件定义创建 BSP

创建应用

构建应用

定义调试环境,以使我们能够通过 JTAG 链路在开发板上运行应用

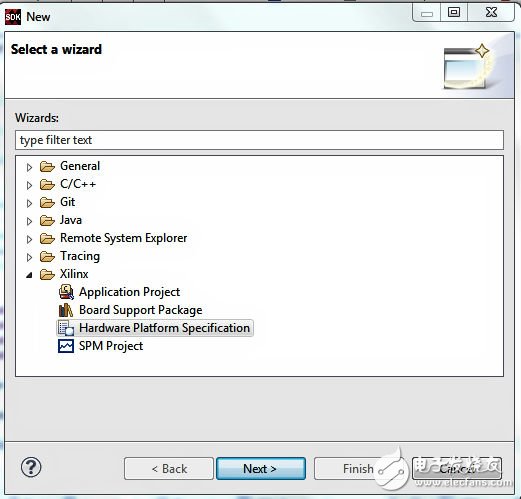

第一步是导入硬件定义。要在 Vivado 中进行此操作,应从 SDK 菜单中选择 file -> new -> other。这会打开一个对话框,如图 4 所示。选择 Xilinx 文件夹下的“Hardware Platform Specification”

图 4:选择硬件平台规范

在下个对话框中输入项目名称。比较好的方法是始终命名为 project_HW,以清楚标明。浏览至 Vivado 项目中包含 HDF 文件的目录。注意,这在 Vivado 项目下的 .sdk 文件夹内。

这样可创建硬件规范,并出现在 SDK 左侧的项目浏览器中。这个项目中,你可打开 HDF 文件,并查看所有存储器映射的外设的地址。

利用创建的硬件平台,我们现在就可创建 BSP。这里面包含用来驱动和控制硬件的驱动程序和 API。我们可选择 file -> new -> board support package,以创建 BSP。这将打开一个对话框,我们可以逐页设置。

输入项目名称。注意它如何关联我们刚创建的硬件平台。本例中,我们使用独立的操作系统。这会打开一个 BSP 的设置弹出窗口。在这里,我们不需要做任何修改,但是如果需要,可以添加一些选项,例如轻量级 IP 协议栈等。

在独立页面中,我们还可为编译器选择 stdin 和 stdout。确保将它设置成 AXI UART。

此时,我们就可以创建自己的应用了。本例中,我使用“hello world”简单模板。我们在 SDK 中选择 -> new -> application project ,以创建应用项目。这将打开一个对话框,我们可以在对话框中选择之前创建的 BSP,以及硬件定义和我们针对的处理器。(本例中只有一个。)

通过这些步骤,我们可以创建一个通过 UART 输出“hello world”字符串的简单应用。选择“build all”以构建 BSP 和应用项目,并产生一个 ELF 文件,你可以下载这个文件并在硬件上运行。

在硬件上运行

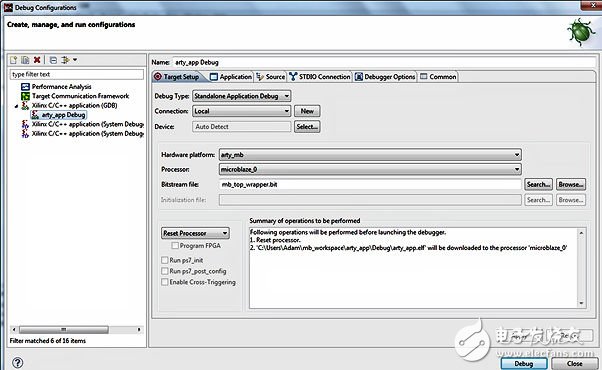

我们需要创建一个调试环境,然后点击下载 ELF 文件。为此,右键点击应用项目并选择 Debug As -> Debug Configurations。这将打开一个对话框,如图 5 所示,在此创建一个新的调试环境。我们希望创建一个新的 GBD 调试应用。

图 5:创建调试配置

提供一个名称,在接近底部的下拉菜单中选择“Reset Processor”。我们还需要点击“Debugger applications”标签,并将“stop at main() when debugging.”选项取消选中,以确保应用程序下载后自动运行。最后,点击apply,而非调试,然后关闭。

首先要做的是对 FPGA 编程。我们在 Xilinx Tools -> Program FPGA 下进行此操作。对 FPGA 编程后,就可以下载 ELF 文件。点击顶部菜单上的“bug”图标,这样就可使用刚刚创建的调试配置。

下载后,你可以看到软件运行,而且“hello world”消息出现在所选的终端程序中。

结论

构建 MicroBlaze 系统非常简单,而且容易实现,开发系统上运行的软件也同样如此。如果你想降低系统的 SWAP-C,那么 MicroBlaze 处理器可以帮到你。

- 相关推荐

- 热点推荐

- MicroBlaze

- swapc

-

SWaP-C高可靠性连接器选择和应用指南2025-01-25 1867

-

VITA 48.8空气流通冷却标准降低了已部署VPX系统上的SWaP-C2022-10-31 3199

-

半导体技术的发展如何帮助实现改进电控天线SWaP-C?2021-06-17 1338

-

半导体技术如何改进电控天线SWaP-C2021-01-20 2739

-

半导体技术的发展如何帮助实现改进电控天线SWaP-C2021-01-05 1747

-

相控阵天线技术在改进电控天线SWaP-C方面有什么优势?2019-08-07 2223

-

电控天线SWaP-C怎么改进?2019-07-31 2602

-

MicroBlaze构建了雷达多目标跟踪的嵌入式系统解决了排序的难点2017-11-24 2791

-

AXI总线的MicroBlaze双核SoPC系统设计2017-10-31 1363

-

基于MicroBlaze的嵌入式系统设计2017-03-01 883

-

基于AXI总线的MicroBlaze双核SoPC系统设计2012-03-09 1767

-

基于Xilinx MicroBlaze的嵌入式I/O系统设计2011-05-14 1027

-

基于MicroBlaze软核的FPGA片上系统设计2009-06-20 3675

-

基于MicroBlaze 软核的FPGA 片上系统设计2009-04-15 718

全部0条评论

快来发表一下你的评论吧 !