使用Vivado高层次综合工具高效评估和实现所选压缩算法

FPGA/ASIC技术

描述

赛灵思的 Vivado HLS 工具有助于降低无线去程网络基础设施不断攀升的成本。

无线网络运营商面临的巨大挑战 在于维持盈亏底线的同时要增大网络的容量和密度。针对无线接口的压缩方案可减少所需的去程网络基础设施投资,有助于应对这种挑战。

我们使用 Vivado® Design Suite 的高层次综合 (HLS) 工具来评估针对 E-UTRA I/Q 数据的开放无线电设备接口 (ORI) 标准压缩方案,以估计其对信号保真度的影响、造成的时延及其实现成本。我们发现赛灵思的 Vivado HLS 平台能够高效评估和实现所选压缩算法。

无线带宽压力

无线带宽需求的不断增加催生了对新的网络功能的需求,例如更高阶的 MIMO(多输入多输出)配置和载波聚合。这样导致网络日趋复杂,从而要求运营商做出架构调整,例如进行基带处理集中化以优化网络资源的使用。在降低基带处理成本的同时,基带处理资源的共享会增加去程网络的复杂性。

这些去程网络负责在基带单元 (BBU) 与远程射频单元 (RRH) 之间传输天线载波调制信号,在光纤上使用通用公共无线接口 (CPRI) 协议是这种网络最常见的实现途径。CPRI 协议需要恒定的比特率,并且经过多年的发展,该协议规范已提高了最大数据速率以满足不断增长的带宽需求。网络运营商正在寻求合适的技术以便能够在显著提高数据速率的同时不增加所使用的光纤数量,从而维持蜂窝基站当前资本支出与运营支出不变。

为提供长期解决方案,网络运营商正在研究可选的网络布局,包括重新设计基带处理与射频单元之间的接口结构以减少去程带宽。然而,重新布局网络功能可能导致其更难以满足一些无线接口规范的严格性能要求。

减少带宽的另一种方法是针对接近或超过可用吞吐量的无线接口实现压缩/解压缩 (codec) 方案。可实现的压缩率取决于具体的无线信号特性,例如噪声等级、动态范围以及过采样率等。

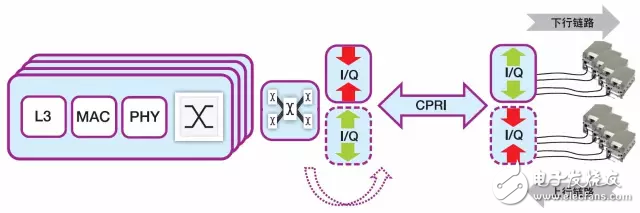

让我们仔细研究一下针对 E-UTRA IQ 数据的 ORI 标准压缩方案——传输调制符号的真实和虚拟组件。图 1 的简化应用实例说明了 CPRI IQ 输入和输出接口中压缩和解压缩模块的位置在滤波器设计过程中对特定的通道特性进行探索,以最大程度减少因下面下采样和上采样引起的信号丢失。

IQ 压缩算法

ORI 标准是在 CPRI 规范的基础上进行了完善和改进,旨在支持开放 BBU/RRH 接口。在最新版本中,ORI 为 10、15 或 20 MHz 的通道带宽指定了有损时域 E-UTRA 数据压缩技术。将固定 3/4 速率重采样与 15 位 IQ 样本的非线性量化相结合,可将带宽要求降低 50%,例如,有助于通过单条 9.8 Gbps CPRI 链路,实现覆盖两个分区的 8 x 8 MIMO 配置。

重采样阶段涉及到对输入 I 和 Q 数据流进行内插操作,使内插数据通过低通滤波器,并对输出数据流进行抽取操作。在滤波器设计过程中对特定的通道特性进行探索,以最大程度减少因下采样和上采样阶段引起的信号丢失。例如,以 30.72 MHz 速率采样的 20 MHz E-UTRA 下行链路通道可输出 18.015 MHz 的 OFDMA 有效带宽,这意味着在 3/4 采样率下可实现理想的无损低通滤波器响应。

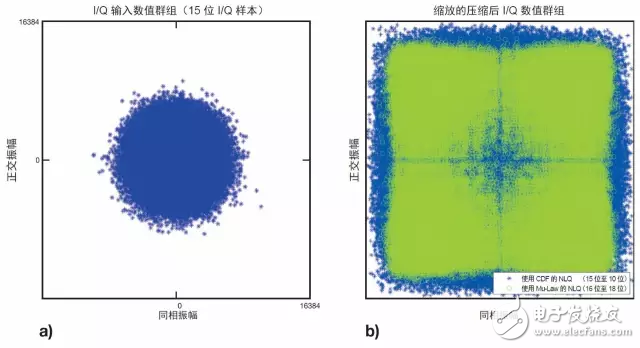

非线性量化 (NLQ) 过程将正态分布的 15 位基带 IQ 样本转化为 10 位量化值。NLQ 使用具有指定标准偏差的累积分布函数 (CDF) 来描述精细粒度下出现频率比较高(而非出现频率比较低)的振幅,以将量化误差减至最小。如图 2b 中的结果所示,量化后数值群组对减小后数值范围的填充比例明显高于图 2a 所示的输入数值群组,因此,与其他线性量化方案相比,量化后数值群组可将量化误差减至最小。通常,I 与 Q 样本实现在查找表中,它们利用其对应的分布函数单独进行量化。我们将 ORI IQ 压缩性能与 ITU-T Recommendation G.711 指定的 Mu-Law 压缩算法实现方案进行对比。同属于非线性量化技术,Mu-Law 利用对数函数在可用数值范围内对量化值进行重新分布。不同于考虑输入样本统计分布的 CDF 量化法,通过 Mu-Law 量化的输出与对应输入样本值和指定压缩值成函数关系。

为了比较 50% 的等效压缩比,我们考虑 16 位至 8 位 Mu-Law 编码器。由于不需要重采样,因此从时延和实现资源成本方面考虑,Mu-Law 压缩是一款低成本解决方案,能够在设计复杂性与可实现的重建信号保真度之间进行权衡。

图 1:采用 CPRI IQ 压缩技术的简化无线系统

图 2:20 MHz E-UTRA DL 通道参考输入帧的 IQ 数值群组 (a),以及压缩后 IQ 数据 (b) 经扩展用以说明每个数值群组的有效数值范围使用情况

向上扩展编解码架构

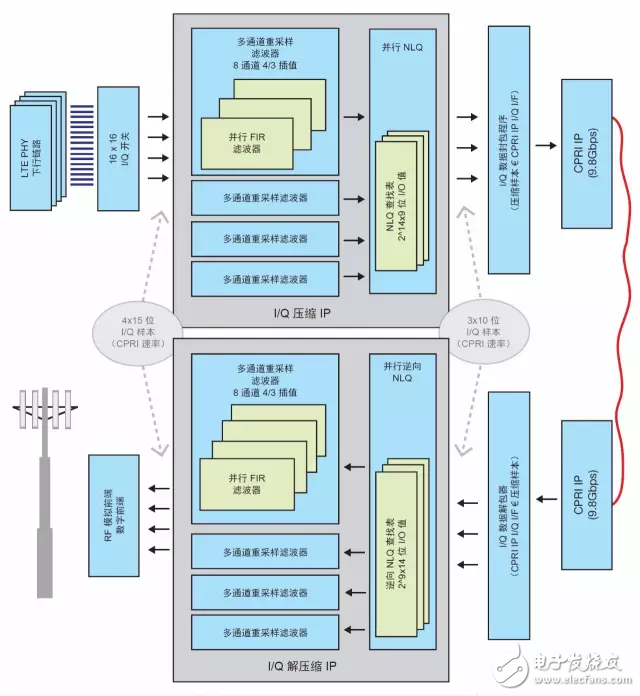

对于原型配置,我们计划将压缩算法向上扩展,以充分利用 9.8304 Gbps CPRI 链路(线路比特率选项 7)。ORI 压缩 E-UTRA 样本规范允许我们通过单个 9.8G CPRI 链路传输 16 条压缩 IQ 通道(32 条 I 与 Q 通道单独压缩)。目标吞吐量为每个 CPRI 时钟输出三个压缩样本,这已足够完全打包 32 位赛灵思 LogiCORE™ IP CPRI IQ 接口,提供所需的 737.28 Msps 的压缩 IP 输出。

以单个时钟域为目标,我们需要构建重采样滤波器以满足每个时钟周期三个样本的输出速率。用 0 的补码对输入样本流进行内插计算允许我们忽略无用的输入样本。输出流变为子滤波器内插速率的函数,每个子滤波器都使用 FIR 系数子集(系数 / 插值速率的总数)。共四个并行滤波器,每个都在一个通道子集上运行,使得整体吞吐量相当于每个时钟周期要求 3 个压缩样本。除高吞吐量以外,所建议的架构还能缩短重采样时延,因为每个子滤波器中仅使用一小部分系数。

对于压缩路径,我们使用累积分布函数 (CDF) 计算 NLQ 量化表。假设 IQ 分布是对称的,我们将 NLQ 查找表的大小缩减至 214 条 9 位量化值。由于我们的设计需要每时钟周期三个并行查找表,因此我们利用相同量化值实现三个并行查找表。可以使用预期或观察的标准偏差值为 I 和 Q 样本单独计算量化等级。或者,以实际的信号级测量值或更高层次的网络参数为依据,单独量化通道子集。解压缩时,我们使用分位函数(逆向 CDF)来计算逆向 NLQ 表。表的大小被限定在 29 个 14 位数值。

我们使用由 MATLAB® LTE 系统工具箱生成的 20 MHz LTE E-UTRA FDD 通道激励来测试已实现的编解码算法。然后,我们使用 Keysight VSA 来解调捕捉到的 IQ 数据,并通过测量输出波形误差矢量幅度 (EVM) 以量化压缩和解压缩阶段引起的信号失真。我们将已公布的输出 EVM 测量值(体现理想信号与测量信号的差异)与参考输入信号 EVM 进行比较。

高级建模与实现流程

我们使用 GNU Octave 语言,并利用其信号处理和统计程序包开发单通道压缩及解压缩模型,启动实现过程。除提供有用的验证参考数据点以外,模型输出还生成了一组 FIR 滤波器系数和量化表。

Vivado HLS 工具从高级数学模型中提供明显的传输路径,从潜在的硬件性能和成本方面评估提议的架构。我们建立了 C++ 测试台,以利用压缩和解压缩函数对输入数据流进行运算。由于我们会将这些函数置于 CPRI 链路的相对端,因此便单独对其进行综合。利用 HLS 流及简单 C++ 循环管理下的交错通道数据流,我们实现了所有内、外部函数接口。

图 3:IQ 编解码架构所示为(仅下行链路中)编解码器 IP 接口处的样本处理速率

我们利用 Vivado HLS FIR IP 来开发重采样滤波器的原型设计。为满足设计的高吞吐量要求,我们实现并行单速率 FIR 滤波器,并采用基于循环的滤波器输出抽取功能。

通过实现多相重采样滤波器,可获得更高效的资源节约型重采样滤波器。多通道分级采样速率转换滤波器就是一种支持 ORI 重采样速率的开箱即用型选择;赛灵思应用指南 XAPP1236-《使用 Vivado 高层次综合以实现多通道分级采样速率转换滤波器设计》对该滤波器进行了介绍。

当验证数据集较大时,快速 C 级仿真的优势就变得愈发明显。对 IQ 压缩算法进行评估时最能体现这一点,因为,至少需要有完整的无线电数据帧(307,200 个 IQ 样本 / 通道),才能利用 VSA 工具进行 EVM 测量。我们发现,C 仿真与 C/RTL 协同仿真相比,仿真速度可提升两个数量级;对于本压缩 IP 测试而言,相比于协同仿真运行时间的 9 小时,C 仿真仅需 5 分钟。

HLS 测试台还具备另一个重要优势,即利用文件和 HLS 流可方便地使用输入数据和捕捉输出数据。结果是可提供一个接口以利用 VSA 工具进行数据分析,或者在 C++ 测试台中直接与 Octave 模型输出进行比较。

性能测量

Keysight VSA 测量结果显示,具有 144 个 FIR 系数的编解码器配置具备 0.29% 的平均 EVM。与 EVM RMS 为 0.18% 的初始输入数据相比,因压缩-解压缩处理链而多出的 EVM 部分为 0.23%。相比之下,同等输入数据集下 Mu-Law 压缩算法实现的平均 EVM 为 1.07%。

根据 Mu-Law 压缩法所减少的时延和资源使用成本来看,当可以将整个 LTE 下行信号处理链的 8% EVM 预算中的 1% 分配给 IQ 压缩时,Mu-Law 压缩就会优于 ORI IQ 压缩方案。然而,任何附加信号失真都意味着要为剩余系统组件设定更严格的性能目标。数字前端器件及功率放大器等组件的成本增加可能会抵消潜在的 IQ 压缩成本优势。

Vivado 高层次综合依据启动间距确认了所需吞吐量——顶层任务准备好接受新输入数据之前的时钟周期数量。同时,经过我们的验证,导出的 Vivado IP Integrator 内核满足目标 Kintex® UltraScale™ 平台的时序要求。

我们将研究范围限定在少量的配置和输入数据向量。然而,一旦系统模型和对应的 C 语言模型就位,即可在几分钟内自定义、实现与评估备选配置。

设计备选方案

从设计工具角度来说,Vivado HLS 提供一个可行的硬件原型设计路径。高级测试平台很适合需要在多种设计与验证工具间传输数据流的设计框架。这种测试平台的主要优势在于能够对硬件系统模型快速执行 C 语言仿真。对于 IQ 压缩及类似应用而言,仿真运行时涉及频繁的高级参数或输入数据集变化,使得快速反馈成为重要因素。

测量结果显示,所建议的 ORI 压缩方案可为 20 MHz E-UTRA 下行链路通道实现低于 0.25% 的信号失真。尽管压缩性能取决于输入通道特性,ORI 压缩方案仍可选择最佳的滤波器设计与量化器参数组合,以提供性能调节范围。

我们原型设计针对所有 16 个天线载波数据流使用通用的静态设计参数集。真实系统中,信号特性可以是事先知道的,或者是可以测量并用来调节设计的。或者,可通过重新配置量化表来动态调节压缩性能,以维持所要求的最低信号保真度。

除压缩性能外,还要考虑执行压缩和解压缩所需的实现资源和附加时延引起的成本。重采样滤波器尺寸与时延占总编解码器成本的主体;更大的 EVM 容差应考虑到具有较少滤波器系数的设计。

考虑到产品上市时间因素,赛灵思创建了基于 ORI 的 IQ 编解码器概念验证。您可在赛灵思网站上了解有关该方案的更多信息,并请求访问相关设计文件。

-

Vivado 高层次综合2012-04-25 3195

-

探索Vivado HLS设计流,Vivado HLS高层次综合设计2020-12-21 4643

-

高层次综合工作的基本流程2021-01-06 1484

-

高层次综合技术的原理2021-02-01 1195

-

FPGA高层次综合HLS之Vitis HLS知识库简析2022-09-07 3863

-

【开源硬件黄金时代02期】从PyTorch到RTL - 基于MLIR的高层次综合技术(文中含回放和课件)2022-11-27 3093

-

利用Mentor高层次综合技术快速实现复杂DSP算法2010-04-29 758

-

使用Vivado高层次综合 (HLS)进行FPGA设计的简介2016-01-06 1462

-

基于Vivado HLS平台来评估压缩算法2017-11-17 1906

-

关于赛灵思高层次综合工具加速FPGA设计的介绍和分享2019-10-06 1962

-

基于Vivado高层次综合工具评估IQ数据的无线电设备接口压缩算法设计2018-07-24 2845

-

揭示高层次综合技术工作的基本概念2021-01-14 2893

-

高层次综合技术原理浅析2021-01-28 1177

-

【开源硬件】从PyTorch到RTL - 基于MLIR的高层次综合技术2022-11-24 2953

-

使用Vivado高层次综合(HLS)进行FPGA设计的简介2023-11-16 543

全部0条评论

快来发表一下你的评论吧 !