基于FPGA的MIPICSI-2接口高清摄像头图像采集系统设计和优势

FPGA/ASIC技术

描述

摘要:阐述一种基于FPGA的MIPICSI-2接口高清摄像头图像采集系统设计,该设计用FPGA实现当前应用广泛的MIPI高清 CCD采集,并提供LCD屏、USB两路输出,数据传输稳定可靠,把MIPI接口摄像头应用到更广泛的其他电路系统中,加快系统开发, 节省成本。

引言

CSI(CameraSerialInterface)是由MIPI(MobileIndustryProcessorInterface)联盟下Camera工作组制定的接口标准,是MIPI联盟发起的为移动应用处理器制定的开放标准,MIPI联盟由ARM、诺基亚、意法半导体和德州仪器发起成立,作为移动行业领导者的合作组织,MIPI联盟旨在确定并推动移动应用处理器接口的开放性标准。CSI接口具有接口少、抗EMI强、速度快、功耗低等优点。CSI-2是MIPICSI第二版,CSI-2由应用层、协议层、物理层组成,最大支持4通道数据传输,单线传输速度高达1Gb/s[1-2]。

系统使用的图像传感器是OV5640, 该CCD分辨率高达5M像素,提供两通道MIPI数据传输[3]。系统使用的FPGA为xilinx的Spartan-6,型号为XC6SLX45,该系列的FPGA拥有业界领先的系统集成能力,同时为成本敏感型应用带来了低风险、低成本和低功耗的最佳平衡[4-5]。

本文阐述如何在FPGA上进行MIPICSI-2接口设计,实现高清摄像头数据采集、显示、接口转换,把MIPI接口摄像头应用到更广泛的其他电路系统中,加快系统开发,节省成本。

1系统设计原理

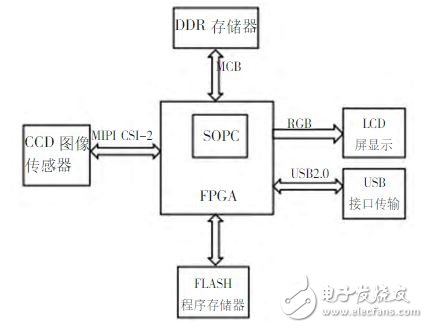

MIPICSI-2图像采集系统如图1所示,整个系统由CCD图像传感器、FPGA、DDR、FLASH存储器组成。CPU使用SOPC,CCD驱动模块、USB驱动模块、LCD驱动模块、DDR管理模块等在FPGA内部设计。

CCD图像传感器经光电转换,把采集到的图像经MIPI接口传到FPGA,FPGA解码后把图像存储在DDR,后分两路输出,一路送到LCD显示屏实时显示,另一路转换成USB接口输出。

图1 MIPICSI-2图像采集系统框图

2 软硬件设计

2.1硬件设计

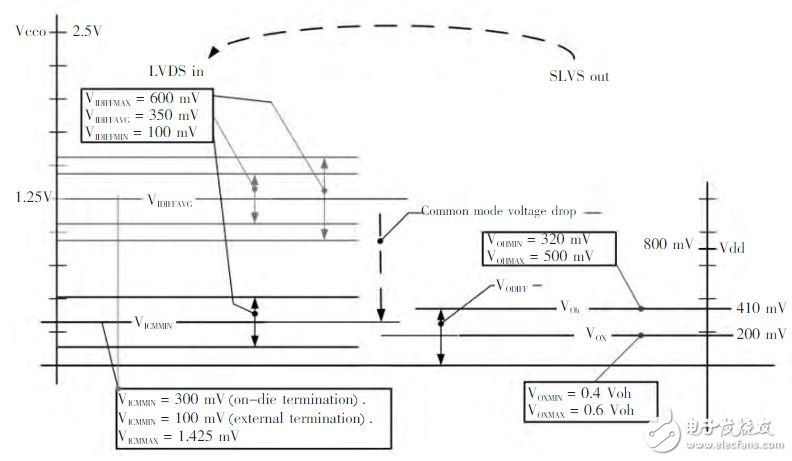

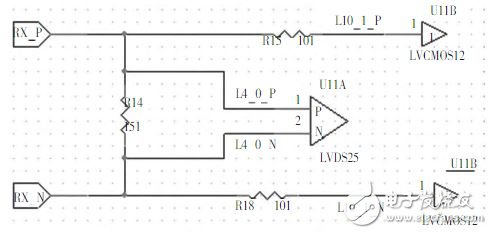

MIPI接口有低功耗和高速两种工作模式,低功耗模 式下的电平为0~1.2V,可直接接到FPGA的I/O口,只需把接口电平配置成LVCOMS1.2V,高速模式下的电平标准是SLVS,其共模电压为200mV,摆幅为200mVp-p,高速模式下的接口连接需要做一些处理。目前市场上的FPGA还没有SLVS电压标准的接口,幸运的是Spartan-6带有LVDS电平接口。由图2可以看出,做为接收端,FPGA的LVDS接口终端电阻使用外部电阻,其共模电压最低可以达到100mv,而SLVS高速模式下的共模电压在200mv左右,在LVDS的允许范围内,可用于MIPI接收,其IO口连接按图3所示的接法设计,解决FPGA与MIPICSI-2物理层(D-PHY)电平匹配问题。

OV5640为两通道MIPI数据口,加上时钟信号,FPGA端用3对LVDS、6个1.2V电平普通IO、2个用于I2C控制普通IO。

DDR选用的为16位MT46H64M16LFBF,其接口控制模块使用Spartan-6自带的MCB硬核设计,MCB可使DDR达到较高速安全运行,并且MCB自带温漂补偿功能,环境适应能力较强。

数据输出部分使用的是标准接口,LCD显示屏接口使用的是24位标准RGB接口,由于FPGA内嵌的USB2.0内核价格昂贵,USB传输系统使用了Cypress公司的CY7C68013芯片。

图2 SLVStoLVDSSignalLevels

图3 FPGAD-PHY接收接口设计

2.2系统设计

整个系统数据处理、驱动设计、接口管理都在FPGA内部设计,FPGA设计时使用工具软件Xilinx ISE DesignSuite13.4,通过硬件描述语言VHDL编程。系统上电后,FPGA自动从FLASH里加载程序,程序加载完毕由SOPC完成各模块参数设置。

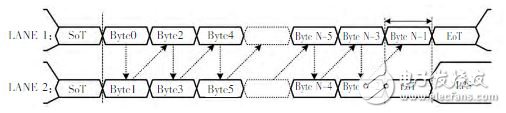

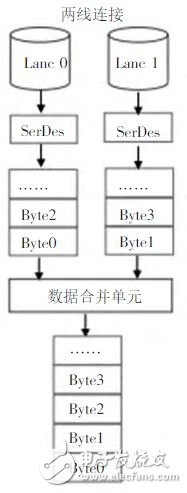

OV5640数据位传送方式如图4所示,通道LANE1传输偶数位,LANE1传输奇数位。FPGA解码模块参考图5所示原理设计,串并转换模块使用ISERDES2原语设计,双通道串行数据经合并单元转换成并行数据后以帧的形式存储到DDR里。

图4 OV5640数据传输方式

图5 FPGA接收数据 处理框图

LCD驱动模块从DDR里读出前一帧数据,然后转换成24位标准RGB数据输出到显示屏全彩显示,同样USB管理模块从DDR里读出数据送给CY7C68013芯片,可配置成ISOCHRONOUS和BULK两种模式输出。

3 实验结果

整个处理系统在单一FPGA内部设计,外围电路简单、无干扰、功耗低。MIPI摄像头高速模式时与FPGA的LVDS接口连接,LVDS选用外部150Ω终端电阻,成功解决了FPGA与MIPICSI-2物理层电平匹配问题。

经测试,OV5640配置成1080P,以30pfs帧率传送,数据传输安全可靠,系统功率小于0.6W,图6为LCD屏的显示效果。另外,USB输出接口可直接挂接到PC或其它USB接口设备上,用于后级图像数据高级处理,加快系统开发。

图6 LCD屏显示效果图

本设计以较低成本成功在FPGA上实现了MIPICSI-2摄像头高速图像实时采集、显示、接口转换。

-

摄像头图像采集基础知识总结2023-09-08 2830

-

【FPGA DEMO】Lab 4:摄像头HDMI显示(高速--HDMI&摄像头)2021-07-30 3373

-

手机摄像头的MIPI接口如何通过FPGA采集2019-12-19 3164

-

基于STM32单片机的摄像头图像采集的处理系统2018-09-06 15996

-

福利来了,各种FPGA驱动摄像头实例分享2018-09-03 10570

-

基于Xilinx FPGA的视频图像采集系统设计2018-07-03 2291

-

【小梅哥FPGA】基于FPGA的CCD摄像头图像采集系统(附源码)2017-09-24 21151

-

例说FPGA连载101:双摄像头图像采集之板级调试2017-05-16 6010

-

例说FPGA连载99:双摄像头图像采集之功能概述2017-05-11 5327

-

做FPGA+摄像头+VGA显示的视频采集系统,摄像头用的ov7725插2014-12-01 30172

-

做FPGA+摄像头+VGA显示的视频采集系统,摄像头选什么的好2014-11-20 3718

-

基于DSP与双目CMOS摄像头的数字图像处理系统2014-11-05 3846

-

Pandaboard MIPI CSI2高清摄像头接口设计2013-07-01 7010

-

网络摄像头监控的系统优势2009-03-25 5734

全部0条评论

快来发表一下你的评论吧 !