详解双向/串行/同步(BiSS)位置编码器的接口

FPGA/ASIC技术

描述

在本博客系列的第一部分,Martin Staebler提供了各类电机位置编码器及其接口的概述。在第二部分中,笔者将对双向/串行/同步(BiSS)位置编码器的接口进行讲解。

BiSS是来自iC-Haus公司的开源协议。它定义了适用于致动器和传感器(如旋转编码器或位置编码器)的数字双向串行接口。(更多详情见 。)BiSS允许单向或双向模式(被称为BiSS-C连续模式)下的串行同步数据通信。BiSS接口与串行同步接口(SSI)硬件兼容。

BiSS协议定义了进入数据部分访问的每一个用户/从站,这些数据部分为:传感器数据部分、致动器数据部分、寄存器数据部分和(如果已规定)多周期数据部分。根据访问和传输性能,每个数据部分均可有不同的设置 —— 这取决于传感器应用。为连接到用户/从站,“BiSS主站”协议应是预先确定的,它可发送数据到位置编码器,也能从位置编码器接收数据。BiSS主站是软件,并在Sitara™处理器或现场可编程门阵列(FPGA)等主机处理器上实现。

BiSS接口有两种物理层(PHY)选项,一种是基于TIA/EIA-422标准的,另一种则是使用LVDS TIA/EIA-644标准的。典型的接口是基于TIA/EIA-422标准的。

BiSS有两种不同的结构选项:点对点结构和总线结构。在本文中,笔者将重点谈论点对点结构。如欲获得更多有关总线结构硬件的信息,敬请参阅5V BiSS位置编码器接口TI Designs参考设计的设计指南。

现今的编码器一般采用点对点结构。当把具有RS422或RS485物理层的BiSS数字编码器连接到伺服驱动器时,笔者建议使用以双绞线作为芯线的屏蔽线缆。编码器线缆通常具有六根或八根可用作信号线和电源线的芯线,如图1所示。100米或超过100米的线缆长度并不少见。

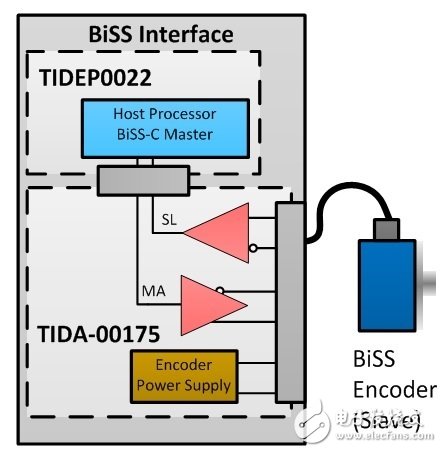

图1:BiSS-C点对点结构

图1展示了一种适用于位置或旋转编码器的典型BiSS配置。在点对点配置中,只有一个设备(具有一个或多个传感器)被连接到主站。

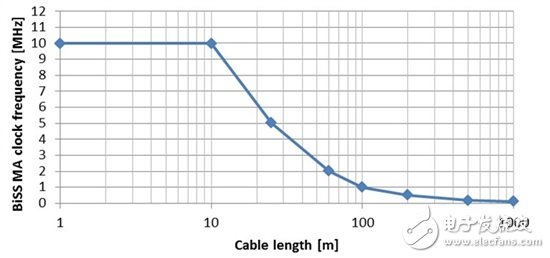

MA时钟频率是可变的。推荐的MA时钟频率取决于线缆长度,如图1中粗略展示的。笔者使用应用手册《BiSS接口AN15:BiSS C主站运行详情》中的表1生成的本图。

图2:推荐的BiSS MA时钟频率与线缆长度

当为BiSS接口的推荐频率进行设计时,10MHz的MA时钟频率将转化为能支持20MBaud的RS422/485收发器。这些是最低要求。使用5V BiSS位置编码器接口TI Designs参考设计进行的测试表明,速度更快的收发器将允许您增加线缆长度,同时仍使用该协议的最高频率,因为该收发器对线缆扭曲的噪声敏感性不强。

适用于BiSS编码器的电源通常需要支持表1所示的参数,不过您应借助您的编码器供应商的产品说明书来确认这些数据。

表1:编码器电源通用规范

对于电源,您将需要考虑该编码器可支持的电压范围以及您的线缆的电压降有多大。一种选择是使用能根据线缆长度改变电压的可编程电源。查看具有可编程输出电压和保护功能、适用于位置编码器接口的电源TI Designs参考设计。

在本系列(讨论的是编码器接口)的下一篇文章中,笔者和自己的同事将提供关于如何实现Endat2.2位置编码器符合EMC标准的工业接口的详细信息。

其它资源

进一步了解适合硬件接口的5V BiSS位置编码器接口TI Designs参考设计。

如欲获得适用于Sitara器件的BiSS主站软件示例,敬请查看具有集成式BiSS C主站接口的ARM微处理器(MPU)TI Designs参考设计。

阅读本博客系列中其它关于位置编码器的博客。

-

HPM5300系列SEI串行编码器接口:如何设置通讯协议(上)2023-12-20 4130

-

5V BiSS位置编码器硬件接口解决方案2018-12-04 4282

-

符合EMC标准绝对位置编码器的通用数字接口2018-11-09 3156

-

C2000 MCU的BiSS-C绝对编码器主接口参考设计2018-10-22 9938

-

电磁兼容(EMC)标准的电机位置编码器接口讲解2018-09-05 3280

-

一个到电机位置编码器的EMC兼容接口设计2018-09-04 2872

-

针对电机位置编码器的不同数字接口选择2018-05-28 13075

-

电机位置编码器接口设计2017-11-17 3378

-

针对电机位置编码器接口的 EMC 兼容设计——第6部分2017-04-26 7926

-

EnDat 2.2-位置编码器双向数字接口2016-03-14 1414

-

5V BiSS 位置编码器接口参考设计2015-04-29 3149

-

开源硬件-TIDA-00175-5V BiSS 位置编码器接口 PCB layout 设计2007-05-28 1046

全部0条评论

快来发表一下你的评论吧 !