基于Zynq SoC增强CCD图像传感器性能

FPGA/ASIC技术

描述

CCD常用于对量子效率、动态范围、暗信号和读出噪声等指标要求极高的高性能图像系统。CCD工作在一种并行/串行架构,也就是说图像的每一线并行移动,输出的线数据在时钟作用下逐像素写入串行寄存器读出。因为CCD是模拟器件,为了获得更好的性能,这些并行和串行转换需要精确的时序和精确的重叠区域控制。许多现有的CCD驱动系统都基于大规模的系统架构,这限制了它们的性能和灵活性。E2V公司“Space Imaging ”项目组的产品开发团队已经研发出了用于内部测试和系统产品的灵活的“proximity electronics core”原型机。这里的“proximity”指的是为了获得更好性能,驱动电路离CCD非常近。这种设计架构允许主要的图像处理工作在前端转换成“安全”的数字信号后可以在远端通过专用的处理集群完成。

这个核心板的主要功能是:

(1)Software-Defined:软件配置操作模式,硬件使用一个类似于SOI 7层协议栈的预定义协议栈;

(2)信号快速转换到数字域,显著的减少了模拟链路路径;

(3)提升了用于定义CCD驱动行为的抽象层次;

(4)产生高精度的时钟;

(5)Network-Enabled:通过千兆网进行高速通信;

(6)Interface-Rich:可以使用许多通用的嵌入式通信接口,如USB、RS-232、 I2C, SPI, CAN等。

开发团队之所以选择使用Xilinx Zynq-7000 SoC用作系统原型,是因为它支持丰富的接口标准,各种功能可根据各自的特点选择在ARM Cortex-A9 MPCore双核处理器(PS)或可编程逻辑(PL)上面完成。Zynq SoC允许设计团队聚焦到增值领域:应用软件、嵌入式软件、FPGA开发和模拟前端设计。

1 什么是Software Defined?

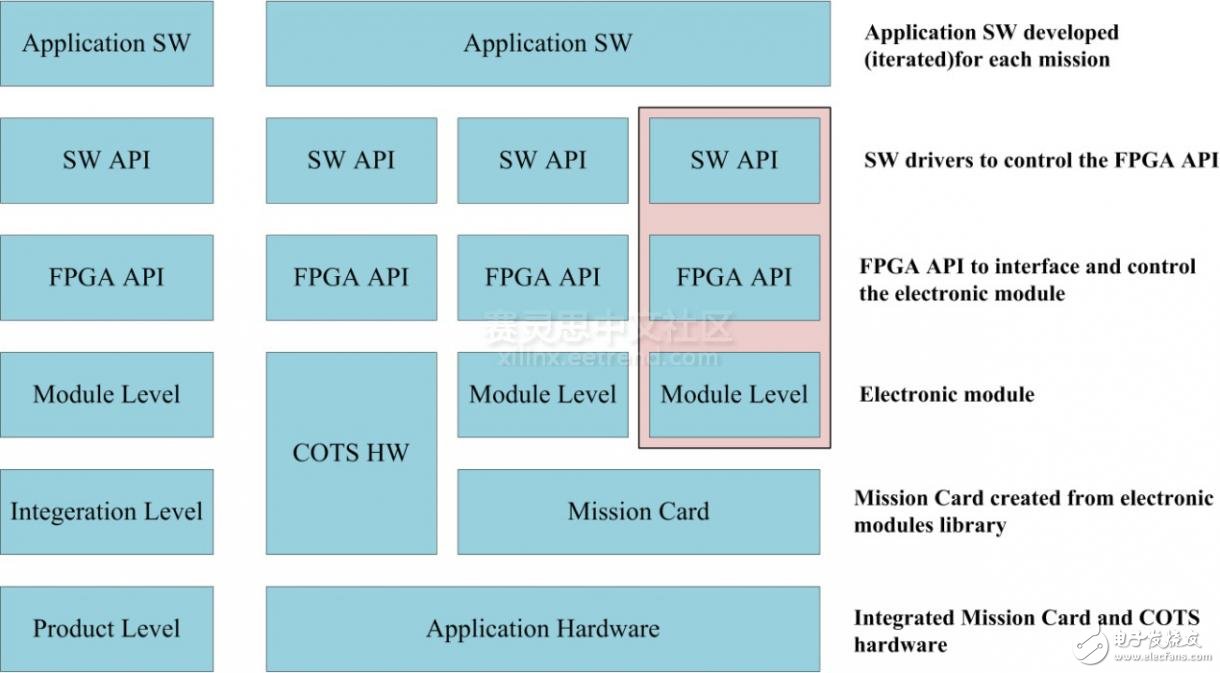

这里没有一个明确的标准定义来自Software-Defined嵌入式系统的各个组件是如何联系在一起的。比如说,没有一个标准化的组装机制来整理基于主机的应用程序、嵌入式系统软件、硬件、COTS、FPGA、电源等等。因此,开发团队采用下面的模型,如图1所示。

图1 Software-Defined嵌入式系统模型

和OSI通信模型非常类似的是,用户创建解决方案时无需提供所有的层级功能。层与层之间和层内都使用工业标准接口进行通信,比如FPGA API层采用AXI总线协议,Module Level采用SPI,I2C通信等。只要有可能,我们都尽量避免使用自定义的接口和协议,因为自定义接口和协议会降低模块间的可重用性并且增加不必要的成本和风险。

2 Proximity Core架构

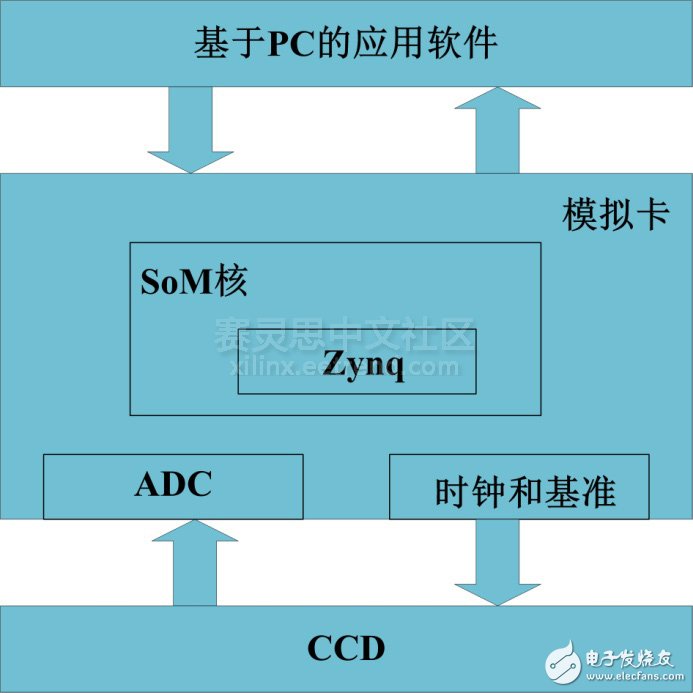

系统架构如图2所示,展示了运行在本地Host的应用软件是如何配置嵌入式系统的。一旦完成配置,由SoM和模拟卡组成的嵌入式系统就会给CCD输出时钟,采样CCD像素数据并封装成以太网帧发出。归功于SoM灵活的IO特性,也可以方便的连接到包括滤光片、快门在内的图像系统的其他硬件。

图2 CCD Proximity Core系统级架构

3 Proximity Core应用软件

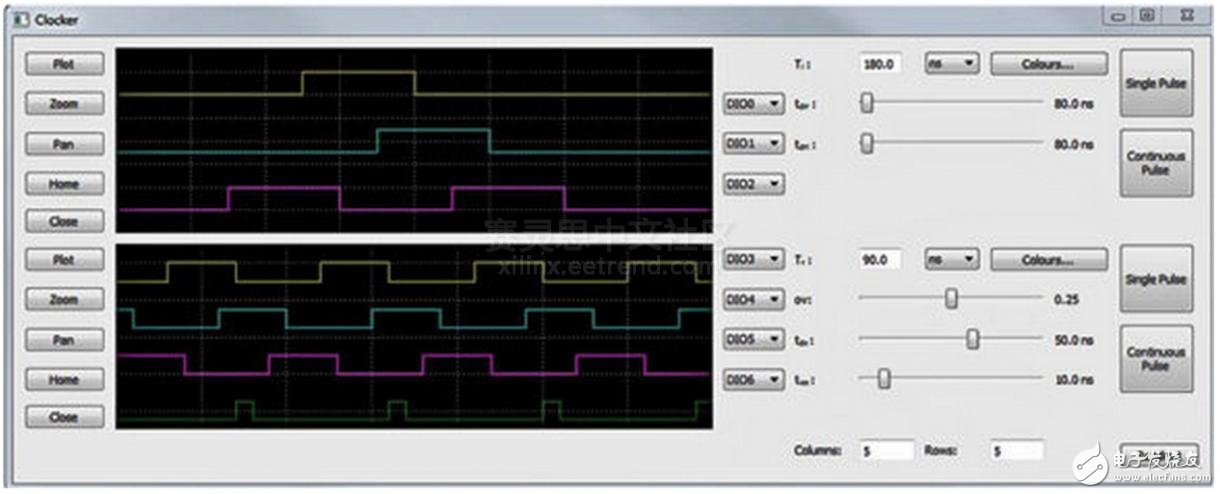

我们用Python语言开发基于PC的应用软件,这个软件允许用户定制图形化的波形图,下图3是软件GUI的截屏。和传统的难调试、耗时多的基于文本的波形文件相比,直观的GUI让人更容易理解用于驱动CCD的波形。

图3 软件GUI屏幕截图

应用软件将用户满意的波形图数据写入到Zynq SoC内的波形发生器使之产生这个波形,这种设计方法可以使用户在设备工作的过程中更新波形,这是针对假设情景分析的一个伟大尝试。

4 Zynq SoC核

标准的核心是运行嵌入式软件和实现FPGA API Levels的Zynq SoC,它完成以下功能:

(1)和基于PC的应用软件通信;

(2)配置Zynq PL内的波形发生器;

(3)产生CCD驱动波形;

(4)和模拟前端连接,并对CCD输出的模拟像素信号进行模数转换;

(5)使用数字相关双采样技术来确定像素值;

(6)通过千兆网发送数据。

以上这些任务分成产生输出波形和输入视频处理两组。产生输出波形需要灵活的、高精度的波形发生器。开发团队在波形发生中使用Xilinx PicoBlaze微控制器,PicoBlaze是一个8位的微控制器软核,每条指令仅用两个时钟周期,实时性能非常高。

PicoBlaze控制器在Zynq SoC PL内完全独立运行,它的可执行代码存储在内部的双端口RAM中。使用双端口RAM代替单口RAM存储PicoBlaze代码的优势是Zynq SoC PS端可以向PicoBlaze控制器实时更新代码。不需要调用通用PicoBlaze汇编器,系统内基于PC的应用程序就可以产生PicoBlaze可执行代码并将它下载到目标器件。

系统大多数图像信号处理(ISP)链路都使用Vivado IP库里面的标准组件,但是输入视频处理需要开发一个自定义的ADC接口和DCDS IP Block。在系统定制和优化过程中,所有的标准和自定义的IP组件都允许通过AXI-Lite接口进行software-defined配置。

输入视频处理内部模块和模块间的数据流通信采用AXI Stream协议传输,允许使用DMA通过Zynq SoC的高性能AXI接口将数据很容易的写到PS端的DDR内存。千兆网专用的DMA将内存中的图像数据搬运到PS的Ethernet MAC发送,这样可以节省ARM处理器的开销。

运行在ARM处理器的嵌入式软件主要负责两大功能:管理PicoBlaze控制器的代码存储空间和将采集到的图像数据通过千兆网发送出去。

使用Zynq SoC一个额外的优势是其内部集成XADC可以实时监控CCD和其他嵌入式组件的运行参数。如果有需要,这些系统健康数据可以叠加在图像数据的后面发出。

5 模拟前端

非常遗憾的是,CCD设备没有一个易用性很好的数字接口。在Zynq SoC输出的数字时钟和CCD时钟输入引脚之间需要一个中间级实现电平转换和大电流驱动。中间缓冲级将数字时钟信号电平变换到CCD需要的电压范围(典型值是8V-30V)并提高电流驱动能力,因为CCD内部设计的原因,它的时钟输入引脚的负载很重。

模拟输入链路将CCD输出的模拟像素信号缩放到适合ADC采样的动态范围内。因为CCD的输出不是一个真正的差分信号,在使用不同类型的CCD时可能需要额外的模拟信号处理,比如说类差分减法。

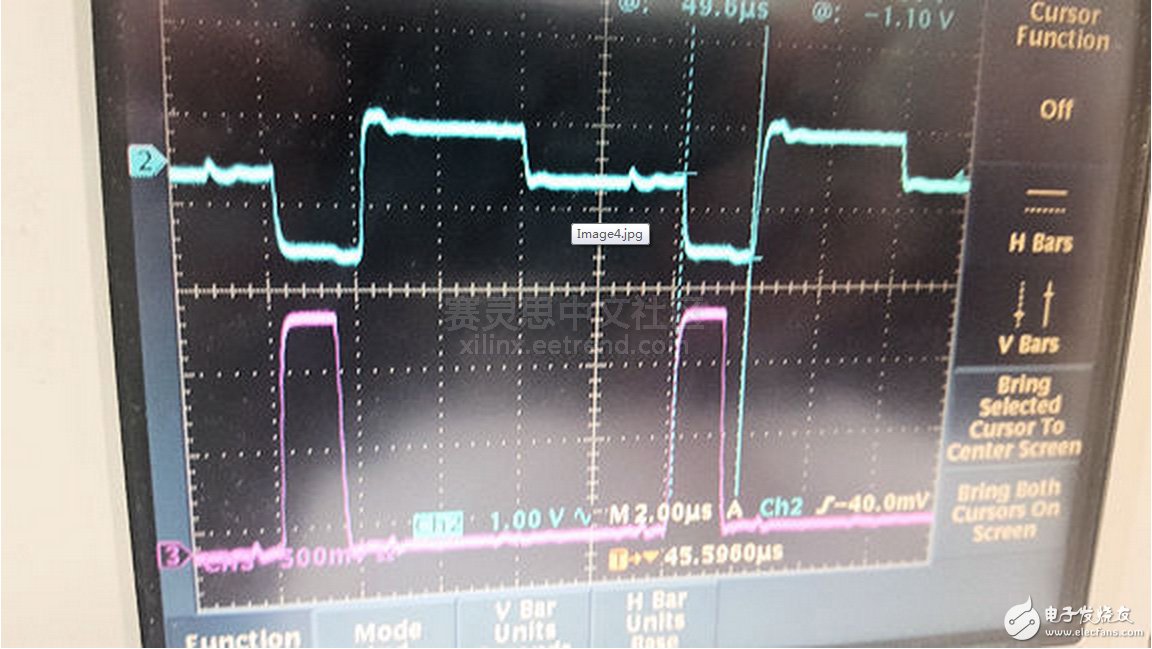

下图4是在电气和光学实验室中从“proximity electronics core”原型机上捕捉到的第一个输出波形。

图4 实验室捕捉到CCD输出的第一个波形

6 将来的性能优化考虑

通常的,CCD输出波形彼此之间,特别是重叠区域对齐必须要非常精密的位置控制。虽然Zynq SoC可以运行在很高的频率下,但是我们可能要求更高精度,也就是对这些信号亚毫微秒级的控制,不包括这个原型机在内,E2V已经开发出了在Zynq SoC ARM处理器的控制下允许亚毫微秒级脉冲控制的技术。结合上述方法,这些额外的控制办法通过粗调和精调时序相结合来确保CCD工作在最佳状态。

-

CCD图像传感器和CMOS图像传感器的区别详解2023-10-11 3597

-

CMOS图像传感器的原理参数和CCD图像传感器有什么区别等资料概述2018-11-07 3704

-

相比CMOS图像传感器 先进的CCD图像传感器变得日益关键2018-09-17 7326

-

Adam Taylor玩转MicroZed系列60:Zynq与PicoBlaze第五章:控制CCD(一种图像传感器)2017-02-08 322

-

CCD和CMOS图像传感器的比较2015-09-06 15444

-

安森美半导体CCD图像传感器增强性能2014-07-15 3828

-

基于CCD与CMOS的图像传感技术2011-02-01 1457

-

CCD图像传感器发展及市场2010-08-19 3012

-

CCD图像传感器,CCD图像传感器原理什么?2010-03-27 6276

-

CCD与CMOS图像传感器技术简介2009-11-07 1093

-

CCD的应用(CCD固态图像传感器)?2009-08-02 4349

-

CCD图像传感器及其数字相机技术2009-04-26 885

-

CCD图像传感器的市场与发展2009-04-25 559

-

CCD和CMOS图像传感器性能比较2009-04-07 813

全部0条评论

快来发表一下你的评论吧 !