对2个LM3880进行简单排序实现6通道加电和断电排序

FPGA/ASIC技术

描述

多通道加电和断电排序已经成为很多电源系统的必备功能。随着这些系统的复杂度不断增加,工程师必须针对更加严密紧凑的计时技术规格进行设计,并且在反向序列出现时具有断电功能,并且能够处理大量的电源轨。

LM3880/LM3881简单电源排序器提供一个简单且精准的方法,来控制这3个独立电源轨的加电和断电—然而,根据目前电源系统所具有的复杂度来看,3通道排序也许还是不够用。所以,对于那些需要对更多电源轨进行排序的系统,你可以将两个LM3880/LM3881器件级联在一起,以实现6通道电源排序。在这篇博文中,我将讨论一下如何将这些器件级联在一起,实现所需应用。

针对3通道排序的单个LM3880

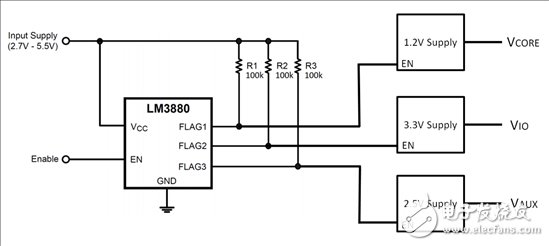

LM3880通常用于3个电源的加电和断电排序,并且在宽温度范围内,借助精密时序功能来提供一个非常简单的解决方案。这一点在断电过程中需要反向序列时特别重要;这种情况会出现在很多微处理器和现场可编程门阵列 (FPGA) 中。图1显示了一个LM3880使用示例;在加电和断电期间,需要以正确加电序列,按照顺序对一个FPGA的VCORE, VIO 和 VAUX 加电。

图1:使用LM3880时的3通道电源排序

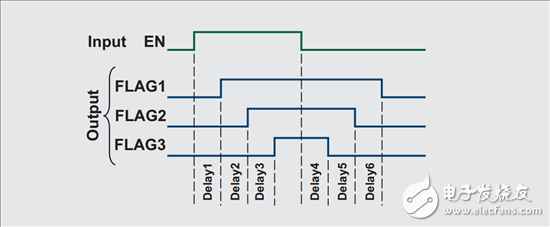

图2显示的是加电和断电期间的时序图。在这个示例中,3个FPGA电源将被启用,从VCORE 开始,每隔30ms的时间;断电时,顺序相反,从VAUX开始。而工程师们常常忽略的是,为了防止杂散电流路径的出现,比如说流经一个FPGA的内部P-N结,反向断电顺序与加电顺序同样重要。因此,正确排序将增加终端产品的使用寿命,并且提升产品可靠性。

图2: 3通道时序图

针对6通道排序的2个LM3880

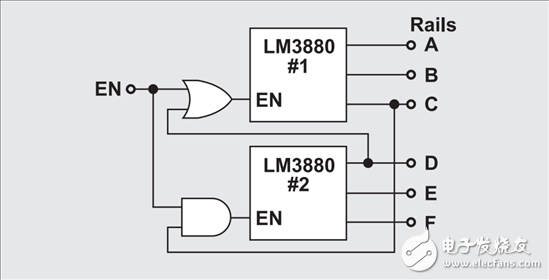

对于需要的电源轨多于3个应用该怎么办呢?有没有一个简单的方法对这些系统进行排序呢?谢天谢地,还真有!你可以将2个LM3880集成电路 (IC) 级联在一起,以实现6通道加电和断电排序,除此之外,只需要一个外部AND门和OR门。图3显示的是这一应用的经简化示例,其中的上拉电阻器被省略掉了。

图3:使用2个LM3880时的6通道电源排序

这个级联系统配置是如何工作的?

加电时,OR门确保1号LM3880被EN上升边缘触发,而且电源轨A、B和C开始按顺序加电。AND门确保2号LM3880在它收到一个EN信号,并且电源轨C被触发之前不会被触发。

断电时,AND门确保2号LM3880可以侦测到EN下降边缘,并且电源轨F、E和D按顺序断电。OR门确保第一排序器在D已经下降前不会侦测到EN下降边缘。

针对级联系统配置的主要设计注意事项

在选定AND门和OR门时,以下是一些主要注意事项:

AND门和OR门输出的摆幅范围应该足够大,这样的话,LM3880的EN阀值可以在上升和下降边缘上触发。

对于两个LM3880 IC,以及AND门和OR门来说,最好使用同样电源。

LM3880 IC的标志输出必须能够触发上升和下降边缘上的AND门和OR门输入。这意味着,在选定AND门和OR门时,你必须考虑他们的输入阀值,以及它们所具有的任何迟滞,并且确保LM3880标志输出的逻辑电平能够触发逻辑门的输入阀值。

正是由于我在上文中提到的原因,LM3880简单电源排序器提供易于使用且准确的解决方案,实现多达6个电源轨的排序。考虑到当前非常严密紧凑的时序要求,以及对于反向断电排序的需要,不会有比这个解决方案更简单的解决方案了。

其它资源:

要获得包括测试波形和全部电路原理图在内的完整测试报告,敬请查看针对多轨输出的简单6通道电源排序参考设计TI Designs参考设计,在这个设计中,突出强调了LM3880在6通道电源排序中的使用。

用WEBENCH® Power Designer快速创建一个完整的排序器设计:

用于3通道排序的LM3880

用于6通道排序的LM3880

- 相关推荐

- 热点推荐

- lm3880

-

探索LM3880:三轨简单电源排序器的卓越性能与应用2026-02-26 651

-

基于LM3880/LM3881的简单6通道电源轨排序解决方案2022-11-17 705

-

一个简单6通道电源轨排序解决方案说明2021-11-10 972

-

LM3880 电源序列发生器2019-04-18 654

-

电源排序得以简化2018-11-21 1485

-

怎么实现6通道电源排序2018-09-04 1632

-

基于LM3880的6通道电源排序器参考设计包括BOM及原理图2018-08-29 3206

-

通过一个6通道电源轨排序轻松解决方案2018-07-18 5257

-

常用于3个电源的加电和断电排序2018-07-11 3326

-

用于3个电源的加电和断电排序2018-05-30 4273

-

2个LM3880时的6通道电源排序方案2018-05-28 3588

-

LM3880/LM3881多通道加电的断电电源排序功能2017-04-18 6630

-

一个简单6通道电源轨排序解决方案2016-01-29 3189

全部0条评论

快来发表一下你的评论吧 !