msp430如何设置时钟及ad模块学习

嵌入式设计应用

描述

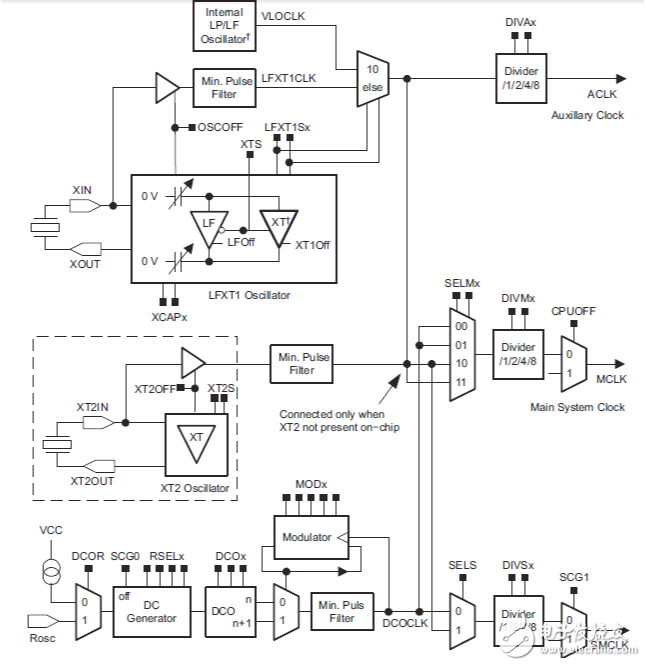

时钟就像是单片机的脉搏,没有时钟单片机是无法工作的,还有其他一些模块也是需要

三个时钟输出:

辅助时钟ACLK(AuxillaryClock):由软件选择来自VLOCK、LFXT1CLK之一经过

1,2,4,8分频之后得到,为外围模块提供时钟源。

主系统时钟MCLK(MainSystemClock):由软件选择来自VLOCK、LFXT1CLK和

DCOCLK之一经过1,2,4,8分频之后得到,为CPU和系统提供时钟。

子系统时钟SMCLK(SubSystemClock):和MCLK一样由软件选择来自VLOCK、

LFXT1CLK和DCOCLK之一经过1,2,4,8分频之后得到,为外围各个模块提供时钟。

四个时钟源:

VLOCLK:片内超低功耗12KHz的内部振荡器。XT2CLK:G2553是没有XT2CLK这个模块的。

DCOCLK:片内可数字控制的振荡器DCOCLK,在软件的调节下该时钟的输出范围为

0.6MHz到26MHz。

LFXT1CLK:由外部时钟源提供的LFXT1CLK时钟源,也即LanuchPad开发板上未焊

接的时钟电路,在这里我们可以焊接一个32.768KHz的低频时钟晶体由G2553的XIN引脚输入。

在MSP430单片机中,一个时钟周期 = MCLK晶振的倒数。如果MCLK是8MHz,则一个时钟周期为1/8us。

一个机器周期 = 一个时钟周期,即430每个动作都能完成一个基本操作。

一个指令周期 = 1~6个机器周期,具体根据具体指令而定。

另外,指令长度只是一个存储单位,与时间没有必然的关系。

MSP430单片机的时钟模块主要包括:

三个时钟:辅助时钟ACLK 、主时钟MCLK 、子系统时钟SMCLK

三个振荡器:低频时钟源LFXT1 、高频时钟源XT2 、数字控制RC振荡器DCO

而MSP430单片机工作所需时钟就是由这些振荡器振荡后经处理产生的。

(1)ACLK:是LFXT1CLK信号经1/2/4/8分频后得到的,主要用作低速外围的时钟

(2)MCLK:是LFXT1CLK,XT2CLK,DCOCLK的三者之一决定,由软件选择,然后经1/2/4/8分频后得到,主要用于CPU和系统

(3)SMCLK:可由LFXT1CLK和DCOCLK,或者XT2CLK与DCOCLK决定,然后经1/2/4/8分频后得到,主要用于高速外围模块

MSP430的时钟模块由DCOCTL,BCSCTL1,BCSCTL2,IE1,IFG1这五个寄存器来确定,具体的功能如下所示:

DCOCTL:控制DCO振荡器

BCSCTL1:控制XT2,LFXT1,DCO振荡,并控制ACLK的分频情况

BCSCTL2:设置三个时钟源分别选择什么振荡器

我们在程序里对寄存器的设置,也就是对三个振荡器进行设置,时钟振荡器设置好了,还要对时钟模块进行设置,也就是让三个时钟模块MCLK SMCLK ACLK选择相应的时钟振荡器以得到不同频率的时钟。

PUC信号后,系统选择内部电阻以实现频率的输出。RSELx = 4 与 DCOx = 3,开始时使DCO有一个适中的频率。MCLK与SMCLK的时钟信号全部来自DCO,约为800KHz(芯片手册)。PUC信号后将LFXT1设置到LF模式(XTS=0),并且关断HF模式(XTS=1)与关断XT2振荡器。

(1)DCOCTL:DCO控制寄存器,地址为56H,初始值为60H

// 7 6 5 4 3 2 1 0

// DCO2 DCO1 DCO0 MOD4 MOD3 MOD2 MOD1 MOD0

//

// DCO0~DCO2:DCO Select Bit,定义了8种频率之一,而频率由注入直流发生器的电流定义

// MOD0~MOD4:Modulation Bit,频率的微调

//

// DCO的设置:通过设置DCOCTL和BCSCTL1,设置DCO的频率

// (1)DCO的调节:

设置DCOR比特来选择是外部电阻还是内部电阻,以确定一个基准频率

通过BCSCTL1寄存器的RSELx来进行分频,确定时钟频率;

通过DCOCTL寄存器中DCOx在标称频率基础上分段粗调,选择频率;

通过DCOCTL寄存器中MODx的值对频率进行细调,选择 DCOx 与 DCOx+1 之间的频率

// 注意:DCO工作在最高频率时,内部电阻正常值大约为200k,此时DCO的工作频率大约为5MHz。

例子:

//DCOCTL初始值为60H,即DCOCTL |= DCO1 + DCO2;

DCOCTL |= DCO0 + DCO1 + DCO2; // Max DCO

//MOD0~MOD4:Modulation Bit,频率的微调一般保持默认即可

//系统默认情况下,RSELx=4

(2)BCSCTL1(ACLK):Basic Clock System Control 1,地址为58H,初始值为84H

// 7 6 5 4 3 2 1 0

// XT2OFF XTS DIVA1 DIVA0 XT5V RSEL2 RSEL1 RSEL0

//

// RSEL2~RSEL0:选择某个内部电阻以决定标称频率(0最低,7最高)

// XT5V:1,该比特未用,必须选择复位

// DIVA0~DIVA1:选择ACLK的分频系数。DIVA=0,1,2,3(DIVA_0,DIVA_1.。。),ACLK的分频系数分别为:1,2,4,8

// XTS:选择LFXT1工作在低频晶体模式(XTS=0)还是高频晶体模式(XTS=1)

// XT2OFF:控制XT2振荡器的开启(XT2OFF=0)与关闭(XT2OFF=1)

//

// BCSCTL1的设置:初始值为84H

//使用XT2振荡器

//控制XT2振荡器的开启(XT2OFF=0)与关闭(XT2OFF=1)

BCSCTL1 &= ~XT2OFF;//清OSCOFF/XT2

do

{

IFG1 &= ~OFIFG;//清OFIFG

OSC_Delay = 255;

while(OSC_Delay --);//延时等待

}

while(IFG1 & OFIFG);//直到OFIFG=0为止

//RSEL2~RSEL0:选择某个内部电阻以决定标称频率(0最低,7最高)

BCSCTL1 |= RSEL0 + RSEL1 + RSEL2;// XT2on,max RSEL

//选择ACLK的分频系数:DIVA=0,1,2,3,ACLK的分频系数分别为:1,2,4,8

//BCSCTL1 |= DIVA_2;//对ACLK进行2分频

//(3)BCSCTL2(SMCLK,MCLK):Basic Clock System Control 2,地址为58H,初始值为00H

// 7 6 5 4 3 2 1 0

// SELM1 SELM0 DIVM1 DIVM0 SELS DIVS1 DIVS0 DCOR

//

// DCOR:Enable External Resister,0—选择内部电阻,1—选择外部电阻

// DIVS0~DIVS1:DIVS=0,1,2,3,对应SMCLK的分频因子为1,2,4,8

// SELS:选择SMCLK的时钟源,0:DCOCLK,1:XT2CLK/LFXTCLK

// DIVM0~DIVM1:选择MCLK的分频因子,DIVM=0,1,2,3,对应MCLK的分频因子为1,2,4,8

// SELM0~SELM1:选择MCLK的时钟源,0,1:DCOCLK,2:XT2CLK,3:LFXT1CLK

//

// BCSCTL2的设置:初始值为00H

//设置BCSCTL2,选定MCLK和SMCLK的时钟源XT2,并可以设置其分频因子

//注意:ACLK只能来源于LFXT1,可以在BCSCTL1里设置ACLK的分频,就是说ACLK最大只能为32768Hz(XIN 与XOUT间接32.768KHz晶振)

//DCOR一般设置为默认值

//设置SMCLK的分频因子,DIVS0~DIVS1:DIVS=0,1,2,3,对应SMCLK的分频因子为1,2,4,8

//BCSCTL2 = DIVS_0;

//BCSCTL2 = DIVS_1;

//BCSCTL2 = DIVS_2;

//BCSCTL2 = DIVS_3;

//设置MCLK的分频因子,DIVM0~DIVM1:DIVM=0,1,2,3,对应MCLK的分频因子为1,2,4,8

//BCSCTL2 = DIVM_0;

//BCSCTL2 = DIVM_1;

//BCSCTL2 = DIVM_2;

//BCSCTL2 = DIVM_3;

//BCSCTL2:设置三个时钟源分别选择什么振荡器

//SELM0~SELM1:选择MCLK的时钟源,0,1:DCOCLK,2:XT2CLK,3:LFXT1CLK

//选择 MCLK 时钟源为XT2,

//BCSCTL2 = SELM_2 ;

//SELS:选择SMCLK的时钟源,0:DCOCLK,1:XT2CLK/LFXTCLK

//选择 SMCLK 时钟源为XT2

//BCSCTL2 = SELS ;

//选择MCLK 与 SMCLK为XT2

BCSCTL2 = SELM_2 + SELS;

//(4)IE1,Interrupt Enable Register 1

// 7 6 5 4 3 2 1 0

// OFIE

// 7~2 and 0 : These bits may be used by other modules

// OFIE:Oscillator fault interrupt enable. 0---Interrupt not enabled

// 1---Interrupt enabled

//(5)IEG1,Interrupt Flag Register 1

// 7 6 5 4 3 2 1 0

// OFIFG

// 7~2 and 0 : These bits may be used by other modules

// OFIE:Oscillator fault interrupt flag. 0 No interrupt pending

// 1 Interrupt pending

//

在PUC信号后,默认情况下由DCOCLK作MCLK与SMCLK的时钟信号,由于DCOCTL初始值为60H,根据需要可将MCLK的时钟源另外设置为LFXT1或者XT2,设置顺序如下:

//(1)清OSCOFF/XT2

//(2)清OFIFG

//(3)延时等待至少50us

//(4)再次检查OFIFG,如果仍置位,则重复(1)~(4)步,直到OFIFG=0为止

//(5)设置BCSCTL2的相应SELM

关于msp430 定时器的捕获比较单元,怎么有3对TA0,TA1,TA2管脚,外加一个TA0

都是TA捕获模式的输出口,可用作PWM输出.TA0输出不能调整占空比.TA1、TA2输出占空比分别对应CCTL1/CCR0和CCTL2/CCR0.(置位/复位模式及复位/置位模式,这两种模式PWM控制最常用)

AD的辅助参考电压和参考电压没有区别,一个大小叫法不同

ad转换时的参考电压是内部T行网络的标准电压,参考电压可以认为是你的最高上限电压(不超过电源电压),当信号电压较低时,可以降低参考 你的参考电压,在计算实际电压时,就需要将参考电压考虑进去。参考电压的稳定性对你的系统性能有很大的影响。 外接了参考电源就不能设置为内部参考,否则短路。

AD外部电压的来源 主要就是从引脚的VCC上的3.3V 接到芯片引脚VEREF上,0电平接V- 就可以了 430芯片里面集成了AD转换器 所以不用外接 参考电压 比如说AD会把参考电压当成0,比参考电压高是正输出。

AVDD 在这里的解释一般为:A代表模拟 VDD代表数字供电 这个AVDD一般在声卡部分AVSS 在这里的解释一般为:A代表模拟 VSS代表接地 VSS这个一般在桥的脚位里出现的比较多

Vref参考电压 比如说AD会把参考电压当成0,比参考电压高是正输出。Vr+,Vr-: AD模块最大,最小值参考电压 当输入大于最大值,AD输出0xfff,小于最小值时,输出为0x0000

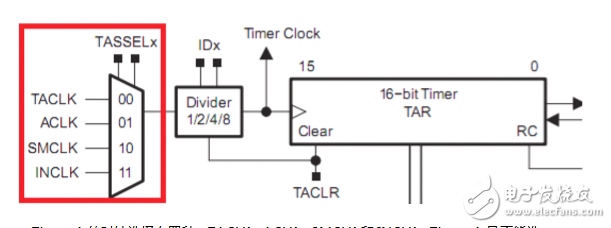

有一些模块的时钟是有自己特有的时钟源的,如Timer_A:

Timer_A的时钟选择有四种:TACLK、ACLK、SMCLK和INCLK。Timer_A是不能选择MCLK作为时钟源的。而INCLK和TACLK是Timer_A特有的时钟源。

-

通过RTC模块DS3231与MSP430连接来制作数字时钟2022-11-11 4713

-

聊聊MSP430单片机的时钟模块2022-02-15 1134

-

MSP430学习笔记-时钟篇2021-12-16 1933

-

解析MSP430系统时钟资源2021-09-26 1071

-

MSP430 G2553 学习笔记--ADC模块2021-09-18 1243

-

如何设置MSP430 时钟?2021-04-02 1856

-

介绍 MSP430 的外围模块2018-06-13 6031

-

MSP430单片机时钟模块2018-05-04 1045

-

基于msp430学习笔记2017-10-12 978

-

msp430内部温度传感器测试程序2016-06-21 786

-

MSP430时钟设置及应用总结2012-08-20 4038

全部0条评论

快来发表一下你的评论吧 !