cd4518应用电路汇总(引脚图及功能和工作原理)

电子常识

描述

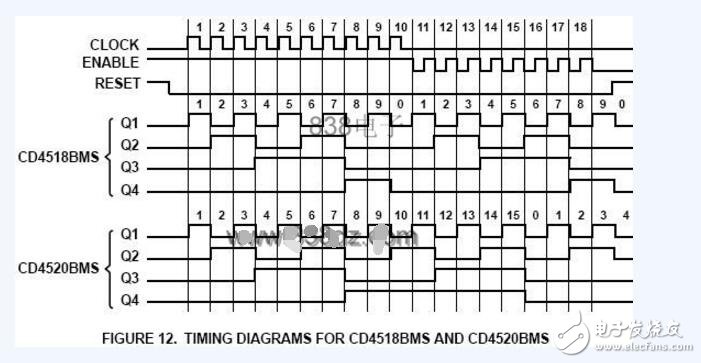

CD4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器。每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

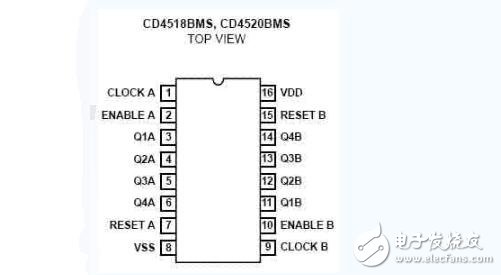

CD4518是一个同步加计数器,在一个封装中含有两个可互换二/十进制计数器,其功能引脚分别为1~7和9~{15}。该CD4518计数器是单路系列脉冲输入(1脚或2脚;9脚或10脚),4路BCD码信号输出(3脚~6脚;{11}脚~{14}脚)。

CD4518引脚图:

CD4518引脚功能:

1CP、2CP:时钟输入端。

1CR、2CR:清除端。

1EN、2EN:计数允许控制端。

1Q0~1Q3:计数器输出端。

2Q0~2Q3:计数器输出端。

Vdd:正电源。

Vss:地。

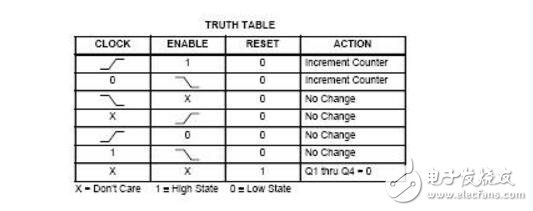

cd4518真值表:

cd4518真值表功能:

CL℃KENABLERESETACTION

上升沿 10加计数

0下降沿 0加计数

下降沿 X0不变

X上升沿 0不变

上升沿 00不变

1下降沿 0不变

XX1Q0~Q4=0

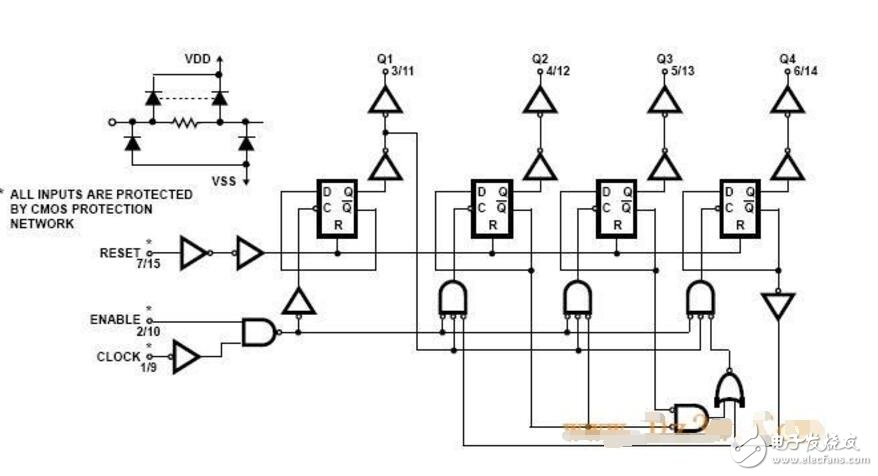

CD4518逻辑图:

cd4518工作原理:

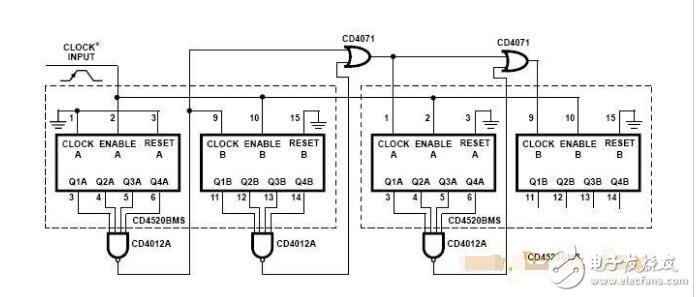

CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。

CD4518时序图:

cd4518应用电路汇总:

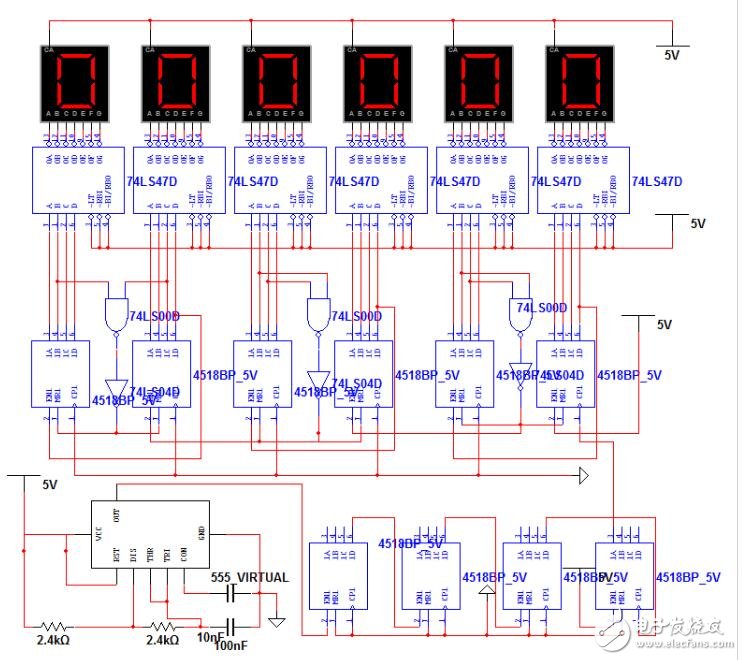

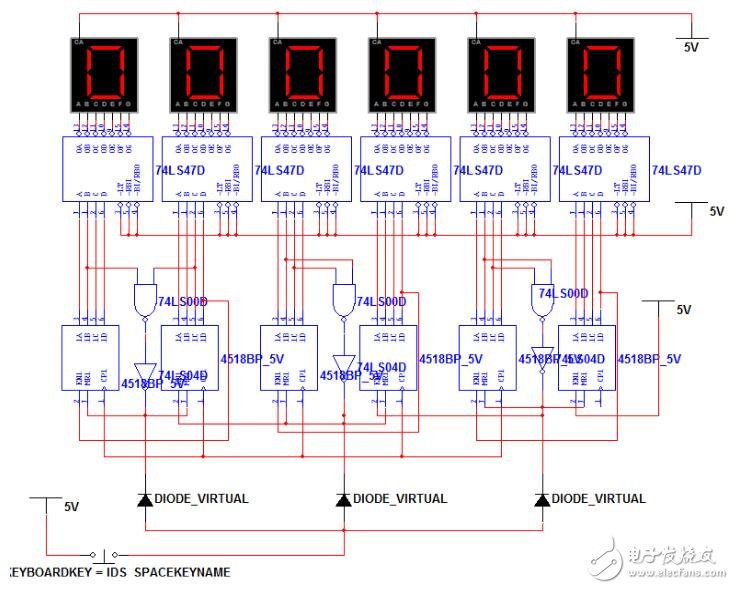

(1)CD4518组成的数字钟电路图

图一为不能进行清零的数字钟

图二为能够清零的数字时钟

图中CD4518的清零端连接了三个二极管,二极管具有单向导通特性,使每个清零端之间没有影响, 当清零端为高电位的时候进行清零,所以,按下清零开关,清零端为高电位,时、分、秒清零。

(2)同步串联二进制计数器负边缘触发器电路

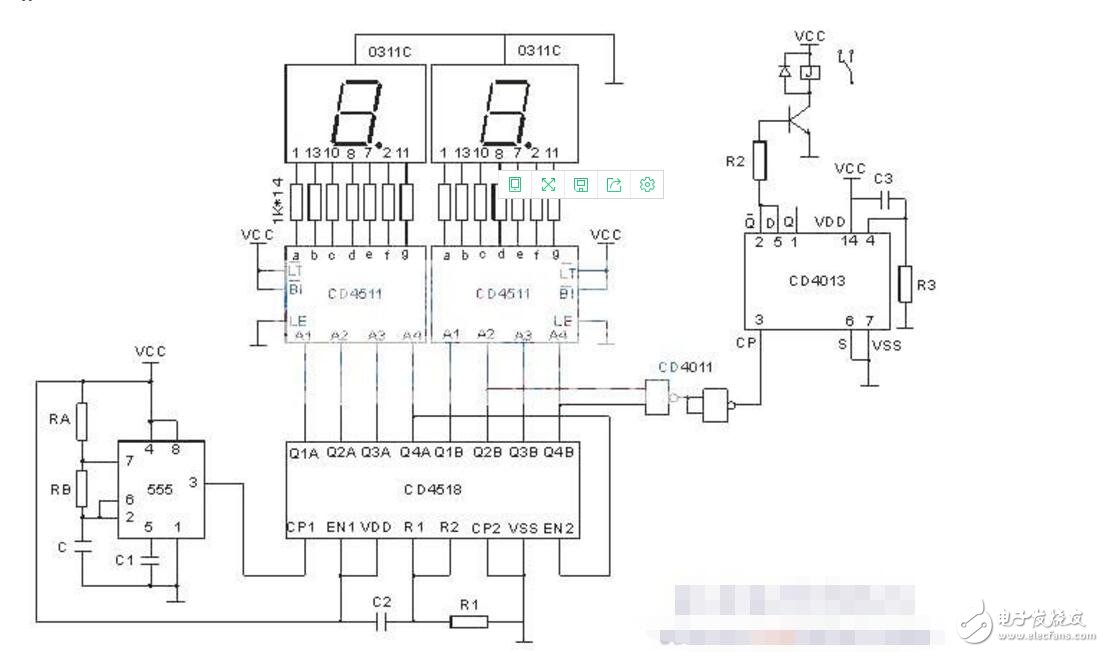

(3)CD4518循环定时器电路

当电路上电时,C2、R1和C3、R3产生一个微分尖脉冲,使计数器CD4518和D型触发器CD4013复位清零。此时D型触发器的Q反为高电平,三极管导通,继电器吸合。

该定时器由555集成电路和电阻RA、RB、电容器C,产生1分钟的的时基信号,经1/2CD4518分频(10分频)后Q4A的下降沿触发下一个分频器。同时Q1A、Q2A、Q3A、Q4A输出BCD码送入CD4511七段译码器驱动LED数码管。当当计数器接受第100个脉冲时,Q1B、Q2B、Q3B、Q4B(0101)时,与非门CD4011输出一个下降脉冲,经反相器反相后变成一个上升脉冲,触发CD4013,使电路翻转Q反为低电平。继电器断电释放,同时计数器自然复位。计数器开始重新计数,这时继电器保持断开状态,只有当计数器计满100个脉冲时继电器才会吸合。因此这个定时器是通电100分钟,再断电100分钟,循环往复。

因为这里的时基信号是1分钟,所以LED数码管显示的数值正好和延迟的时间吻合。如果时基信号不是整数,那么LED数码管只能显示定时的进度。

推荐阅读:

CD4518组成的数字钟电路(cd4518引脚图及功能表与工作原理)

-

cd4518重新上电还会保存原来记的数吗?2020-09-23 2675

-

CD4518同步加法计数器的工作原理和时序图及应用电路汇总2019-07-15 6449

-

cd4047中文资料汇总(cd4047引脚图及功能_工作原理及应用电路)2018-05-11 77443

-

cd4029中文资料汇总(cd4029引脚图及功能_工作原理及应用电路)2018-05-10 82594

-

CD4040中文资料汇总(CD4040引脚图及功能_工作原理及应用电路)2018-04-03 64892

-

cd4027中文资料汇总(cd4027引脚图及功能_工作原理及应用电路)2018-03-29 71725

-

CD4518组成的数字钟电路(cd4518引脚图及功能表与工作原理)2018-03-28 138738

-

cd4051工作原理_引脚图功能_特性参数及典型应用电路2017-12-09 224255

-

cd4518逻辑功能测试电路2017-11-07 20816

-

cd4518中文资料pdf2008-06-11 4541

-

cd4518管脚图引脚图及功能表2007-12-19 71872

全部0条评论

快来发表一下你的评论吧 !