基于SRIO的FPGA间数据交互系统设计与应用

FPGA/ASIC技术

描述

摘要:基于时分长期演进(timedivision- longtermevolution,TD-LTE)射频一致性测试系统中数据交互的分析研究,为了很好地满足现场可编程门阵列(fieldprogrammablegatearray,FPGA)间的大容量数据交互,设计了一种高速的嵌入式技术串行高速输入输出口(serialrapidIO, SRIO),实现2块FPGA芯片间的互连,保证在TD-LTE系统中上行和下行数据处理的独立性和交互的便捷。基于Xilinx公司的Virtex-6系列XC6VLX475T芯片,给出了SRIO接口的整体性设计方案,经过ModelSim软件仿真,确定适合项目需要的数据交互的格式类型和事务类型,对接口代码进行综合、板级验证、联机调试等,在ChipScope软件上对比分析数据传输的正确性,通过测试模块统计比较发送和接收信号的误比特率, 确定了SRIO接口在高速数据传输的稳定性和可靠性,成功验证了SRIO接口在FPGA之间数据的互连互通,并将该方案作为一种新的总线技术应用于TD-LTE射频一致性测试仪系统开发中。

0 引言

随着移动通信技术研究的不断深入, 3GPPLTE逐渐成为支撑世界电信业务的重要移动通信系统。在时分长期演进(timedivision-longtermevolution,TD-LTE)系统的研究中,频分多址技术、多输入多输出(multipleinputmultipleoutput, MIMO)技术[1]等各种创新技术的应用,使得系统的处理能力要求越来越高,高速数字信号处理(digitalsignalprocessor,DSP)以及大规模现场可编程门阵列(fieldprogram-mablegatearray,FPGA)被广泛应用[2],仅仅依靠提高单处理器的性能来提高处理能力越来越艰难,必须采用实时并行处理技术。多处理芯片并行处理是满足系统处理能力要求的有效解决途径,因此,芯片之间的互连显得尤为重要。传统的分级共享总线带宽和速率都很低,其性能已经达到极限,不能满足TD-LTE的高速处理需求。

传统并行总线互连所需要引脚数较多,给器件封装、测试和焊接都带来了一些问题,也会增加在系统中应用的复杂度。而串行高速输入输出口(se-rialrapidIO,SRIO)接口具有速度快、管脚数少、系统成本低、可以实现点对点或点对多点通信等优点。SRIO接口已经成功应用在多DSP处理芯片间 的数据互连[3] 。在多FPGA处理芯片系统架构的TD-LTE系统中,基带处理信息交互急需一种新的 高速互连接口。本文在对SRIO协议[4] 及相关技术 进行深入研究后,设计了一种基于可靠的开放式互连协议标准,实现2块FPGA芯片之间的数据交互方案,提高了数据交互能力,并对传输时延进行分析,满足TD- LTE射频一致性测试系统的性能要求。

1 SRIO技术

1.1 SRIO的简介

SRIO属于系统内部互连技术,适用于高性能的 嵌入式设备的系统内部互连, 还提供了嵌入式系统开发者所需的可扩展性、鲁棒性和效率。RapidIO采用包交换技术,在网络处理器(networkprocessingunit,NPU)、中央处理器(centralprocessingunit,CPU)和DSP之间的通信具有高速、低延迟、稳定可靠的互连性,可行的应用包括多处理器、存储器、网络设备中的存储器映射I/O器件、存储子系统和通用计算平台的数据交互,具有广阔的应用前景。

2011年5月发布的RapidIOv2.1规范提供了2种接口模式(1x和4x)[5] , 1x使用较少的逻辑资源,数据带宽也比较低;4x需要更多的逻辑资源,但是提供了更高的带宽和更好的可靠性。时钟采用内部的差分时钟,支持的波特率[6] 分别有1.25, 2.5,3.125和5Gboud,满足不同的应用需求,还支持多 种事物类型,包括读/写非共享寄存器、流写、维护、门铃和信箱服务等。

1.2 SRIO规范

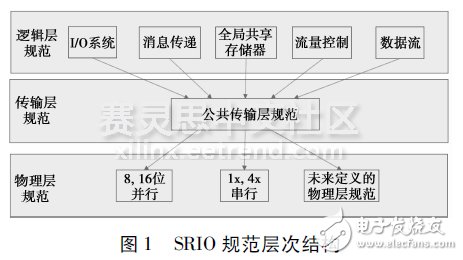

SRIO采用3层分级体系结构[4],如图1所示。

①逻辑层。定义了多种规范,包括I/O逻辑操作、消息传递、共享存储、流量控制和数据流,以及接口的全部协议和包的格式。它们为端点器件发起和完成事物提供必要的信息。

②传输层。定义了RapidIO的地址空间,并提供报文在端点设备间传输所需的路由信息。

③物理层。处于整个分级结构的底部,定义了设备级接口的细节,明确说明了包传输机制、流量控制、电气特性和低级错误管理[7] 。

1.3 SRIO接口写时序

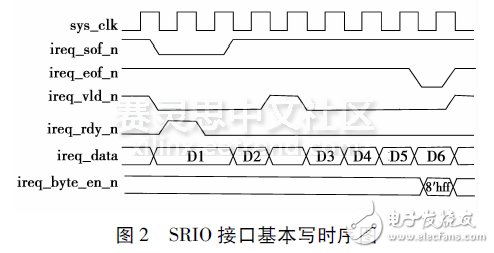

根据实际应用时FPGA用户端通过SRIO接口 发送数据所生成的时序图[6] ,可知其接口的基本时序图如图2所示。

图2中,sys_clk是系统时钟,是由输入的差分 时钟经过时钟模块得到的,比普通单端时钟更稳定;ireq_sof_n是开始信号,标志着一个数据帧的开始;ireq_eof_n是结束信号,一个数据帧的结束标志;ireq_vld_n为有效信号,该信号为低时所传送的数据有效;ireq_rdy_n是开始标志位;ireq_byte_en_n是数据的位使能信号,图2中数据D6对应的ireq_byte_en_n低8位为高,意味着D6的低8位未被使能,还有其他许多的格式控制信号就不在这一一列举。

2 SRIO的逻辑设计与实现

SRIO接口作为FPGA间的数据交互通道,数据 通过接口由主机传送到从机以及由从机传回至主机的过程,在FPGA中由6个主要的模块完成:接口控制、时钟、复位控制、逻辑核、物理核、缓存控制。下面将介绍系统内部实现方案以及各个模块的功 能及Veriolg语言[8]实现方法[9]。

为了仿真和实现图的显示直观方便,这里采用回环的方式来论证,即发送和接收为同一主机,目标地址与源地址相同。

接口控制模块是整个系统的起始端和结束端,用户可以通过该模块来控制所需交互数据大小、类型和格式。随机存储器(randomaccessmemory,RAM)是FPGA用来传输数据的中转站,通过控制RAM中的数据来实现SRIO在2块FPGA芯片之间数据交互功能。

SRIO使用的是专用的差分时钟,频率为156.25MHz或125MHz,不同的时钟对应的传输速率不一样,差分时钟的用户约束为NET“sys_clkn”LOC=“G9”;NET“sys_clkp”LOC=“G10”。这里差分时钟先是经过差分时钟缓存(IBUFDS_GTXE1)和时钟 分频管理单元(MMCM_ADV)后, 得到2个时钟UCLK和UCLK_DV4,用来驱动其他模块工作。

2.1 FPGA设计方案的硬件环境

FPGA是选用2块Xilinx公司的Virtex-6系列 XC6VLX475T芯片。基于采用第三代Xilinx ASMBLTM架构的40nm制造工艺, Virtex-6FPGA系列还拥有新一代开发工具和早已针对Virtex-5FP-GA而开发的广泛IP库支持。Virtex-6FPGA把先 进的硬件芯片技术、创新的电路设计技术以及架构上的增强完美结合在一起,与前代Virtex器件以及竞争FPGA产品相比,功耗大大降低,性能更高并且成本更低。

2.2 FPGA内部实现方案框图

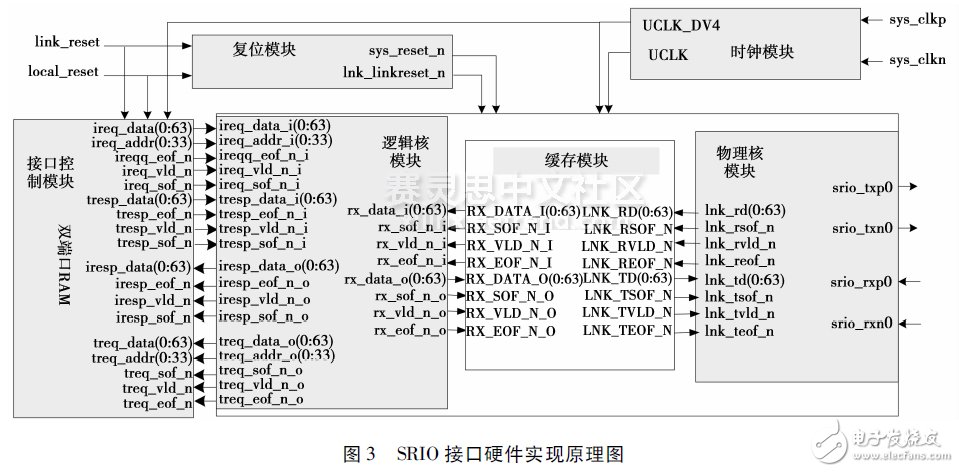

根据SRIO接口构成系统的原理可以设计出SRIO接口硬件实现原理方案框图,如图3所示。SRIO完成2块FPGA芯片间的数据交互,原理图两部分是对称的。

复位模块为整个工程产生复位信号,这里采用 的是异步复位同步释放,当一个系统复位信号出现时这个模块会发出一个链路复位信号。

逻辑层接口由3个部分组成:用户接口、链路接口和维护接口。用户接口又由4个信号端口构成,分别为初始请求ireq、初始响应iresp、目标请求treq和目标响应tresp。用户可以通过接口控制模块来配置这4个信号端口,来实现数据向远端的或写操作。链路接口是用来与物理层通信和缓存器的数据交互。维护操作可以用来发送某些信息,例如,不含端点的器件的错误指示符或状态信息。数据载荷通常放在目标端点的队列中并向本地处理器产生一个中断。

缓存器可以平衡系统性能与资源使用之间的平衡,发送和接收的缓存区间大小是可以配置的。缓存核可以处理所有从物理层返回的数据包,包括包的重发和错误恢复。它能够保证数据包正确到达接收端和物理层的验证。

物理层核( phy sicallayer,PHY )负责处理链路调整、初始化和协议,包括插入循环冗余校验码(cyclical redundancy check,CRC

)和确认标识符到输出的信息包中。PHY使用专用的8B/10B码(即K码)来管理链路,管理内容包括流量控制、包定界和错误报告。

最后在接口控制模块中加入数据收集模块,收集有效的发送数据ireq_data和接收数据treq_data,再用matlab软件对比分析误码率。

3 数据交互仿真与实现

本文使用Xilinx ISE13.4软件,联合ModelSim仿真软件仿真了不同事物格式和类型下多数据包传输。图4主要显示了事物格式字段值为5、事物类型字段值为4的情况下数据交互的控制信号和数据信号的整体波形,由于篇幅的原因,图4只给出了部分发送端和接收端的信号,包括数据信号treq_data_i、开始控制信号treq_sof_n_i、结束控制信号treq_eof_n_i、准备控制信号treq_rdy_n_o、有效控制信号treq_vld_n_i、事务格式treq_ftype_i和事物类型treq_ttype_i等。经过仿真对比分析,验证了发送和接收数据是相同的,且相应的控制信号满足协议要求,仿真实现了2块FPGA芯片间的数据交互功能。

对上述设计的程序进行综合、布局布线,将代码下载到硬件平台后能够正常运行,通过ChipScope软件,可以进一步从实际情况测试接口的正确性和稳定性。通过数据采集,可以得到SRIO在硬件平台上数据交互的测试波形图,如图5所示。FPGA以NWRITE(Ftype=5,Ttype=4)事务类型发送数据,而接收端从物理接口接收数据并以逆向解析出用户数据。

用matlab软件对比发送和接收数据,计算统计得到的误码率低于10-10,满足高速低误码率传输系统的要求,而且各个控制信号都符合协议要求。由图5可知,数据传输时延为122个时钟周期,接口在硬件平台上运行的实际情况与设计方案是相符的,满足接口通信的要求,实现了数据的正确接收并且具有较好的稳定性。从而能够更好地用在实际的开发平台中。

4 总 结

SRIO针对高性能嵌入式系统芯片间和板间互连设计,是未来嵌入式系统互连的最佳选择之一。本文详细介绍了SRIO基本规范、系统组成基本原理、硬件环境和关键模块设计。经过软件仿真和硬件平台,验证了2块FPGA芯片之间数据交互的可行性。并将此模块应用于TD-LTE射频一致性测试仪表系统开发中,如图6所示(TD-LTE射频一致性测试仪基带发送板)。通过实验证明,其工作可靠,达到了设计要求,为下一步数据的正确处理提供了可靠保证。

-

如何使用FPGA实现SRIO通信协议2025-11-12 6187

-

FPGA优质开源模块-SRIO IP核的使用2023-12-12 4068

-

FPGA的SRIO接口使用应注意的事项2024-06-27 6554

-

DSP、FPGA之间SRIO通信的问题?2025-11-15 2958

-

C6657与FPGA(K7) SRIO 口互连的电路设计问题2018-06-19 3870

-

C6672与FPGA的SRIO通信问题2018-06-21 3820

-

关于FPGA与 DSP SRIO通信,请问DSP侧SRIO接收的数据最先在哪里可以看到?2018-08-06 3676

-

请问SRIO数据接收怎么判断FPGA发送过来的数据已经到达DSP指定的空间2019-01-03 4491

-

6678通过SRIO接收FPGA数据,串并转换是在SERDES里面自动进行的吗2019-01-11 2802

-

基于Zynq-7000的SRIO高速数据传输设计与实现2017-12-21 2719

-

Xilinx SRIO IP介绍和使用经验分享2022-08-02 6298

-

在FPGA和DSP两种处理器之间实现SRIO协议的方法2023-03-20 4262

-

基于FPGA的SRIO协议设计2023-09-04 2670

-

srio交换芯片是什么?srio交换芯片的原理和作用2024-03-16 5999

-

FPGA与SRIO调试步骤2024-04-19 2948

全部0条评论

快来发表一下你的评论吧 !