基于DSP与FPGA的实时功率谱分析系统设计

处理器/DSP

描述

摘要: 设计了一套实时功率谱分析系统,主要用于信号的实时功率谱分析。采用DSP 浮点芯片TMS32C6713 作为系统的主处理单元,负责进行功率谱分析; FPGA 芯片Spartan xc2s200 为主控制单元,并通过CY7C68013 USB 芯片与基于LabVIEW 的上位机进行通信。为了保证系统的实时性,在DSP 中使用了实时操作系统内核DSP/BIOS. 它提供了抢占式多线程、硬件抽象、与寄存器配置等功能。分别采用频率为25 Hz、100 Hz 的正弦信号对该系统进行标定。

0 引言

功率谱分析在现代工业中有着极为广泛的应用[1 - 3],如石油探测、噪声分析、机床故障判断等。针对许多应用中对功率谱分析的实时性要求,针对工业中常见信号的特征,设计了该系统,该系统在诸多工业应用的功率谱分析中是可以通用的。

以TI DSP 浮点芯片TMS32C6713 为主处理单元,FPGA 芯片Spartan xc2s200 为控制单元,使用CY7C68013 USB 芯片与基于LabVIEW 的上位机进行通信。同时系统使用了实时操作系统内核DSP/BIOS. DSP/BIOS 是为集成开发环境CCS 开发的一个尺寸可伸缩的实时内核,是为需要实时调度与同步而设计的,提供了抢占式多线程,硬件抽象,与寄存器配置等功能[4]。

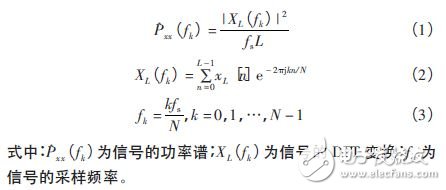

1 功率谱分析方法

系统的功率谱分析采用了非参量方法。具体流程是先使用汉明窗对信号截断为若干段长为L 的子信号段,然后对各子信号段分别进行功率谱估计,最后对各信号段的功率谱取算数平均值。对长为L 的子信号段 的周期图功率谱估计方法如下:

2 系统设计

2. 1 系统整体设计

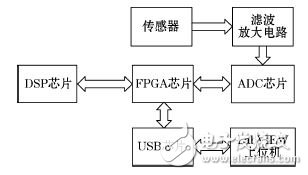

系统整体设计如图1 所示,FPGA 控制ADC 芯片AD9240 进行采样,当ADC 采满512 ×14 bit 数据之后通过通用I /O 口( GPIO) 中断DSP 芯片,DSP 芯片通过增强型DMA( EDMA) 将数据读入DSP进行功率谱估计,DSP 处理完数据后将数据交给FPGA,FPGA 再通过USB 芯片CY7C68013 将数据传输给上位机显示。

图1 系统结构

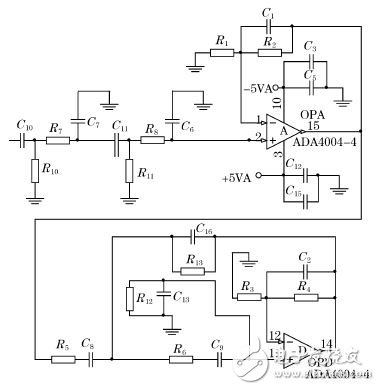

2. 2 滤波放大电路

系统放大滤波电路是由ADA4004 - 4 组成的滤波放大电路,由四阶带通组成,通带范围为10 Hz ~ 3 kHz,放大倍数为1000倍,如图2 所示。

图2 带通滤波放大电路

2. 3 DSP 模块

DSP 模块是整个系统的处理核心。为了保证系统的时序,使用了实时操作系统内核DSP/BIOS 进行任务调度。在DSP/BIOS 中,编写了3 个线程: 读A/D 数据的线void AD( ) ,做FFT的线程void FFT( ) ,写USB 的线程void USB_Write( ) 。3 个线程之间通过Semaphore 通信。

下面以void USB_Write( ) 线程为例说明:

void USB_Write( )

{

while( 1)

{

SEM_pend( &fftComplish,SYS_FOREVER) ; / /等待FFT 的完成

usbWrite( ( float* ) power,N > > 1) ; / /前面已经定义好的函数,将FFT 后的数据传输走

SEM_post( &usbWriteComplish) ; / /告诉其他线程FFT 后的数据已经传输完成

}

}

ADC 芯片由FPGA 控制,并通过FPGA 读取采样后的数据,当FPGA 读满大小为512 × 14 bit 的buffer 后中断DSP,DSP 的线程void AD( ) 通过EDMA 从FPGA 的buffer 读取512 × 14 bit数据,读取完成后触发FFT 线程。

FFT 运算线程void FFT( ) 负责对void AD( ) 读入的512 ×14 bit数据进行FFT 变换,并最后转化为功率谱。FFT 模块是系统计算量最大的部分,考虑到系统的性能,使用库DSP67x. lib,调用它的库函数void DSPF_sp_cfftr2_dit( float* x, float* w,short n) 进行基2 FFT 计算。

当FFT 线程完成后,会触发void USB_Write( ) 线程,将功率谱分析的结果传输给FPGA,FPGA 再将数据传输给由FPGA 控制的USB 芯片CY7C 68013。

2. 4 FPGA 模块

FPGA 模块使用Verilog HDL ( HDL: Hardware Discription Language) 语言编写。FPGA 采用Spartan2 系列xc2s200 芯片。该模块是系统的控制核心,控制着ADC 芯片与USB 芯片,以及通过DSP 的EMIF 接口与DSP 进行通信。

对于ADC 芯片,FPGA 通过接受用户在上位机设定的采样频率,为ADC 芯片提供该频率的时钟信号,使ADC 芯片工作在该采样频率下; 同时在ADC 时钟上升沿到来时读取一次数据ADC 所采样的数据,并存放在FPGA 内部,当FPGA 采集完512× 14 bit 数据之后,中断DSP 芯片,DSP 芯片将数读走。FPGA传输数据给DSP 的Verilog 代码如下:

assign EXT_INT = ( data_addr = = 511) ; / /采完512 个数后FPGA通过DSP 芯片的外部中断引脚中断DSP 芯片

reg[13: 0]TED_o;

always @ ( CE[2] or TEA or dout)

if ( ~ CE[2]&& ( TEA = = 4’b0000) )

TED_o = dout;

assign TED = ( ~ AOE) ? TED_o : 16’bz; / /DSP 芯片读取FPGA内部数据

USB 芯片由FPGA 芯片控制。当FPGA 收到从DSP 芯片传输过来的功率谱分析数据后就会将数据交给USB 芯片的端点0 进行传输,USB 芯片将该数据传输给LabVIEW 上位机显示。

2. 5 USB 模块

USB 芯片采用了EZ - USB FX2 系列芯片之中的CY7C68013,该芯片符合USB 2. 0 标准,可以工作在USB 2. 0 的最大速度下。系统中,USB 芯片工作在slave FIFO 模式下。

2. 6 ADC 模块

ADC 芯片选择14 bit 芯片AD9240,由FPGA 为其提供时钟。

2. 7 上位机模块

上位机软件采用LabVIEW 编写,对功率谱估计的结果实时显示。首先,需要安装NI-VISA,NI-VISA 是一个用来与各种仪器总线进行通讯的高级应用编程接口( API) [5 - 6]。安装完成之后,还需要安装USB 设备驱动程序。之后,就可以在Lab-VIEW 上实现与USB 设备的通信。

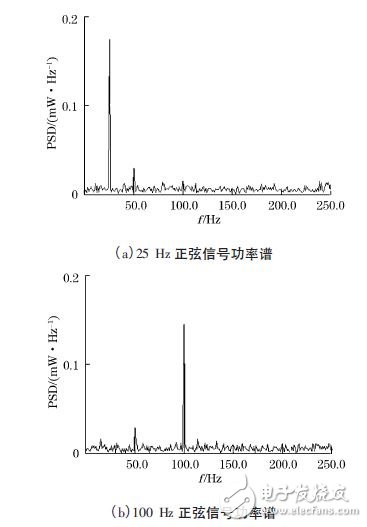

3 系统标定

使用SPF20 信号发生器产生频率分别为25 Hz、100 Hz,幅度为0. 5 mV 的正弦波信号对该功率谱分析系统进行标定,在上位机上对ADC 采样频率设定为512 Hz.

图3 为使用该系统对上述正弦信号功率谱分析结果。谱线高度为0. 125 mW/Hz 左右( 由于有噪声,所以略有浮动) ,这与正弦信号的理论功率谱是吻合的,由此完成系统的标定。

图3 LabVIEW 显示的正弦信号的功率谱分析结果

4 结束语

利用DSP 芯片与FPGA 芯片设计了一套功率谱分析系统,并使用了实时操作系统内核DSP/BIOS,可以保证系统的实时性,完全可以满足对实时性要求很高的工业场合; 同时该系统使用方便,成本较低,配合各类传感器,在工业的许多领域具有很好的使用价值。

-

实时频谱分析仪的关键技术浅析2024-05-16 2402

-

什么是实时频谱分析仪2022-09-01 50504

-

简单介绍实时频谱分析仪2018-11-08 8803

-

基于DSP+FPGA的实时图像去雾增强系统设计2017-12-25 4531

-

基于DSP和FPGA的模块化实时图像处理系统设计2017-10-23 1334

-

基于FPGA+DSP实时图像采集处理系统设计2017-01-03 1270

-

【TL6748 DSP申请】噪声实时分析系统2015-10-29 2165

-

FFT实时谱分析系统的FPGA设计2010-06-25 496

-

用FPGA动态探头与数字VSA对DSP设计实时分析2010-01-07 1011

-

基于DSP+FPGA的实时视频采集系统设计2009-12-16 802

-

使用实时频谱分析评估和优化射频识别(RFID)系统2009-10-17 518

-

DSP+FPGA 实时信号处理系统中2009-09-02 658

-

基于VC++实时海浪功率谱分析软件设计2009-08-13 479

-

基于FPGA和DSP的光纤信号实时处理系统2009-06-19 925

全部0条评论

快来发表一下你的评论吧 !