基于FPGA的软件无线电载波同步技术设计与实现

FPGA/ASIC技术

描述

摘 要:同步系统工作的好坏,在很大程度上决定了通信系统的质量。GPS接收机将天线接收到的卫星信号经射频前端处理后变成了数字中频信号,接收机对GPS卫星的信号处理过程,可依次分为捕获、跟踪、位同步和帧同步四个阶段。针对GPS信号的BPSK调制和强度微弱等特点,模拟GPS 接收机基带数字信号处理过程,首先介绍了科斯塔斯(Costas)接收机的工作原理,分析研究了基于FPGA的软件无线电载波同步技术的实现方法,并采用Costas 环实现了载波同步,性能测试验证了设计的正确性和可行性。

接收机对GPS卫星的信号处理过程,可以依次分为捕获、跟踪、位同步和帧同步四个阶段。由于位同步、帧同步均需要以数据解调为前提条件,除了幅度调制及频率调制可以采用非相干解调外,大部分调制方式都采用相干解调以获取更好的性能,而进行相干解调,接收端就必须提取相干载波。载波同步的性能直接影响着通信系统的性能。针对GPS信号的BPSK 调制和强度微弱等特点,GPS 接收机锁相环通常采用I/Q 解调法来帮助完成对输入信号的下变频、鉴相和数据解调等任务。自同步法是工程上广泛应用的一种载波同步方式。自同步法主要有锁相环、平方环、Costas环和判决反馈环等。目前工程上最常用的抑制载波跟踪环是平方环和Costas环等。由于Costas 环不需要对接收信号进行平方变换,也不需要对锁相环路中DDS 输出的载波信号进行分频处理,因此实现复杂度更小些,所耗费的硬件资源也更少。模拟GPS 接收机基带数字信号处理过程,首先介绍了科斯塔斯(Costas)接收机的工作原理,分析研究了基于FPGA 的软件无线电载波同步技术的实现方法,并采用Costas 环实现了载波同步,性能测试验证了设计的正确性和可行性,对实际应用具有一定的指导价值。

1 Costas接收机的工作原理

目前的载波同步技术有多种电路,其中最常用的有平方环、Costas 环(同相―正交环)、判决反馈环等。J.P. Costas在1956 年首先提出采用同相―正交环来恢复载波信号,随后Riter 证明跟踪低信噪比的抑制载波信号的最佳装置是Costas 环及平方环。传统的模拟Costas 环因存在同相支路与正交支路的不平衡性从而使环路的性能受到一定影响,且模拟电路还存在直流零点漂移、难以调试等缺点,而采用全数字的实现方式,则可以有效避免这些问题。

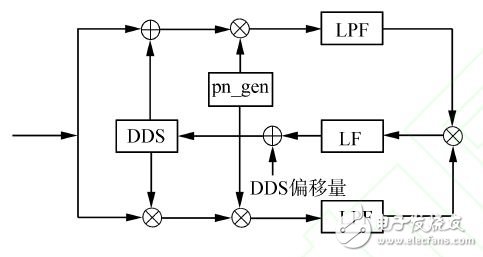

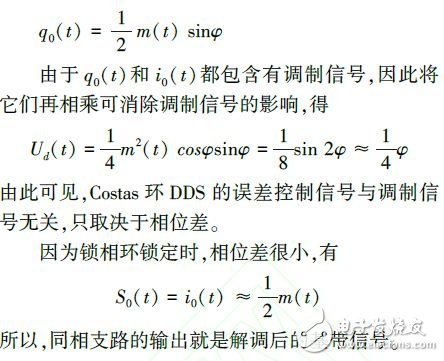

Costas环的工作原理如图1 所示,主要由数字频率合成器(DDS)、数字鉴相器(乘法器)、伪码发生器(pn_gen)、低通滤波器(LPF 和环路滤波器(LF)组成。由于它是由输入信号分别乘以同相和正交两路载波信号,因此常称这种环路为同相―正交环,亦称科斯塔斯环(Costas)。输入信号经上、下支路分别乘以同相和正交载波,然后再与伪码进行相乘,并通过低通滤波器后再相乘,完成鉴相功能,最后经环路滤波器输出控制本地振荡器的误差电压。

2 系统设计与实现

2.1 参数选取

全数字载波环系统参数设计如下:

数据速率:4MHz;伪码速率:10MHz;

载波频率:70MHz;系统时钟:100MHz;

中频采样后的载波频率:6MHz;

信道带宽:20MHz;调制方式:BPSK。

2.2 系统设计

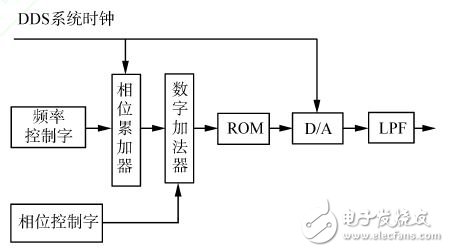

1)直接数字频率合成器的设计与实现直接数字频率合成器的基本工作原理框图如图2 所示。

图2 DDS 基本工作原理框图

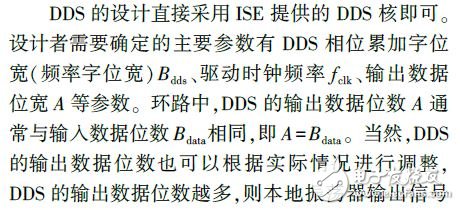

直接数字频率合成器(direct digital frequency synthesizers,DDS,用于产生频率及相位可控的正、余弦信号。DDS 的基本工作原理是在时钟信号的驱动下读取三角函数表。在FPGA实现中,通常采用ISE工具提供的DDS 核来实现。

DDS 的仿真波形如图3 所示。系统仿真是由Modelsim10.1a 软件实现的。

图3 DDS 的仿真波形

2)伪码发生器的设计与实现

GPS 从根本上讲是一个基于码分多址(CDMA)的扩频(SS)通信系统。扩频调制是通过伪随机码或伪随机(PN)序列来实现的。GPS 采用的GOLD序列就是由m序列优选对产生的,其目的之一是用来实现码分多址,目的之二是用来测距。

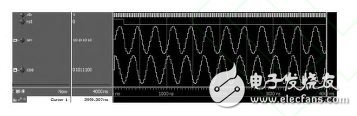

m 序列码发生器是一种反馈移位型结构的电路,它由n 位移位寄存器加异或反馈网络组成,其序列长度M =2n -1,只有一个冗余状态即全0 状态,所以称为最大线性码发生器。

由于其结构已定型,且反馈函数和连接形式都有一定规律,因此利用查表就可以设计出m 序列码。表1 列出了部分m 序列码的反馈函数和移位寄存器位数n 的对应关系。如果给定一个序列信号长度M,则根据M =2n-1 求出n,由n 查表便可得到相应的反馈函数。

考虑用长度m =5 的线性反馈移位寄存器产生一个m 序列。从表1 中选择[3,5]作为反馈连接,编写相应代码进行仿真,结果如图4 所示(初始状态为00001)。系统仿真是由Modelsim10.1a 软件实现的。通过仿真波形可以看出,伪码发生器输出的序列为1000010010110011111000110111010...,码序列周期M=31。

图4 伪码发生器的仿真波形

3)低通滤波器的设计与实现

滤波器是数字信号处理中十分常用的模块之一,一般来讲,对于一些比较复杂的通用数字运算或处理需求,如果目标器件及开发工具提供相应的IP核,则一般选用IP核进行设计,这样不仅可以提高设计效率,同时也可以保证系统的性能。

Xilinx 公司作为世界上最大的 FPGA/CPLD 生产商之一,多年来一直占据行业领先的地位。Xilinx 的FPGA/CPLD具有高性能、高集成度和高性价比的优点,而且它还提供了功能全面的开发工具和丰富的IP核、宏功能等。ISE(Intergrated synthesis Environment)是Xilinx FPGA/CPLD 的综合性集成设计平台,利用该平台可完成从设计输入、仿真、逻辑综合、布局布线与实现、时序分析、程序下载与配置、功耗分析等整个FPGA/CPLD 的开发过程,其最新版本为ISE14.7 suit 系列。ISE13.1 提供了功能十分强大的FIR 核FIR Compiler v5.0。FIR 核进行配置后,即可以使用。

FIR Compiler v5.0核可根据用户需要,选择生成乘/ 加结构(Multiply Accumulate,MAC)或分布式结构(Distributed Arithmatic,,DA)的滤波器;最多可同时支持256个通道;抽头系数从2~1024,输入数据位宽及滤波器系数最多可支持49 比特,能够自动发掘系数的对称性来节省资源。

首先用 MATLAB 仿真低通滤波器系数,对滤波器系数进行n 位量化,并将滤波器系数存入FPGA所需的COE 文件。然后,用FIR 滤波器进行设计和实现。

低通滤波器(Lowpass filter,LPF)的仿真波形如图5 所示。系统仿真由Modelsim10.1a 软件实现。

图5 低通滤波器的仿真波形

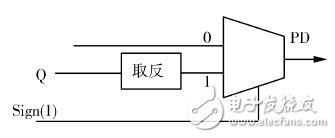

4)数字鉴相器的设计

数字鉴相器原理图如图6 所示。

图6 数字鉴相器原理图

根据图1 Costas环的工作原理,鉴相器实际上是同相支路与正交支路的乘法运算。在FPGA 实现过程中,乘法运算不仅需要耗费较大的硬件资源,且运算速度也会受到一定限制。工程上通常取同相支路的符号位作为过零检测脉冲,并与正交支路进行异或运算。

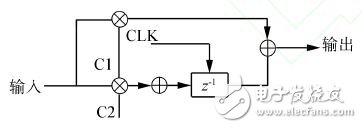

5)数字环路滤波器的设计

数字环路滤波器的结构如图7 所示。

图7 数字环路滤波器的结构图

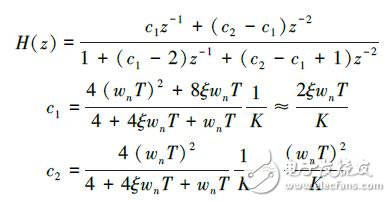

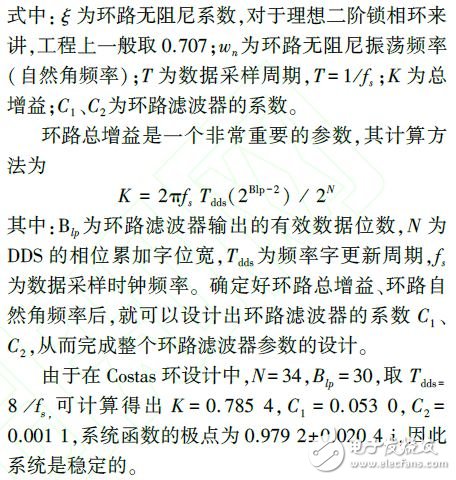

环路滤波器在Costas 接收机中起着非常重要的作用。它具有低通特性,一方面可以起低通滤波器的作用,更重要的是它对环路参数调整起着决定性的作用。在模拟电路中,常用的环路滤波器有RC积分滤波器、无源比例积分滤波器和有源比例积分滤波器。其中高增益的有源比例积分滤波器因其性能优良,是锁相环中应用最为广泛的滤波器(理想积分滤波器)。数字环路滤波器设计的关键问题在于获取滤波器系数C1、C2。

对于理想积分滤波器来讲,其数字化系统函数表示为

3 系统实现与仿真

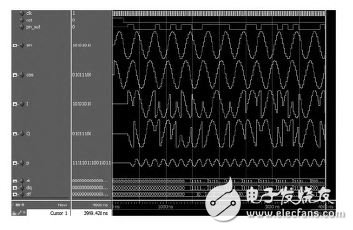

图8 为系统设计在Xilinx ISE开发平台下实现后的仿真波形。系统仿真是由Modelsim10.1a软件实现的。根据无线电技术的惯例,以二进制数“0”代表正电平(+1),以二进制数“1”代表负电平(-1)。从I、Q 支路输出波形可以看出,BPSK调制后,在伪码发生器输出“0”时,载波相位状态不变,在伪码发生器输出“1”时,载波相位会有180度 跳变。通过仿真波形还可以看出,对于不知道伪随机码(PN码)的用户而言,扩频后的信号简直就是噪声。FPGA 实现后,可以在ISE 界面十分方便地查看到整个系统所占用的硬件资源及最高系统运算速度。其中, Slice Registers(寄存器资源)使用了759 个,占3%; Slice LUTs(查找表资源) 使用了631 个,占3%; Block RAM/FIFO使用了1 个,占3%;BUFG/BUFGCTRLs(全局时钟资源) 使用了1 个,占3%;DSP48Es 使用了8个, 占25%。Minimum period:7.958ns{1} (Maximun frequency:125.660MHz) 最高系统时钟频率可达125.660MHz,显然满足设计要求的100 MHz。

图8 系统仿真波形

4 结束语

GPS接收机对信号的跟踪主要是借助载波环和码环来完成的。载波环通过复制一个与接收载波信号的相位或频率相一致的载波,然后让接收信号与复制载波进行相乘混频,以实现对输入信号的下变频,从中获得对接收载波信号的相位或频率的测量值,并且解调出接收信号上所调制的导航电文数据比特。载波同步的性能直接影响着通信系统的性能。全数字的载波同步环对GPS接收机来讲就非常重要。

-

真正实现软件定义无线电设计2015-08-14 3946

-

FPGA-CPLD在软件无线电中的工程应用2009-04-18 7021

-

认知无线电技术实现和挑战2010-04-24 3063

-

软件无线电、无线电的技术概述及应用2018-08-21 4395

-

软件无线电的解调模型是什么2019-05-28 2065

-

基于FPGA的软件定义无线电参考设计2019-07-04 1954

-

采用射频天线实现软件无线电技术2019-07-11 2459

-

如何实现软件无线电的设计?2021-04-08 1769

-

软件无线电的主要原理及技术2023-09-22 1149

-

FPGA在软件无线电接收机实现数字定时恢复2009-07-27 562

-

FPGA在软件无线电中的工程应用之同步技2010-02-09 549

-

实现软件定义无线电和认知无线电的自适应特性2010-03-05 564

-

软件无线电,软件无线电是什么意思2010-04-09 2221

-

基于FPGA技术实现软件无线电的设计2019-07-10 5990

-

使用软件无线电实现扩频通信系统同步性研究2020-07-27 1026

全部0条评论

快来发表一下你的评论吧 !