基于正交频分复用(OFDM)技术的L-DACS1系统设计

FPGA/ASIC技术

描述

摘要:L波段数字航空通信系统(L⁃DACS1)是一种基于正交频分复用(OFDM)技术的多载波传输方案。该系统具有频谱利用率高、抗多径干扰能力强等优点,适用于信号传输信道更复杂的民用航空地⁃空通信,并作为未来数字航空通信系统的候选系统之一。研究了L⁃DACS1系统数字变频器的设计方案,并基于现场可编程门阵列(FPGA)在Apex-CPCI⁃5610通信开发板上实现了这种方案。测试结果表明,该方案能够正确地实现数字上/下变频,能够满足L⁃DACS1系统设计要求。

为了解决地空的数据传输业务增长而带来的高通信速度要求和高宽带要求问题,欧洲EUROCONTROL提出了未来航空通信系统(FAC)的候选系统,即L波段数字航空通信系统类型1和2(L⁃DACS1和L⁃DACS2)。其中L⁃DACS1 系统是一种基于正交频分复用(OFDM)技术,采用频分双工(FDD)模式,工作在L波段的多应用蜂窝宽带通信系统。提供双向点对点寻址数据链通信,该系统具有频谱利用率高、抗多径干扰能力强等优点,适用于信号传输信道更复杂的民用航空地⁃空通信[1]。

数字变频器是软件无线电系统中必不可少的一个模块,其作用是实现发射机基带信号的数字上变频及接收机A/D输出信号的数字下变频。本文通过研究L⁃DACS1协议[2]内容,针对L⁃DACS1系统的特点,基于Xilinx公司的FPGA开发板平台实现了L⁃DACS1系统变频器。

1 数字变频器的方案

本设计利用Matlab整定滤波器参数[3],并利用Verilog HDL 语言编程,在ISE 开发环境下构建系统模型,用ModelSim 仿真软件进行仿真验证,最后下载到Apex⁃CPCI⁃5610通信开发板的V5芯片中,借助示波器和频谱仪对数字变频器进行进一步验证。

在L⁃DACS1 系统中,基带信号的带宽为249 kHz,采样率为625 kHz,根据系统要求及所用的开发板的性能将基带信号数字上变频到30 MHz的载波上,采样率为150 MHz。

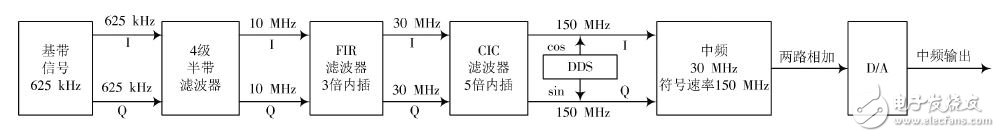

图1显示给出了基带信号数字上变频到中频30 MHz的步骤框图。基带输出的信号采样率为625 kHz,由625 kHz的采样率变为150 MHz的采样率,采样倍数提高了240倍。本设计中选择的上变频方案为:首先经过4级半带滤波器的内插使采样率变为10 MHz,实现低速率的内插;再经过一个FIR滤波器的3倍内插,采样速率变为30 MHz;最后经过一个适合在高采样率条件下工作的CIC滤波器的5倍内插,采样率变为150 MHz,同时调用DDS IP核,产生频率为30 MHz,采样率为150 MHz的正余弦信号,分别与Q路和I路信号相乘,将两路信号的相乘结果相加并经过D/A变换便得到30 MHz的中频信号。

图1 数字上变频方案框图

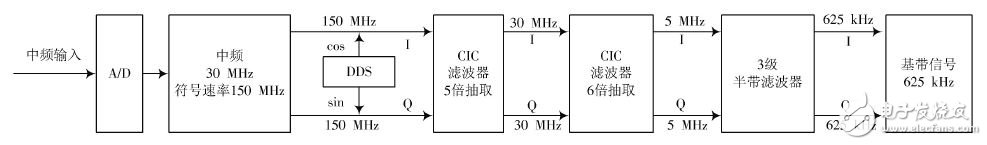

图2显示给出了中频30 MHz信号数字下变频到基带信号的步骤框图。与数字上变频相反,采样速率降低240倍,本设计中选择的方案为:中频信号经过A/D变换后分别与本地载波信号相乘,产生I和Q两路基带信号,首先经过CIC滤波器的5倍抽取,采样速率变为30 MHz;之后再经过CIC 的6 倍抽取,采样率变为5 MHz;以上两个CIC滤波器实现了前端抗混叠的抽取,此时采样率降到了较低的频率,最后再经过3级半带滤波器的抽取即可得到采样率为625 kHz的基带信号,由于半带滤波器工作在较低的频率下,且滤波器的参数得到了优化,更容易以较低的阶数实现。

图2 数字下变频方案框图

2 数字变频器的设计与实现

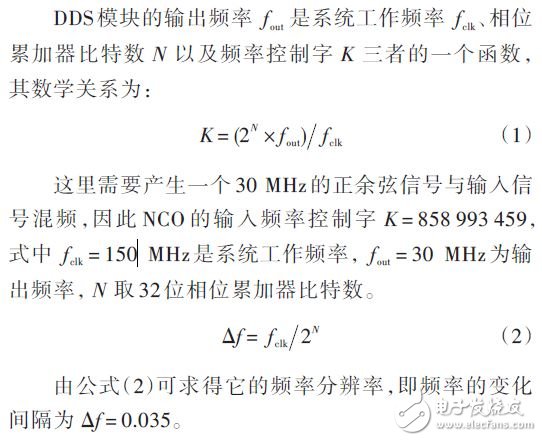

2.1 NCO的设计与实现

在数字变频器中,本地震荡信号是通过DDS(Direct Digital Frequency Synthesis)产生的[4]。DDS 的基本原理是利用采样定理,通过查表法产生波形,DDS的结构有很多种,其基本的电路原理如图3所示。

图3 DDS结构框图

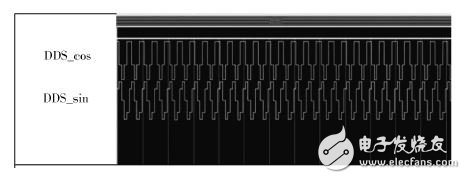

图4 给出了DDS 产生的本地载波信号波形图。由图4可以观测出,NCO可以产生并输出标准的正余弦波形,其中第一路是余弦,第二路是正弦。

图4 本地载波信号

2.2 CIC滤波器的设计与实现

CIC滤波器由积分器、抽取器(插值器)和梳状滤波器组成[5]。CIC滤波器的冲击响应具有如下形式:

以抽取为例,当CIC 滤波器阶数(M)与抽取倍数(D)相等时可以实现CIC滤波与抽取过程同时进行,从而达到减小运算量节约硬件资源的目的。因此在本设计中选择滤波器的阶数和抽取(内插)因子一致。

根据以上分析可知,设计CIC 滤波器时需要考虑两个参数,分别是滤波器的抽取(内插)因子和级联数目,其影响着阻带衰减等性能。

图5 5级CIC滤波器幅频特性(阶数M=5)

2.3 半带滤波器的设计与实现

半带滤波器是一种特殊的FIR滤波器(一半的系数是0),滤波器的通带和阻带对称,即通带容限和阻带容限相等,特别适合作变换因子为2N 倍的抽取或内插运算,计算效率高,本设计采用最优化等波纹法设计滤波器,不仅可以减小滤波器的采样点数,还具有很强的优越性[6]。

在多级半带滤波器系统中,因每级滤波器后均需要进行2倍抽取(内插),又因各级半带滤波器要求通带容限与阻带容限相同,因此可令容限δ 为:

式中:D 为抽取系统总的抽取(内插)因子。在本设计中,设计系统的通带容限和阻带容限均为0.001。

3 系统的建模与仿真

为了验证数字变频器的正确性,本设计中,对变频器输入一个频率为125 kHz,采样率为625 kHz 的正弦波,用ModelSim对变频器进行仿真:

图6给出了在激励信号的作用下,变频器的时序仿真图。由于I,Q两路的模块是一样的,在此只看I路。其中第一路是输入的激励信号源采样率为625 kHz;第二路是经过数字上采样的信号,采样率变为150 MHz;第三路是经过数字上变频输出的中频信号;第四路是数字下变频输出的基带信号,采样率为625 kHz。由图6可以观测出,变频器正确地实现了数字上下变频。

图6 系统时序仿真图

图7 给出了示波器观测到的L⁃DACS1 系统数字上变频后的中频信号时域波形图,为了进一步验证数字上变频的正确性,用频谱仪对中频输出信号进行观测,结果如图8所示。

图7 示波器观测L⁃DACS1系统中频信号波

图8 频谱仪观测L⁃DACS1系统的中频信号频谱

图8 显示的是频谱仪观测的L⁃DACS1 系统数字上变频后信号的频谱图。由图8可以观测出,频谱的宽度是498 kHz,中频在30 MHz,符合L⁃DACS1设计规范,进一步验证了数字上变频的正确性。

4 结语

数字变频器是整个软件无线电中最为关键的信号处理模块之一,本设计采用模块化的思想,对变频器的整体设计方案进行不断优化,同时对数字振荡器、CIC滤波器、HB 滤波器等模块建立模型,不断地仿真和验证,修改参数滤波器参数,最后建立了性能最佳的数字变频器。把数字变频器应用到L⁃DACS1 系统中,实现了整个系统的正确传输,取得很好的效果,因此本设计具有较高使用价值。

-

正交频分复用和普通的频分复用有什么区别?2023-10-09 516

-

OFDM传输技术在水声通信系统的应用2019-07-05 1995

-

OFDM(正交频分复用)通信技术2017-12-05 4208

-

导频叠加OFDM同步方法的FPGA实现2012-02-20 2716

-

短波通信中的正交频分复用技术分析2011-10-11 1169

-

OFDM中基于导频的加窗FFT信道估计2011-06-13 1136

-

正交频分复用信号的全光波长变换性能研究2010-06-02 2249

-

卷积码在光正交频分复用系统中的应用2010-04-23 3153

-

OFDM技术,OFDM技术原理是什么?2010-04-09 3984

-

OFDM,OFDM是什么意思2010-03-13 3331

-

matlab正交频分复用(OFDM)技术-matlab实现仿2010-02-08 880

-

OFDM/OQAM系统中联合迭代信道估计和信号检测2009-10-29 763

-

OFDM(正交频分复用)通信技术原理2009-06-01 2876

-

ofdm的基本原理2008-10-20 7852

全部0条评论

快来发表一下你的评论吧 !