IBERT IP及运行工程生成配置文件与GTX管脚的验证

FPGA/ASIC技术

描述

第一部分 生成IBERT IP及运行工程生成配置文件

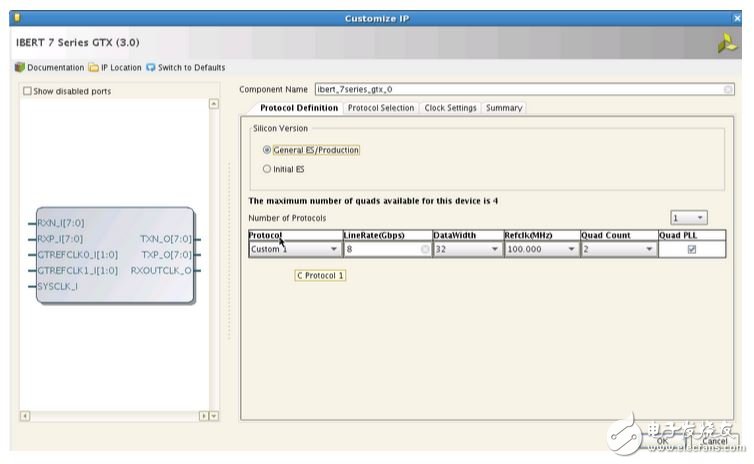

1. 选择IP,选择FPGA版本,protocol数量 (所有通道用一个速率的话一般只选择1个 protocol),速率,参考时钟频率,通道数量和Quad PLL(大于6G的速率时必须选择)

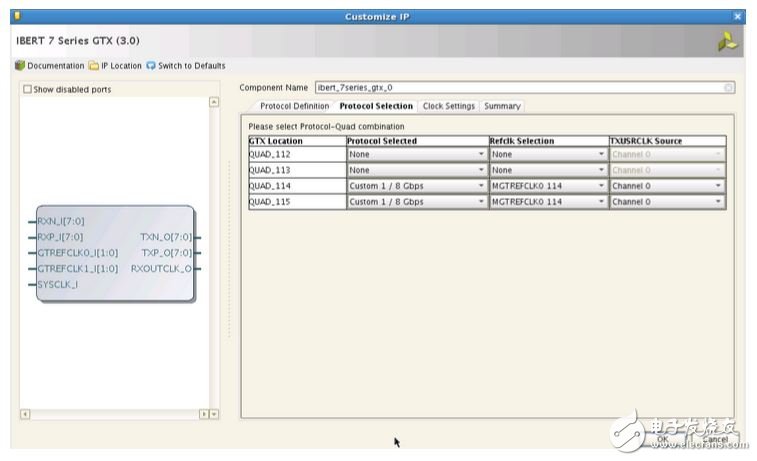

2. 选择需要的Quad 通道114和115,及参考时钟源,这里选择合用QUAD114的参考时钟

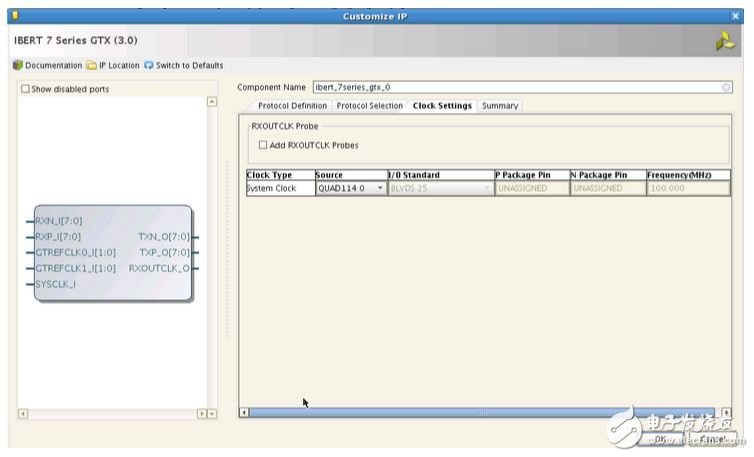

3.时钟源选择QUAD_114_CLK0做为整个IP的系统时钟,当然这个需要根据硬件实际情况来选择。

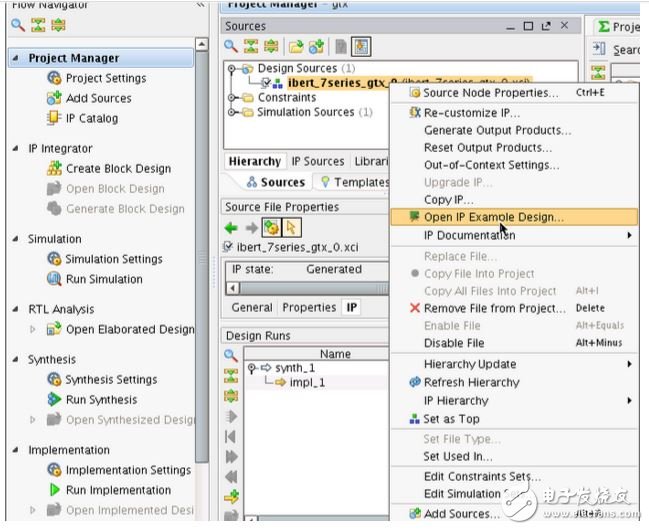

4.生成IP之后在IP的顶层右键点击Open IP Example Design,然后会打开一个新的VIVADO界面。

第二部分 上板利用IBERT验证GTX管脚

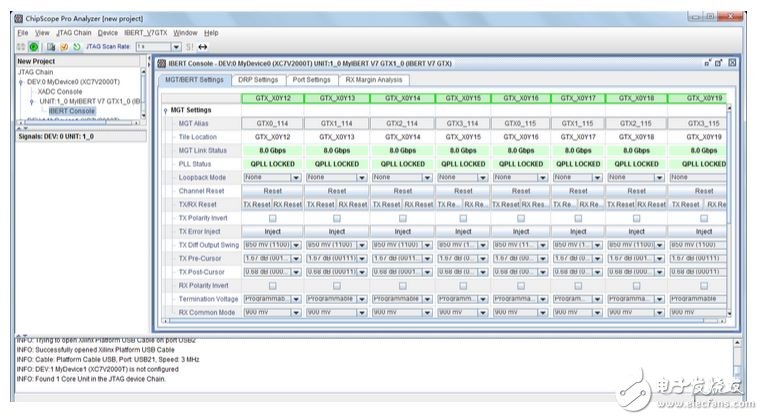

5.如果需要在ISE的ChipScope中查看IBERT时,直接点击ISE的ChipScope的Analyzer,然后点击链接->配置FPGA。如下图所示

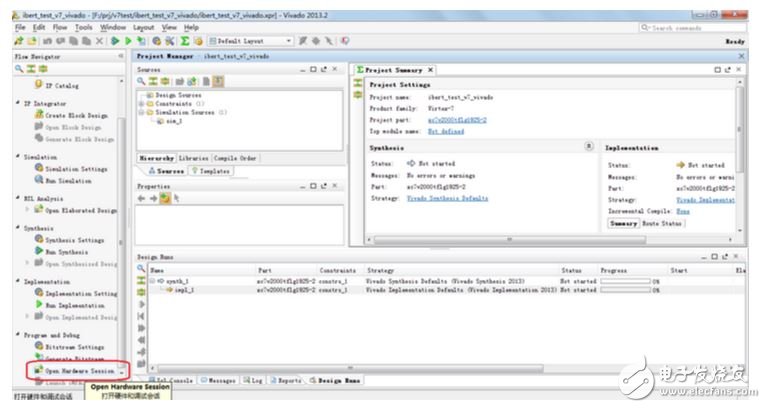

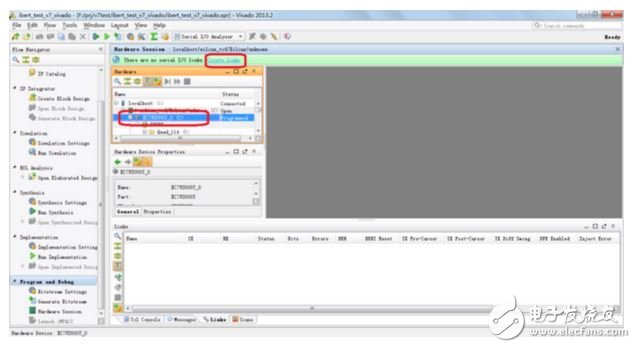

6.如果是要在Vivado中查看Ibert,则需要打开Hard ware Session,如下图所示

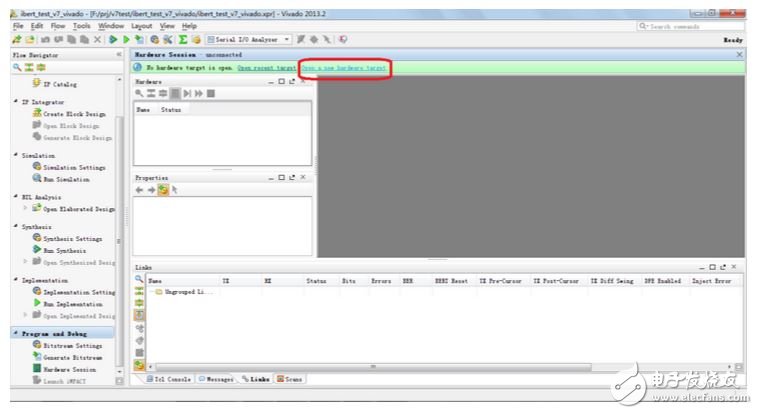

7. 点击Open a new hardware target

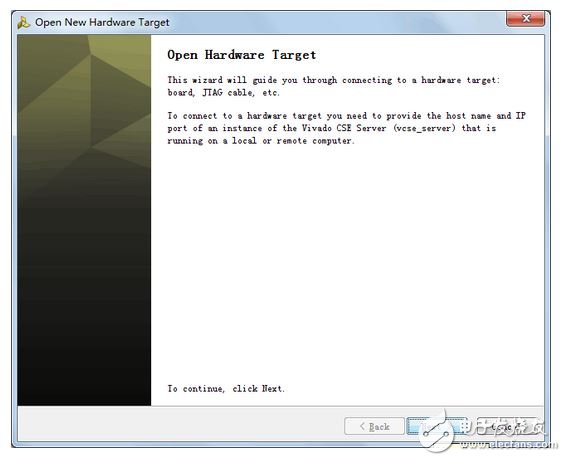

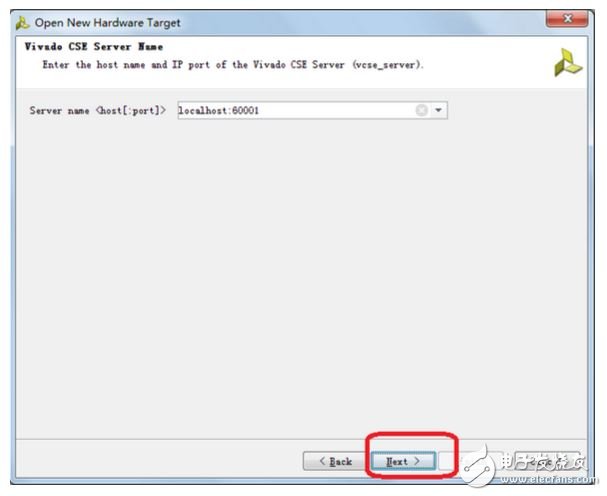

8. Open a new hardware target界面点击Next

9. 不用更改,点击next

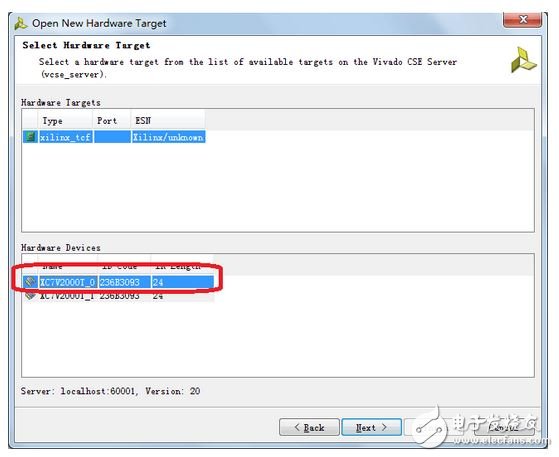

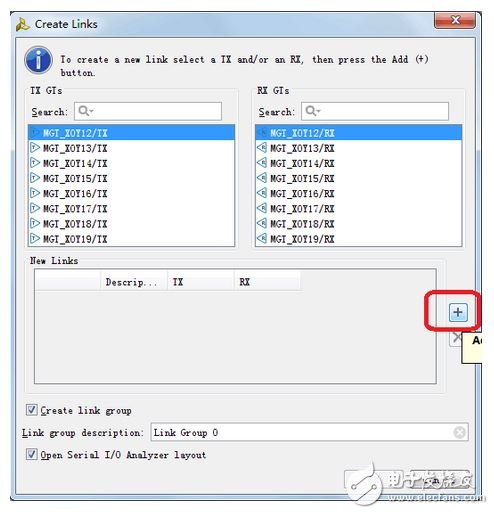

10.选择目标FPGA芯片点击next

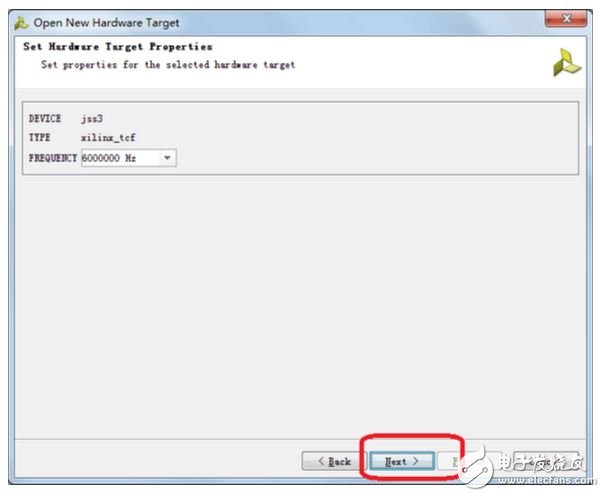

11.无需更改,点击next

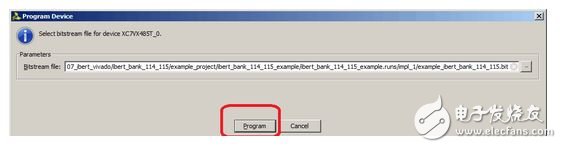

12. 选择配置文件

13.选择配置的FPGA,点击右上角create links

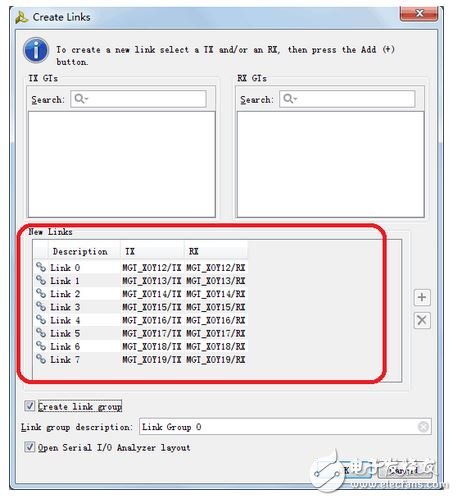

14.点击+号将所有通路添加进去

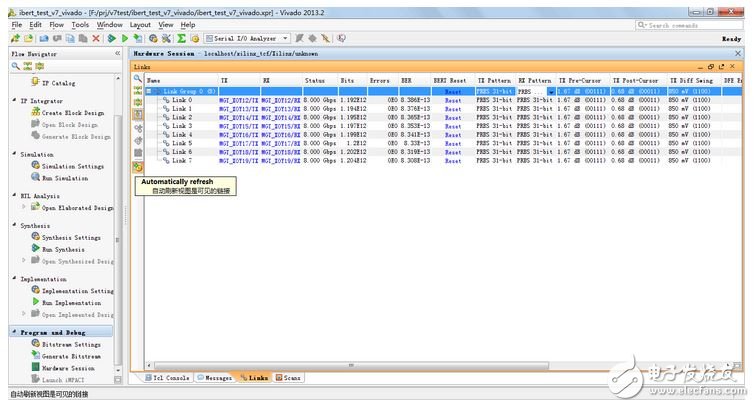

15. 点击Next

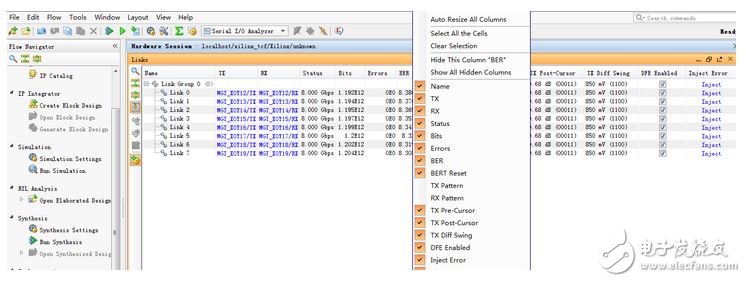

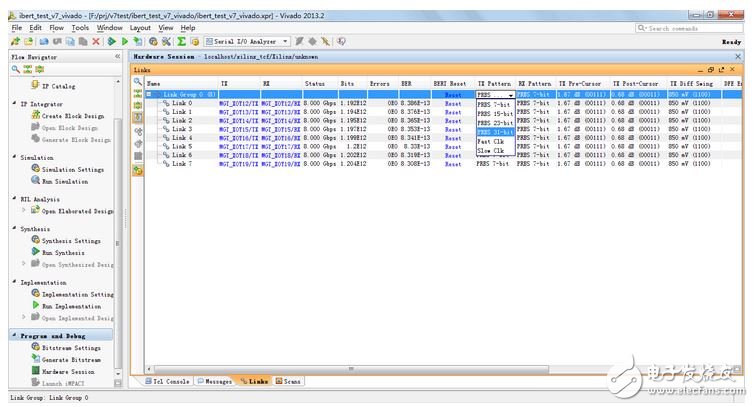

16. IBERT 界面

17.可将光标放在BERT栏上右键,就可以弹出菜单,根据需要添加或减去功能

18.将TX Pattern 和RX Pattern选为31 bit与IP中设置相符

19. 点击AUTO REFRSSH可以看到各个通道的速率变化

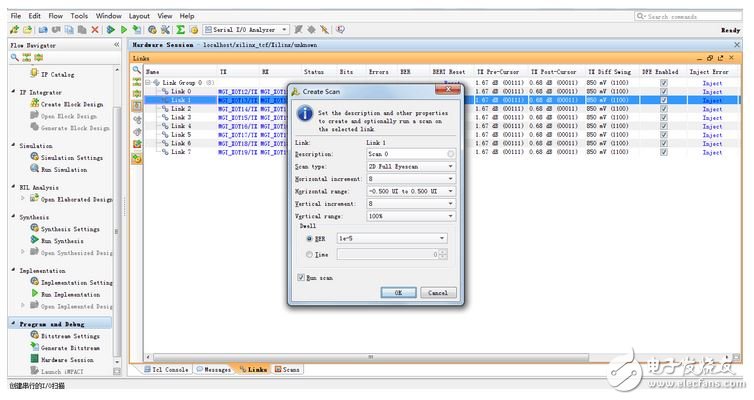

20. 选择一路通道,右键选择create scan可以创建眼图。

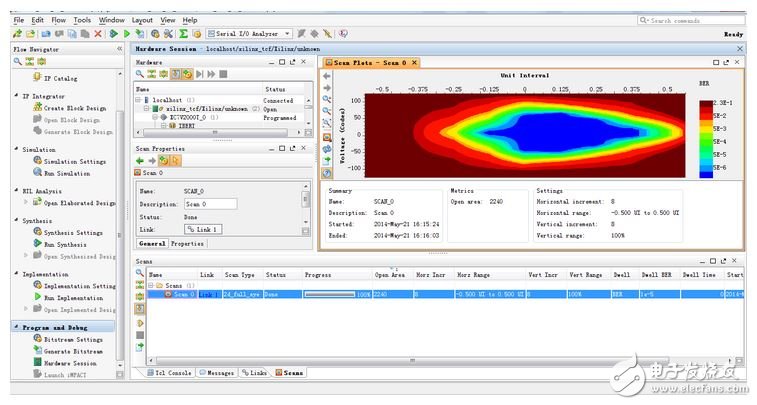

21.眼图

-

fpga开发板使用教程之在K7上用Ibert实现基本的GTX测试2020-12-31 9418

-

labview生成安装包,无法写入配置文件2016-07-25 9556

-

如何使用IBERT生成眼图2020-05-22 5459

-

利用 IBERT 进行 GTX 信号眼图测试 精选资料分享2021-07-20 1287

-

利用IBERT核对GTX收发器板级测试2023-06-21 2132

-

ICD配置文件的详细介绍和配置内容的详细概述2018-06-02 19621

-

VARON IP的生成、连接、嵌入2020-10-25 2312

-

关于利用IBERT核对GTX收发器板级测试的原理与过程详解2021-05-02 7970

-

如何使用管脚配置软件PinMux生成CC3200 GPIO口使用文件2021-11-30 788

-

基于IBERT的GTX数据传输测试2023-08-31 4848

-

linux修改网卡ip配置文件2023-11-17 3812

-

php的配置文件是什么2023-12-04 2476

-

labview的opc生成配置文件2023-12-26 3614

-

labview生成exe文件如何配置文件2023-12-27 4007

-

高速串行总线系列-IBERT使用介绍2024-12-20 4266

全部0条评论

快来发表一下你的评论吧 !