基于FPGA的DDR3用户接口设计技术详解

FPGA/ASIC技术

描述

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了适用于该背景的控制状态机,并对控制时序作了详尽的分析。系统测试结果表明,该设计满足大容量数据的高速率存储和读取要求。

一、引言

随着软件无线电[1]思想的提出和FPGA技术[2]的不断发展,高速实时数字信号处理[3]已经成为FPGA的一个重要课题,高速的采样频率带来的是大容量的存储数据。在存储芯片领域,DDR3以较低的功耗,较快的存储速度,较高的存储容量和较低的价格迅速占领市场;同时在绘制PCB板图时,DDR2对信号完整性[4]的要求比较高,在很多地方都要求T型连接;而DDR3引入了write leveling的模块[5],专门用于各个模块间时钟的对齐,因此可以采用菊花链的连接方式,大大方便了PCB互联设计[6]。因此,在FPGA中使用DDR3进行大容量数据的存储是一种趋势。

本文基于Xilinx 公司的Virtex-6芯片,针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,利用官方提供的IP核完成了用户接口设计,并在该芯片上完成了验证和实现。目前,该方案已经在某雷达系统的高速数据缓存中得到了应用。

二、系统模型

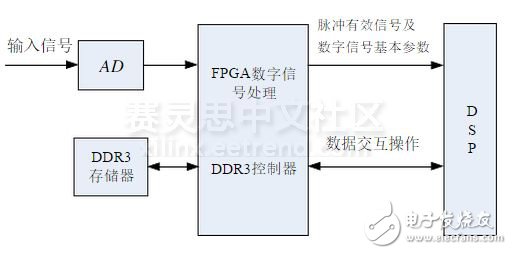

现假定背景是数字信号处理,由FPGA和DSP共同完成,FPGA主要完成数据的实时检测和初步处理,同时负责采集和存储原始数据。DSP主要负责信号的进一步处理。DSP的实时处理能力有限,那么就需要FPGA把感兴趣时间段的数据存储下来,再由DSP一包一包地从中读取并进一步处理。其基本框图如下:

图1 系统背景框图

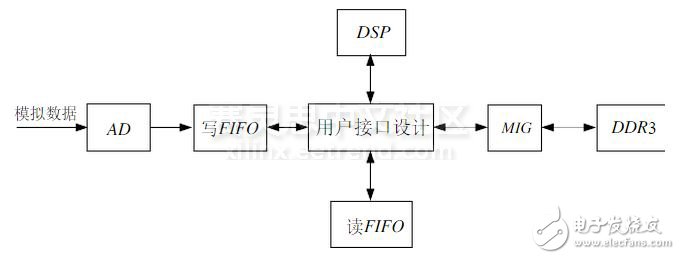

在这里我们主要讨论DDR3的控制,提取感兴趣的模块可以得到简化的框图:

图2 DDR3用户接口设计整体框图

用户接口设计是整个系统的核心,对整个系统进行调度和控制。当接收到DSP写命令的时候,该设计开启写FIFO缓存功能,将对应数据按照MIG的时序要求写入DDR3;当接收到DSP读命令的时候,该设计按照要求产生对应的MIG读时序,控制数据进入读FIFO,进而完成后续操作。

三、MIG时序要求

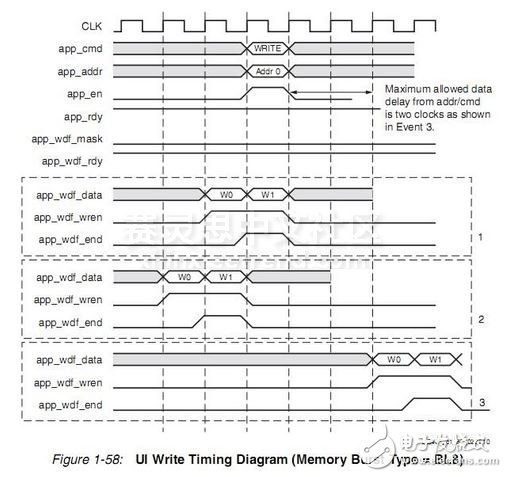

Xilinx MIG v3.7 IP核的一般写命令操作时序[7]如下图所示:

图3 MIG用户接口的时序要求(突发长度为8)

由以上时序图可以得到连续写命令的控制要点:

1、 当app_rdy(DDR3核准备好信号)和app_en(DDR3核使能信号)同时拉高的时候, 写命令和写地址有效。

2、 当app_wdf_rdy(DDR3写FIFO准备好信号)和app_wdf_en(DDR3写FIFO使能信 号)同时拉高的时候,写入数据有效。

3、 突发长度为8时每两个控制周期对应一组突发数据,则每写入两个数据就要给出一个 app_wdf_end(帧尾信号)。

4、 写命令与写数据的操作时序要在两个时钟周期以内。

四、用户接口设计及时序分析

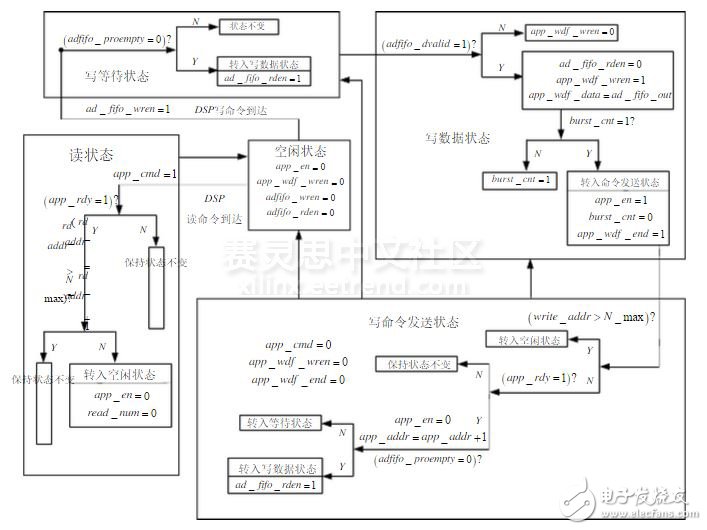

由上面MIG操作时序要求提出基于等待的写命令写数据同时发送机制。这种方式有一个好处:数据基本不会留在DDR3的FIFO里面,这样,就不用考虑app_wdf_rdy会拉低的情况,方便了写数据的操作,提高了时钟利用率。其基本思路如下图所示:

图4 基于MIG的用户接口设计基本框图

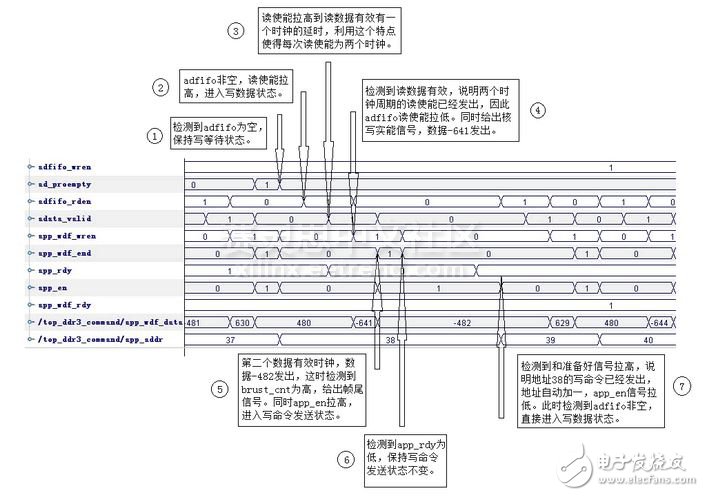

由上图设计的状态机所得的时序如下图所示:

图5 用户设计时序图

时刻①写等待状态,此时检测到ADFIFO为空,因此保持写等待状态。

时刻②检测到ADFIFO非空,于是读使能拉高,下一个状态为写数据状态。

时刻③已进入写数据状态,此时检测adata_valid(ADFIFO数据有效信号),因为读使能拉高到读数据有效有一个时钟的延时,因此当检测到adata_valid有效再使得adfifo_rden(ADFIFO读使能)拉低的话,读使能已经有效了两个时钟了。此时并没有检测到ADFIFO数据有效信号,状态不变继续检测。

时刻④检测到读数据有效,说明两个时钟周期的读使能信号已经发出,于是读使能拉低,同时拉高app_wdf_wren(DDR核写使能信号),将对应数据发出。

因为有两个时钟的有效数据,时刻⑤adata_valid依然拉高,继续写入数据;此时检测到brust_cnt(帧尾计数标志)为高,给出帧尾信号,同时app_en(核使能信号)拉高,准备发送写命令,下一个状态为写命令状态。

时刻⑥已进入写命令状态,这时app_en已经拉高,只要检测到app_rdy(核准备好信号)拉高,说明对应地址的写命令已经发出。时刻⑥检测到app_rdy为低,状态不变,继续检测。

经过连续几个时钟周期的等待后,时刻⑦检测到app_rdy为高,说明对应地址的写命令已经发出,地址自动加一,同时app_en信号拉低,再次进入写等待状态。

时刻①到时刻⑦详细描述了当接受到DSP写命令时用户接口设计对各个端口的时序操作,可见与MIG要求时序相符。

读命令的发送和写命令的发送类似,也比较简单,在此不再赘述。

五、结论

使用Xilinx公司生产的Virtex-6芯片进行验证,采样速率为1Ghz,采样位宽为12位,扩展成16位后进行存储,DDR3内部以1067M处理速度,32位的处理带宽进行存储,写数据时从地址全0写到地址全1,读数据时也从地址全0读到全1,经对比无误,说明该控制器能够较好地进行高速读写操作。

Virtex-6

DDR3

FPGA

高速实时数字信号处理

-

基于FPGA的DDR3多端口读写存储管理设计2024-06-26 844

-

基于AXI总线的DDR3读写测试2023-09-01 7792

-

FPGA学习-DDR32022-12-21 5645

-

DDR3基础详解 精选资料推荐2021-07-28 2158

-

如何实现FPGA和DDR3 SDRAM DIMM条的接口设计?2021-05-07 1912

-

与Kintex 7的DDR3内存接口2020-04-17 2009

-

Kintex-7 325T FPGA DDR3控制器和接口演示2018-11-30 6552

-

基于FPGA的DDR3用户接口设计2018-08-30 4540

-

基于FPGA的DDR3 SDRAM控制器的设计与优化2018-08-02 5092

-

Stratix III FPGA的特点及如何实现和高速DDR3存储器的接口2018-06-22 4627

-

基于FPGA的DDR3协议解析逻辑设计2017-12-05 1479

-

基于FPGA的DDR3多端口读写存储管理的设计与实现2017-11-18 8183

-

基于FPGA的DDR3 SDRAM控制器用户接口设计2017-11-17 4161

全部0条评论

快来发表一下你的评论吧 !