支持25G/28G背板运作 FPGA实现TB级网络应用突破

FPGA/ASIC技术

描述

早在两年前IEEE报告就指出,2015年通讯网络的传输容量要求将达1Tbit/s,到2020年更必须支持到10Tbit/s。 该报告还指出,2015年固网和行动网络装置数量将多达一百五十亿台,其中还包含机器对机器(M2M)的互连;在光传输网络(OTN)应用方面,核心节点的每波长带宽到2015年预计达到100G?400G,到了2020年更会提升到400G~1T。

新型FPGA可满足1Tbit/s应用

为了满足TB级的网络应用,市场上推出UltraScale All Programmable现场可编程门阵列(FPGA),该组件可支持1Tbit/s系统的建置,且具理想效能、系统整合度和高带宽,广泛适用于有线通讯、量测、航天国防及数据中心等各种应用。

事实上许多公司早已表示对1TB网络应用的需求,希望收发器能直接驱动25G/28G背板,进而解决布线性(Routability)、串音(Crosstalk)、差动式馈入损耗(Differential Insertion Loss)和阻抗匹配(Impedance Matching)等问题。

新款FPGA可以克服以上问题,且毋须使用复位时器,即可提供25G/28G背板操作,进一步支持各种1Tbit/s应用。

图1 在高层次TB级系统概念图中,多个低于1Tbit/s的支路板与一个1Tbit/s的线卡进行讯号传输。

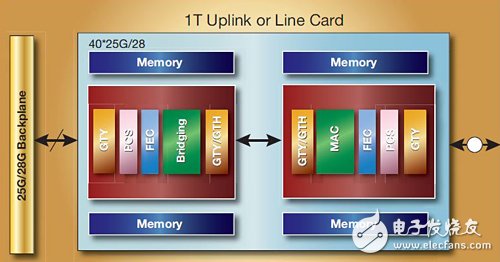

图1是通用的1Tbit/s系统高层次模块图。其中,多个带宽低于1TB的支路板(图1中有两个)透过运行速率为25G/28G的背板与一个1T线卡相连。 图2、3和4则为三种1Tbit/s以太网络和OTN可能应用的模块图,全都以新型FPGA为基础。

图2 多个低于1Tbit/s的以太网络支路板透过25G背板链接对1TB以太网上行链接模块传输讯号。

25G背板收发器战胜可布线性问题

从上述的模块图可以了解,若没有支持25G/28G的背板收发器,则难以实现各种1T网络应用。而若只有一个仅具备10G连结的背板,则会产生布线性、串音、差动式馈入损耗,甚至是阻抗匹配等问题。

可布线性问题

这些实例展示以总带宽为40×25Gbit/s =1Tbit/s的速率,在25G/28G背板上运行的四十个通道。背板厚度通常约0.25英吋,其主要取决于两个因素:连接器压装的机械及支持多个通道路由的需求。

图3 1TB以太网上行链接模块在OTN链接上分布有效载负,透过25G/28G背板连结重复使用既有的OTN线卡(<1Tb)。

若背板接口仅支持10Gbit/s的运作,通道数就须要增加到原来的2.5倍,每个1Tbit/s线卡和支路板的背板通道数量会从四十个增加到一百个。在需要二十五个支路板和线卡的系统中,最终所需的通道总数则为100×25=2,500,会为路由造成很大的问题。

图4 1TB OTN线卡透过28G背板连结重复使用从低于1TB OTN支路模块传送的讯号。

使用背板介电材料时,以Megtron-6为例,其介电常数约为3.65且标准导线宽度为7mil,使用者会发现每个差动式带状线对的堆栈高度为:每100奥姆(Ω)的差动奇模阻抗对应16mil。

假设背板连接器间距通常是2毫米(mm),就是每层连接器的引脚间可以建置一个通道。因此,背板每层能够在每个连接器支持十个通道(发送+接收)的作业。

如果以25Gbit/s的速率运作,通常需要十六个布线层,背板总厚度为16mil×16布线层=0.256英吋。如果是10Gbit/s的运作速率,则厚度为0.640英吋(16×2.5=40布线层,背板总厚度为16mil×40层=0.640英吋)。

但是,背板最大厚度通常由通路孔的深宽比决定,典型通路孔直径为15mil,标准深宽比为25:1,代表背板厚度上限约为 14×25=350mil。因此,10G背板无法支持1T应用。

串音问题

对1T应用而言,相较于10G背板,25G背板的另一个关键优势是串音效应。串音通常是通道距离太近所引起,背板通道越多,串音的机率就越高。因此,比起拥有两千五百个10G通道的背板,拥有一千个25G通道的背板较不会有串音问题。

但是大多数介电材料并不完全同质,因此会有远程串音(FEXT)效应。而在背板连接器周围的通路孔区域发生的通常为远程串音。

由于背板系统的串音问题可以同时是近端串音(NEXT)和远程串音效应,系统设计师必须留意要降低与总噪声预算相关的串音噪声成分。

事实上敏感组件和干扰源网络之间均存在互电容电场(Cm)与互感磁场(Lm)。互感会在与干扰源网络相对的敏感组件线路上感应产生电流(冷次定律);互电容会通过互电容传递在敏感组件线路上的双向电流,而近端和远程敏感组件线路上的电流会一起产生近端串音和远程串音效应,如公式1。

I(Next)=I(Cm)+I(Lm) while I(Fext)= I(Cm)–I(Lm) ................................公式1 近端串音都是正数的;远程串音可以是正数,也可以是负数。

差动式馈入损耗

通道的馈入损耗是建立可靠连结时的重要参数。馈入损失取决于两个因素:连接器损耗和介电损耗,使用Megatron-6等介电材料时,切线损耗为0.004,图5显示1公尺长走线的馈入损耗,表面粗糙度为1微米(超低截面)。

由于背板的最大厚度为0.350英吋,10G背板的走线宽度已经降到只有3mil,以允许差动奇模阻抗维持100奥姆的情况下,在0.350英吋厚的背板上铺四十层布线。另一方面,25G背板的走线宽度为7mil,可在最大厚度为0.350英吋的背板上铺十六层布线。 图5所显示的10G背板的差动式馈入损耗高于25G背板,是因为10G背板在最大背板宽度内增加布线层数,所以导致走线宽度变窄。

图5 25G和10G背板分别在各自的奈奎斯特频率(Nyquist Frequency)中显示馈入损耗。

新式的FPGA组件毋须使用复位时器即可支持25G/28G背板的操作,进而支持各种1Tbit/s的应用。这些将要上市的1Tbit/s应用要求接收器能够直接驱动25G/28G背板,以解决布线性、串音、差动式馈入损耗和阻抗匹配问题。因为过多的布线层数、更大的连接器和通路孔深宽比相关的可靠度问题都会产生某种程度的影响。

由于背板复位时器是一项附加组件,须建置在线卡和支路板上,所需的电压调节模块、配电网络、直流阻断器和参考频率都会占用印刷电路板(PCB)空间。由此可知,使用外部复位时器除会产生可靠性问题,还会占用大量且耗费成本的PCB板空间。

- 相关推荐

- 热点推荐

- FPGA

-

25G SFP28 BIDI光模块介绍2024-11-11 1291

-

25G 以太网SFP28光模块解决方案2017-10-25 3692

-

25G SFP28光模块专题:25G SFP28光模块产品、应用及解决方案介绍2017-11-10 5614

-

什么是28G光模块?介绍28G光模块各项参数2018-04-08 4028

-

产品:25G-SFP28 LR光模块PK 25G-SFP28 SR光模块2018-04-09 5494

-

介绍:两款常见的25G SFP28G光模块2018-04-24 10226

-

25G SFP28 1310nm-10km光模块怎么样?好不好?-易飞扬Gigalight2018-05-03 3899

-

讲解25G SFP28光模块的优势及特征2018-07-18 4478

-

电信级25G CWDM 光模块技术要求有哪些?2020-04-30 3352

-

易飞扬25G/100G AOC系列助力数据中心光互连2020-06-05 2236

-

25G全系列产品解决方案2021-10-28 1518

-

25G SFP 28 LR高性价比的光模块?2019-08-05 10714

-

25G BIDI光模块的解决方案分析2019-11-13 7503

-

25G/28G重定时器与转接驱动器在常见应用中的最优化实现2024-09-06 288

-

易飞扬25G SFP28 ZR,突破25G传输距离2024-11-29 742

全部0条评论

快来发表一下你的评论吧 !