搭配最佳供电序列方案 FPGA系统电源管理效率大增

FPGA/ASIC技术

描述

设计现场可编程闸极数组(FPGA)时,供电序列为重要考虑因素。由于设计需求可能介于三轨至十轨以上,FPGA厂商通常会明定电源序列要求。若遵循建议的电源序列,即可避免启动时产生过量电源,进而避免装置受损。系统内共有数种方式可达成供电序列,本文将说明依据系统需求复杂程度高低,能够采用的各种序列解决方案。

序列解决方案 提高FPGA能效

本文介绍的序列解决方案包括:

1.将PGOOD接脚串接为启动接脚

2.使用重置芯片排

3.模拟电源恢复/切断序列器

4.具备电源管理总线(PMBus)接口的数字系统健康监控器

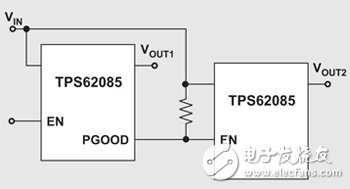

方法一:将PGOOD接脚串接为启动接脚

若要以基本且符合成本效益的方式排序,可串接某一电源的PG接脚,做为下一次序列供电的启动接脚(图1),达到PG门坎(通常指电源达到九成终值)后,第二电源就会启动。这项方式成本较低,但无法轻易操控时间,若在EN接脚增加电容,即可在各级之间加上时间差,不过在温度变化与电源重复循环时,这项方式并不可靠。此外,本方式并不支持电源切断序列。

图1 将PGOOD接脚串接为启动接脚

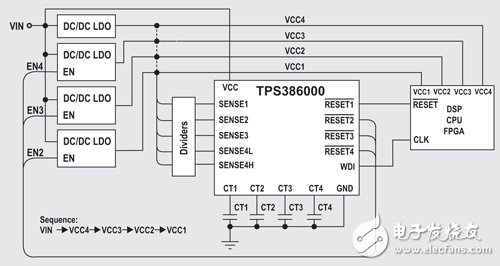

方法二:使用重置芯片排序

对于电源恢复排序而言,另一项简易方式为重置芯片与时间差。重置芯片监控门坎限制紧密的电源轨,一旦电源轨距离终值只剩3%以下,重置芯片将进入由解决方案设定的等候期,再启动下一轨。只要使用EEPROM或外部电容,即可将等候期纳入重置芯片编程,一般多信道重置芯片(图2),在电源恢复排序时使用重置芯片,能够监控解决方案。

图2 以多重输出重置芯片达到电源恢复排序

由于系统将确定每一轨都保持在稳压范围内,才会启动下一轨,故变电器不须具备PGOOD接脚,不过重置芯片序列解决方案并不适用于电源切断排序。

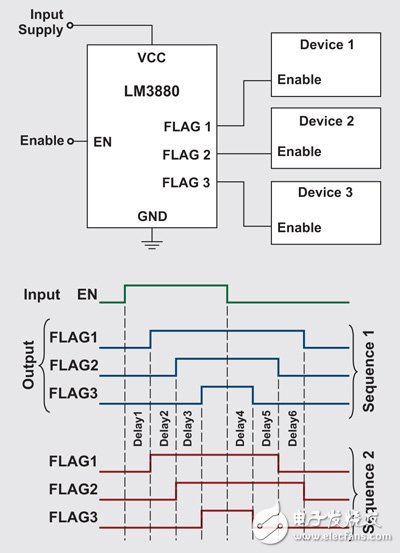

方法三:模拟电源恢复/切断序列器

电源恢复排序通常比电源切断排序简单,若要同时达成两者,可使用简易模拟序列器(图3),翻转(序列一)或混合(序列二)相对于电源恢复序列的电源切断序列,电源恢复时,在EN升高之前,所有旗标都会保持低点,EN达标后,随着内部频率通过,每一旗标依序进入漏极开路(须提升电阻)。电源切断序列与电源恢复相同,只是顺序相反。

图3 模拟电源恢复/切断序列器

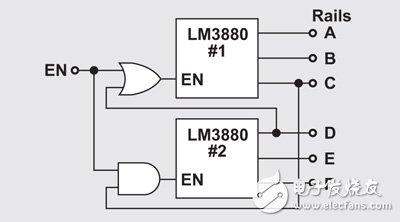

.串接多个序列器

序列器串接在一起后,可支持许多电源轨,并且在Enable讯号之间提供固定或可调整的延迟时间,以图4来说,两项序列器串接在一起,以建置六条序列轨,电源恢复时,唯有AND闸极接收到EN讯号及启动C轨后,第二序列器才会启动;电源切断时,AND闸极确保不论C输出情况如何,第二序列器都会见到EN负缘。OR闸极确保第一序列器随EN正缘启动,电源切断时,OR闸极确保在D降下之前,第一序列器都不会见到EN负缘,此举可达成电源恢复与电源切断序列,但未提供监控序列。

图4 串接多个模拟序列器

.监控电源恢复/切断排序

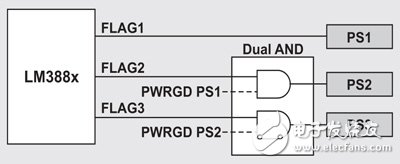

只要在图5的FlagX输出与PG接脚之间,加入数个AND闸极,即可在图4的线路中增加监控排序。在本案例中,PS1必须超过终值的90%,PS2才会启动,如此可达到低成本的监控排序解决方案。

图5 在简易频率序列器内增加监控排序

方法四:具备PMBus接口的数字系统健康监控器

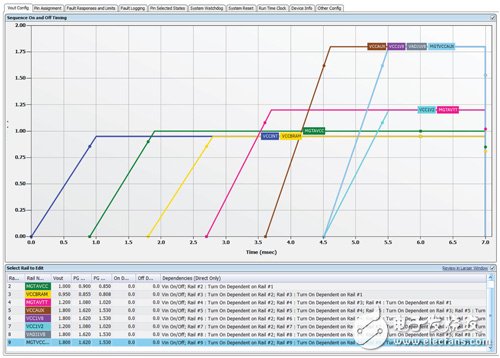

若系统要求最大弹性,PMBus/I2C兼容的数字系统健康监控器就很适用,以UCD90120A为例,设计人员可自行配置斜升/斜降时间、开关延迟、序列依赖、电流与电压监控等,满足最大序列控制需求。

数字系统健康监控器若结合图像使用接口(GUI),可搭配其他系统参数,为电源恢复/切断序列编程(图6),有些数字系统健康监控器亦具备非挥发性错误与峰值记录功能,在电源耗弱情况下协助系统故障分析。

图6 使用UCD 90120A GUI的电源恢复序列范例

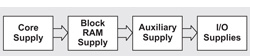

赛灵思(Xilinx)等FPGA厂商在产品说明书内,均提供建议或必要电源恢复序列,使用者可自网上取得,各家厂商的序列要求不一,即便是同家厂商,不同FPGA系列产品的要求也各异,产品说明书也会列出斜升及关闭的时间点要求,而建议电源切断序列则通常与电源恢复序列相反。图7为电源恢复序列范例。

图7 FPGA电源逻辑序列范例

多项序列解决方案均可配合FPGA厂商提出的要求,除了电源恢复与电源切断序列之外,系统要求也可能包括电源监控,不过最理想的FPGA电源解决方案仍取决于系统复杂度与规格。

- 相关推荐

- 热点推荐

- FPGA

-

如何为FPGA选择合适的电源管理方案呢2021-10-29 1375

-

篇1:如何为FPGA选择合适的电源管理方案2021-10-23 835

-

远程电源管理的解决方案2020-12-31 4166

-

为FPGA供电的最佳解决方案2019-12-11 3637

-

基于FPGA应用设计优秀电源管理解决方案2019-05-05 2785

-

寻找为FPGA供电的最佳解决方案并不简单啊,这里有解决方案!2019-03-14 3381

-

最佳SSD电源选择方案2018-11-28 4282

-

给Altera Arria 10 FPGA和Arria 10 SoC供电:经过测试和验证的电源管理解决方案2018-10-29 2751

-

适用于FPGA、GPU和ASIC系统的电源管理2018-10-15 1574

-

FPGA电源系统设计2018-09-07 2697

-

怎样为FPGA选择最合适的电源管理方案?2018-08-27 2482

-

TI PMIC 集成电路管理 加快您的 FPGA 系统设计2017-04-18 1342

-

Maxim为三款Xilinx FPGA参考设计提供电源管理方案2017-02-10 1373

-

基于FPGA直接序列扩频系统的设计2016-01-04 630

全部0条评论

快来发表一下你的评论吧 !