用Xilinx Vivado HLS可以快速、高效地实现QRD矩阵分解

FPGA/ASIC技术

描述

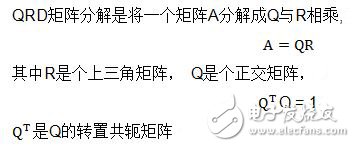

在数字信号处理领域,如自适应滤波、DPD系数计算、MIMO Decoder等,常常需要矩阵解方程运算以获得其系数,因此需对矩阵进行求逆运算。然而,由于直接对矩阵求逆会导致庞大的运算量,所以在实际工程中往往需要先将矩阵分解成几个特殊矩阵(正规正交矩阵或上、下三角矩阵以求其逆矩阵需要更小的运算量)的乘积。目前,QRD矩阵分解法是求一般矩阵全部特征值的最有效且广泛应用的方法之一。它是将矩阵分解成一个正规正交矩阵Q与上三角形矩阵R,称为QRD矩阵分解。

由于浮点具有更大的数据动态范围,所以在众多多算法中具有只需要一种数据类型的优势,所以很多QRD矩阵分解是基于浮点数据类型的。不过在通信应用中,更多的场景还是复数类型。因此,随着通信技术的日益发展,算法的复杂度越来越高,QRD矩阵的维度也越来越大。如果是用传统的手写RTL,浮点复数超大维度QRD矩阵分解的FPGA实现将变得非常复杂,需要很长的时间来编写RTL代码、仿真和进行验证等工作,使得开发效率不是很高。

本文将介绍如何使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者对算法FPGA的实现难度。其中包括:

使用VivadoHLS开发效率比手写RTL实现快5-10倍,而实现的FPGA资源效率与手写RTL接近

由于C/C++仿真验证比传统FPGA RTL要快100倍,Vivado HLS实现可以大大缩短用户的代码开发时间和仿真验证时间,从而大幅提高生产效率。

1. Vivado HLS工具介绍

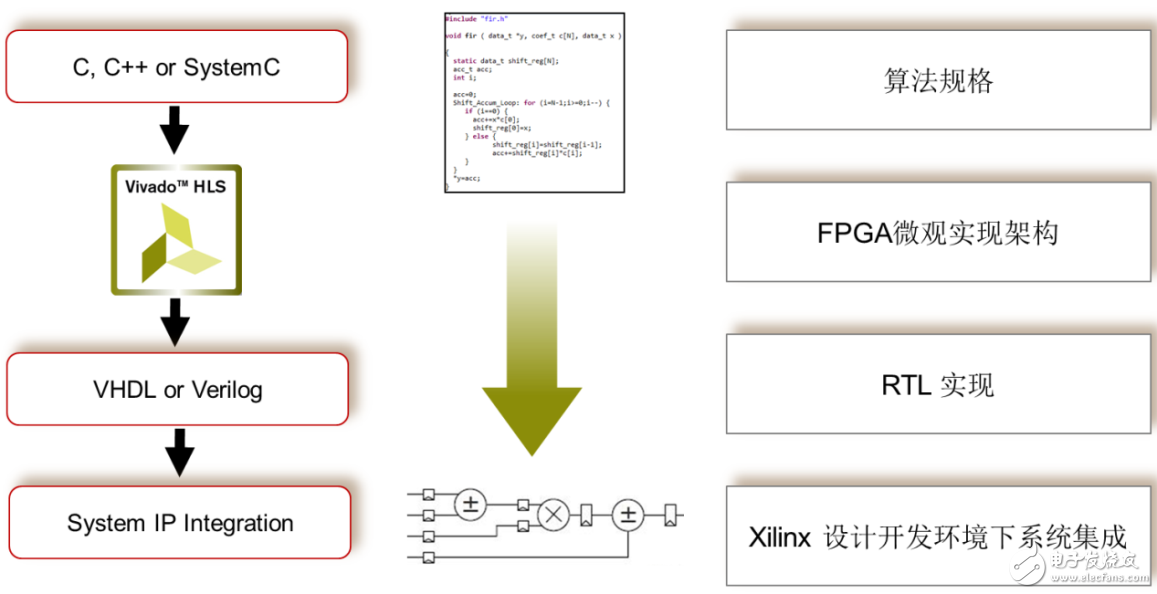

Vivado HLS是Xilinx公司2010 年收购AutoESL 以后重新打造的高层次综合工具,它可以让用户通过添加适当的directives(制导语句)和constrains(约束), 将其C/C++/System C代码直接转换成FPGA RTL(Verilog, VHDL, System C)代码。让用户可以在算法开发环境而非通常的硬件开发环境中只需专注于算法规格和算法的C实现,Vivado HLS工具会自动考虑FPGA微观实现架构,并可生成可综合的FPGA RTL代码。如图1所示。

图1 Vivado HLS设计介绍

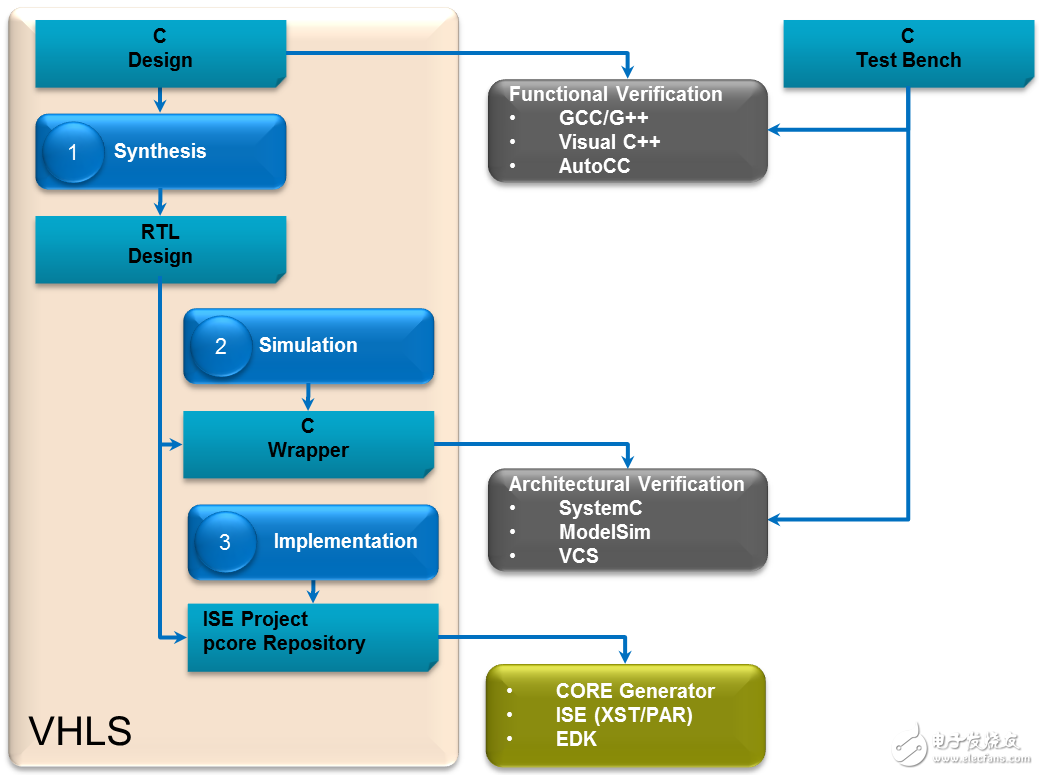

Vivado HLS FPGA设计流程:

首先用C/C++/System C将算法实现,并编写C testbench验证C的功能,确保其功能正确;

然后就可以通过Vivado HLS工具进行C 综合,将C转换成RTL;

接着做C/RTL的协同仿真(Co-simulation),以保证生成的RTL代码功能与C的功能完全一致。

最后Vivado HLS生成的RTL代码可直接用于Xilinx设计开发环境下做系统集成、仿真和生成bit文件。

如图2所示。

图2 Vivado HLS设计流程

2. QRD矩阵分解算法

3. QRD矩阵分解Vivado HLS实现C++代码构架

QRD矩阵分解C++实现代码的顶层模块是qrd_engine.cpp,它调用cal_core.cpp(核心计算函数), coef_cal.cpp(系数计算函数),以及浮点加、减、乘、除法等子函数来实现。

struct cf_t {

float re;

float im;

};

voidqrd_engine

(

cf_t in_u[(R_DIM+Y_DIM)/DIV_NUM][DIV_NUM],

cf_t pd_err_in,

float lamda,

float lamda_sqrt,

float diag[R_DIM],

cf_t r[R_DIM][X_DIM],

cf_t p[R_DIM]

)

{

#pragma HLS ARRAY_PARTITION variable=in_u complete dim=2

#pragma HLS ARRAY_PARTITION variable=r complete dim=2

//注:这里对数组加入完全分割directive,目的是提高数据的并行带宽,从而获得并行计算。

#pragma HLS RESOURCE variable=in_u core=RAM3S

//注:这里对数组加入RAM3S directive,目的是控制生成的BRAM的延迟。

-

Vivado HLS设计流程2025-04-16 1787

-

用TCL定制Vivado设计实现流程2023-05-05 2374

-

Vivado HLS设计流的相关资料分享2021-11-11 1129

-

PYNQ上手笔记 | ⑤采用Vivado HLS进行高层次综合设计2021-11-06 829

-

Vivado HLS实现OpenCV图像处理的设计流程与分析2021-07-08 5325

-

探索Vivado HLS设计流,Vivado HLS高层次综合设计2020-12-21 4628

-

XIlinx利用HLS进行加速设计进度2019-07-31 7653

-

如何创建Vivado HLS项目2018-11-20 4619

-

TCL脚本简介 vivado hls 的设计流程2018-06-05 7565

-

用Vivado-HLS为软件提速2018-03-26 777

-

用Vivado-HLS实现低latency 除法器2017-12-04 1827

-

快速高效的实现浮点复数矩阵分解2017-11-18 1405

-

Hackaday读者有话说:Vivado HLS使用经验分享2017-02-08 900

-

Vivado环境下如何在IP Integrator中正确使用HLS IP2017-02-07 4841

全部0条评论

快来发表一下你的评论吧 !