Vivado中的静态时序分析工具Timing Report的使用与规范

FPGA/ASIC技术

描述

《XDC约束技巧》系列中讨论了XDC约束的设置方法、约束思路和一些容易混淆的地方。我们提到过 约束是为了设计服务,写入Vivado中的XDC实际上就是用户设定的目标 ,Vivado对FPGA设计的实现过程必须以满足XDC中的约束为目标来进行。那么:

如何验证实现后的设计有没有满足时序要求?

如何在开始布局布线前判断某些约束有没有成功设置?

如何验证约束的优先级?

这些都需要用到Vivado中的静态时序分析工具。所以让我们来从如何读懂和用好Timing Report开始吧。

静态时序分析

静态时序分析( Static Timing Analysis)简称STA,采用穷尽的分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误并报告。

STA不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少、覆盖率极高,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计。所以STA不仅是数字集成电路设计Timing Sign-off的必备手段,也越来越多地被用到设计的验证调试工作中。

STA在FPGA设计中也一样重要,但不同于一般数字集成电路的设计,FPGA设计中的静态时序分析工具一般都整合在芯片厂商提供的实现工具中。在Vivado中甚至没有一个独立的界面,而是通过几个特定的时序报告命令来实现。

OCV与PVT

即便是同一种FF,在同一个芯片上不同操作条件下的延时都不尽相同,我们称这种现象为OCV(on-chip variation)。OCV表示的是芯片内部的时序偏差,虽然很细小,但是也必须严格考虑到时序分析中去。

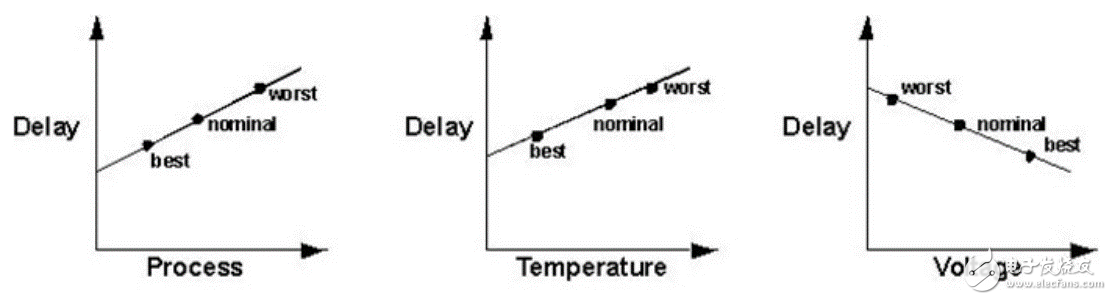

产生OCV的原因主要有PVT(Process / Voltage / Temperature)三个方面,而STA要做的就是针对不同工艺角(Process Corner)下特定的时序模型来分析时序路径,从而保证设计在任何条件下都能满足时序要求,可以正常工作。

通常PVT对芯片性能的影响如下图所示,

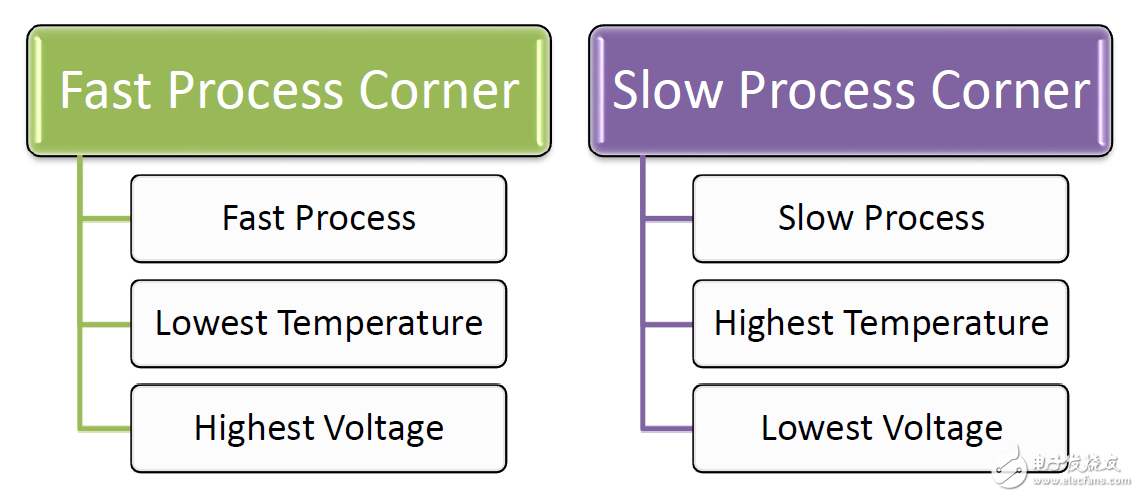

不同的PVT条件组成了不同的corner,另外在数字电路设计中还要考虑RC corner的影响,排列组合后就可能有超过十种的corner要分析。但是在FPGA设计中的静态时序分析一般仅考虑Best Case和Worst Case,也称作Fast Process Corner 和Slow Process Corner,分别对应极端的PVT条件。

Multi-Corner

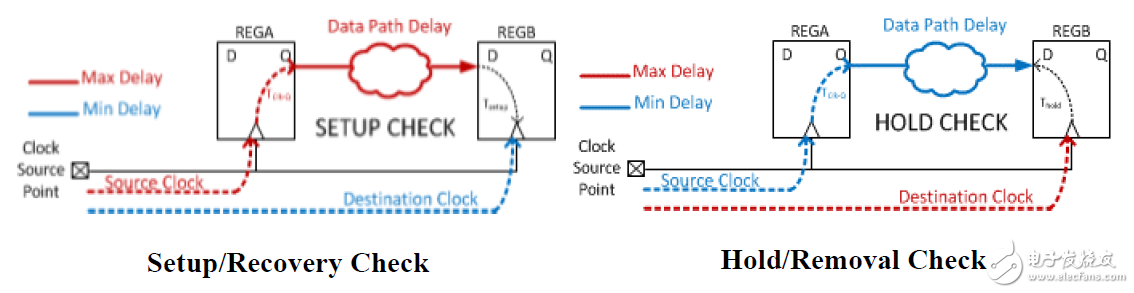

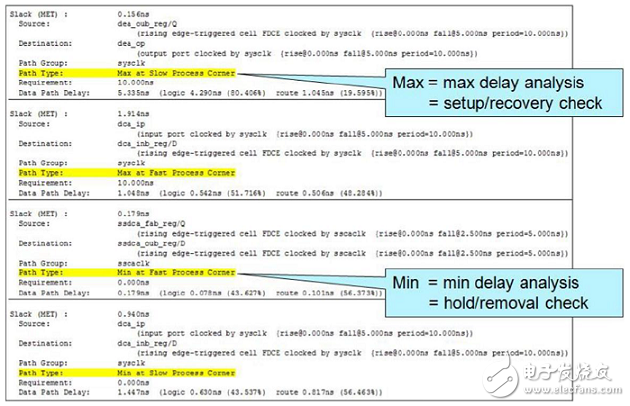

Vivado中的STA支持多角时序分析(Multi-Corner Timing Analysis),会对以上两种corner下的时序同时进行分析,然后报告最差的情况。因为每个corner下的延时也会有一定的变化范围,所以时序分析还会考虑每种corner下的最大延时和最小延时。

如果一个设计在Best Case和Worst Case下都能满足时序要求,则可以推算这个设计在其允许的任何操作条件下都能保持正常工作。

这里要提醒大家,不要被corner的名字误导,实际上,同样一条路径可能在Slow Corner中满足时序却在Fast Corner中有时序违例。但是你在Vivado中看到的时序报告只会显示其对两种corner并行分析后选出的最差情况。

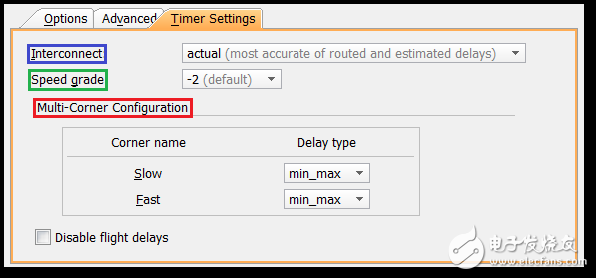

有特殊需要的情况下,可以在Vivado中通过config_timing_corners -corner -delay_type 来选择将某种corner应用于setup和/或hold的分析。在Report Timing Summary 和Report Timing的图形化界面也可以通过Timer Setting对corner做调整,具体界面详见稍后描述。

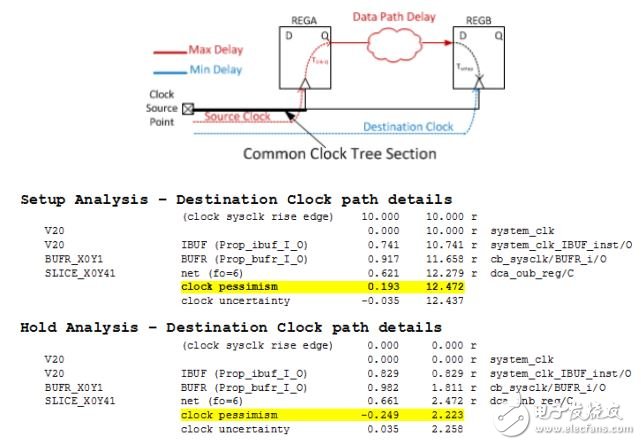

这样最大化考虑OCV的时序分析方法在处理同一条路径的共同时钟路径时也会应用不同的延时数据,从而会得出更为悲观的数据。为了真实反映路径延时情况,这部分延时必须被纠正,这就是CRPR(Clock Reconvergence Pessimism Removal)。

仔细观察时序报告便可以发现在报告路径的Slack之前有一行显示clock pessimism已经被考虑在内,在进行Setup Check时会加上一定的clock pessimism,而Hold Check时则会减去一定的clock pessimism。

下图显示了CRPR的来源以及在Vivado时序报告中的具体体现。

时序命令与报告

Vivado中用于时序分析的命令主要有以下两条,且都有对应的图形化设置界面。

report_timing_summary 主要用于实现后的timing sigh-off

report_timing 主要用于交互式的约束验证以及更细致具体的时序报告与分析

report_timing_summary

我们先看看report_timing_summary ,实际上,不仅在布局布线后,在综合后甚至是更具体的实现过程中的每一小步之后都可以运行,从而得到一个全局的时序报告。

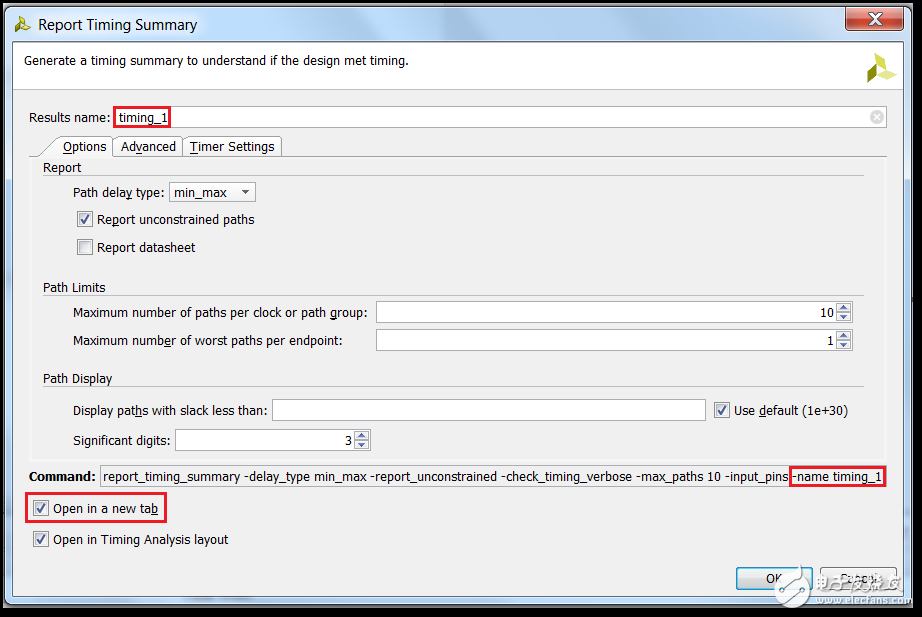

在Vivado IDE中点击Report Timing Summary后可以改变报告的内容,例如每个时钟域报告的路径条数,是否setup和hold全都报告等等。每改变一个选项都可以看到窗口下方的Command一栏显示出对应的Tcl命令。修改完设置后可以直接按OK键确认执行,也可以拷贝Command栏显示的命令到Tcl脚本中稍后执行。

这里有个小窍门,通过-name 指定一个名字,就可以在Vivado IDE中新开一个窗口显示这条命令的执行结果,这个窗口还可以用来跟其他诸如Device View或是Schematic View等窗口之间cross probing。这一点也同样适用于包括report_timing 在内的绝大部分Vivado中的report命令。

在设置窗口中还有Timer Settings一栏(report_timing中也有),可以用来改变报告时采用的具体corner、速度等级以及计算布线延时的方式。很多时候我们可以借助Timer的设置来快速验证和调试设计需求。

举例来说,在实现后的报告中显示时序违例比较严重,我们可以直接在Timer设置中改变速度等级后重新报告时序,来验证把当前这个已经布局布线完毕的设计切换到更快一档的芯片中是否可以满足时序要求。

另外,在布局布线后的设计上报告时序,往往不能更直观地发现那些扇出较大或是逻辑级数较高的路径。此时我们可以修改连线模型为estimated,报告出布局后布线前的时序而无需另外打开对应阶段的 DCP并重新运行时序报告命令来操作,这么做节约时间的同时,也更容易找到那些高扇出路径以及由于布局不佳而导致的时序违例。我们也可以修改连线模型为none,这样可以快速报告出那些逻辑延时较大以及逻辑级数较高的路径。以上这些改变Timer设置的方法可以帮助我们快速定位设计中可能存在的问题和缺陷。

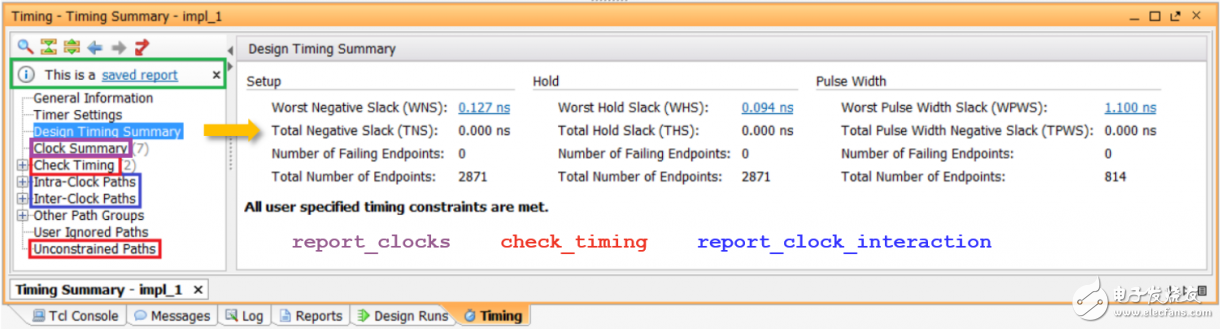

report_timing_summary实际上隐含了report_timing、report_clocks 、check_timing 以及部分的report_clock_interaction命令,所以我们最终看到的报告中也包含了这几部分的内容。另外自Vivado 2014.3版起,打开实现后的结果时会直接打开一个预先产生好的报告。

Timing Summary报告把路径按照时钟域分类,每个组别下缺省会报告Setup、Hold以及Pulse Width检查最差的各10条路径,还可以看到每条路径的具体延时报告,并支持与Device View、Schematic View等窗口之间的交互。

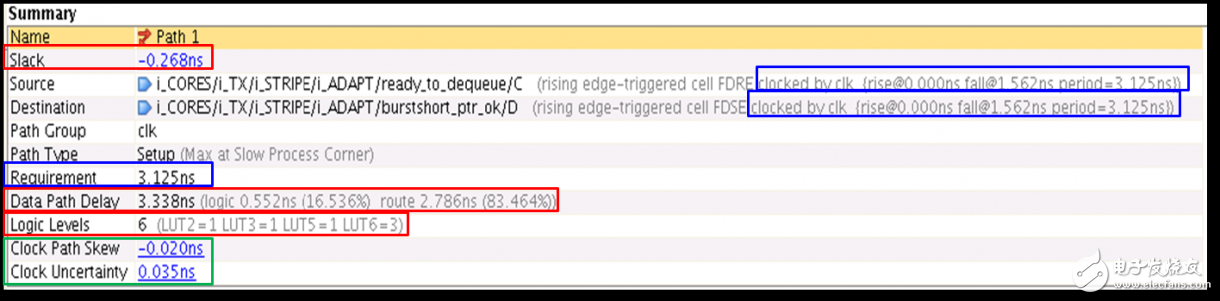

每条路径具体的报告会分为Summary、Source Clock Path、Data Path和Destination Clock Path几部分,详细报告每部分的逻辑延时与连线延时。用户首先要关注的就是Summary中的几部分内容,发现问题后再根据具体情况来检查详细的延时数据。其中,Slack显示路径是否有时序违例,Source和Destination显示源驱动时钟和目的驱动时钟及其时钟频率, Requirement显示这条路径的时序要求是多少,Data Path显示数据路径上的延时,Logic Level显示这条路径的逻辑级数,而Clock Path Skew和 Clock Uncertainty则显示时钟路径上的不确定性。

以上图这条路径来举例,通过Summary我们可以得到这样的信息:这是一条clk时钟域内的路径,时钟周期为3.125ns,这条路径有0.268ns的时序违例。违例的主要原因是逻辑级数较高导致的数据链路延时较大,但连线延时的比例也较高,所以可以仔细看看这条路径的数据路径上有没有可能改进布局、降低扇出或者是减少逻辑级数的优化方向。

report_timing

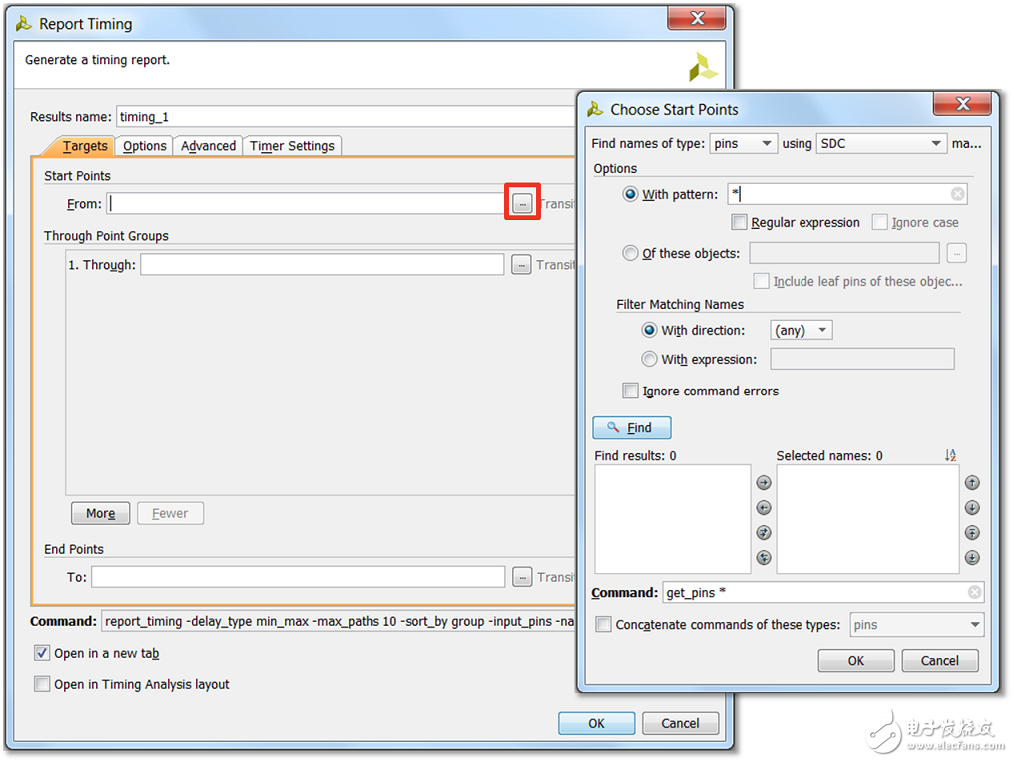

report_timing是更具体的时序报告命令,经常用来报告某一条或是某些共享特定节点的路径。用户可以在设计的任何阶段使用report_timing,甚至是一边设置XDC,一边用其来验证约束的可行性与优先级。在Vivado IDE中可以由Tools > Timing > Report Timing 调出其图形化设置窗口。

与report_timing_summary类似,调整选项后对应的Tcl命令也会在Command栏生成,在Targets一栏还可以设置需要报告路径的起始点/途经点/结束点,可以三个都设置或是仅设置其中任何一项,每一项都支持通配符匹配甚至是正则表达式查找。report_timing报告出的路径延时与report_timing_summary中具体到每根路径上的报告一致,可以以此为依据帮助我们定位时序失败的原因。

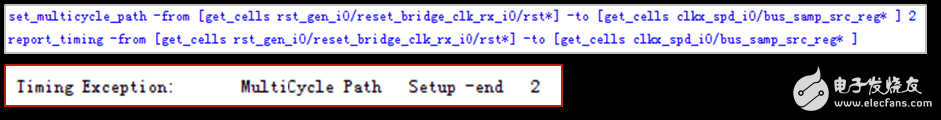

用report_timing来报告时序其实还有一些更常见的应用场景,用来帮助我们设置和验证约束,尤其是那些时序例外约束。

举例来说,在设计过程中我们约束了一条或数条多周期约束,不同于UCF必须读入约束后重跑设计,我们可以直接在Tcl Console中输入这条XDC,无需重跑设计,直接用report_timing来验证。在随之显示的时序报告Summary部分可以看到Timing Exception后列出这条路径被设置了怎样的时序例外约束(注意,不加额外option时,以下两条命令都仅针对setup check )。

单纯的一条多周期约束没有什么特别,但是如果使用了通配符后的时序例外有重叠的情况下,Vivado会根据优先级来决定对某条路径应用怎样的约束。当设计较大,XDC较多时,一边设置XDC一边用report_timing来验证就变得尤其重要。

另外,仅仅输入report_timing而不加任何option,Vivado便会报告出时序违例最严重的那条路径,方便我们快速了解当前设计的WNS,找到最差的那条路径。在验证I/O约束时也常常用到report_timing,只要指定-from 某个输入或是-to某个输出便可以快速验证当前设计在接口上的时序。

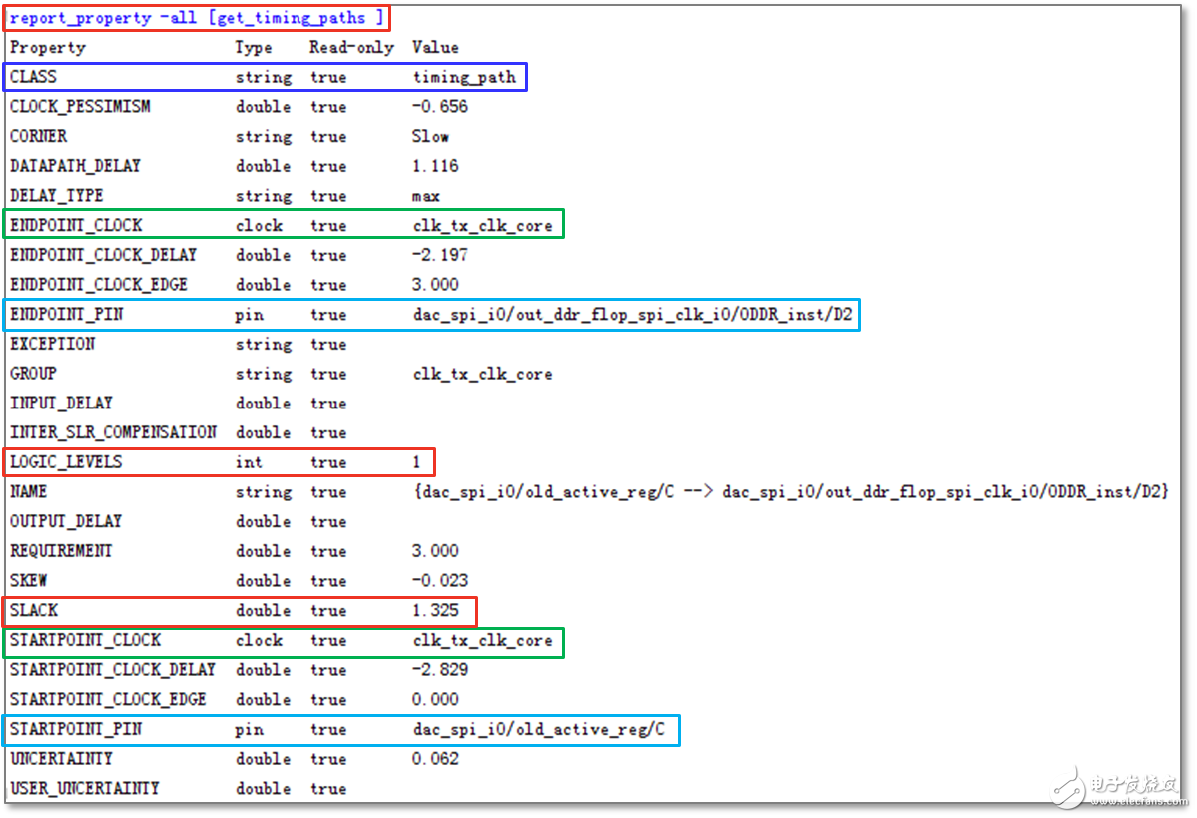

get_timing_paths

除了上述两个大家比较熟悉的时序报告命令,Vivado中还提供一个get_timing_paths的命令,可以根据指定的条件找到一些特定的路径。我们可以利用其返回值中的一些属性来快速定位设计中的问题。

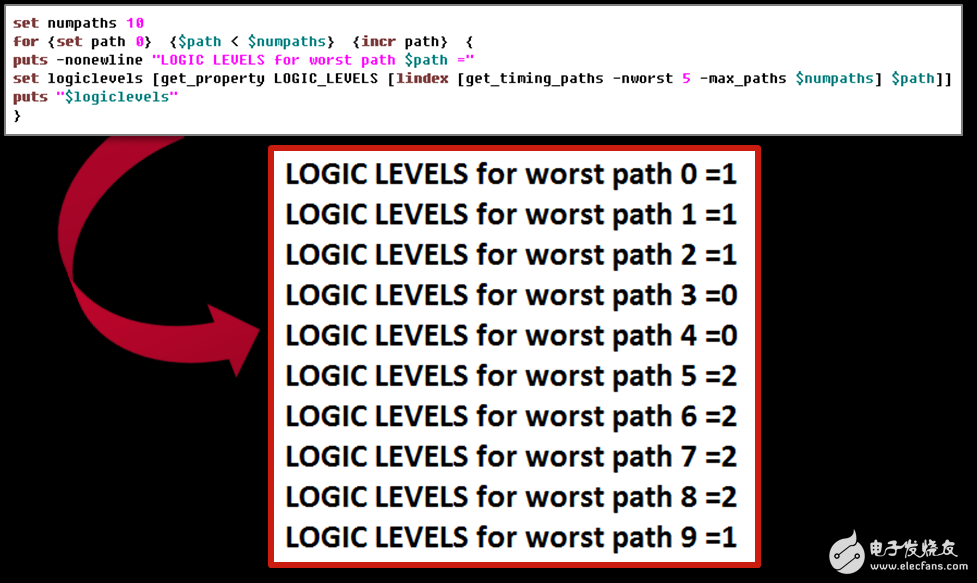

例如逻辑级数这个影响FPGA性能的一大因素,因为经常隐藏在时序报告后很难被发现。在Vivado中,除了借助综合后的报告来找到那些可能因为逻辑级数较高而导致的时序难满足的路径外,还有一个更直接的办法,可以一次性报告出设计中那些高逻辑级数的路径,方便我们有针对性的深入分析和优化。

下图这个例子报告了时序最差的10条路径的逻辑级数。需要注意的是,在综合后和在布局布线后用一样的脚本报告出的结果会稍有不同,对逻辑级数较为关注的情况,还是建议以综合后的结果为主要依据。

小结

本文可以视为对《XDC约束技巧》系列文章的补充,希望可以帮助大家了解FPGA设计中的时序分析方法,学会使用Vivado中的静态时序分析工具来验证时序,定位问题,快速找到问题和解决方案。

-

静态时序分析与逻辑(华为内部培训资料)2010-07-09 1073

-

vivado时序分析相关经验2025-10-30 465

-

vivado:时序分析与约束优化2018-08-22 9409

-

可以在Vivado时序分析器工具中指定温度和电压值来估算设计时序吗?2018-10-25 5211

-

Vivado下显示指定路径时序报告的流程2021-01-15 3635

-

静态时序分析基础及应用2016-05-09 928

-

时序分析的小工具——Global Timing Debugger2020-05-19 10281

-

Vivado时序案例分析之解脉冲宽度违例2020-11-19 7256

-

VIVADO中时序报告中WNS、WHS、TNS、THS有什么含义2021-10-21 30086

-

Vivado使用进阶:读懂用好Timing Report2023-05-04 6060

-

如何在Vivado中添加时序约束呢?2023-06-26 6609

-

什么是时序路径timing path呢?2023-07-05 3478

-

时序分析基本概念介绍—Timing Arc2023-07-06 6029

-

Vivado时序问题分析2024-01-05 4445

-

集成电路设计中静态时序分析介绍2025-02-19 2190

全部0条评论

快来发表一下你的评论吧 !