FPGA设计约束技巧之XDC约束之I/O篇 (上)

FPGA/ASIC技术

描述

《XDC约束技巧之时钟篇》中曾对I/O约束做过简要概括,相比较而言,XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要讨论的I/O约束了。

I/O 约束的语法

XDC 中可以用于 I/O 约束的命令包括 set_input_delay / set_output_delay 和set_max_delay / set_min_delay 。其中,只有那些从 FPGA 管脚进入和/或输出都不经过任何时序元件的纯组合逻辑路径可以用 set_max_delay / set_min_delay 来约束,其余 I/O 时序路径都必须由set_input_delay / set_output_delay 来约束。如果对 FPGA 的 I/O 不加任何约束,Vivado 会缺省认为时序要求为无穷大,不仅综合和实现时不会考虑 I/O 时序,而且在时序分析时也不会报出这些未约束的路径。

本文以下章节将会着重讨论 XDC 接口约束和时序分析的基础,介绍如何使用set_input_delay / set_output_delay 对 FPGA 的 I/O 时序进行约束。

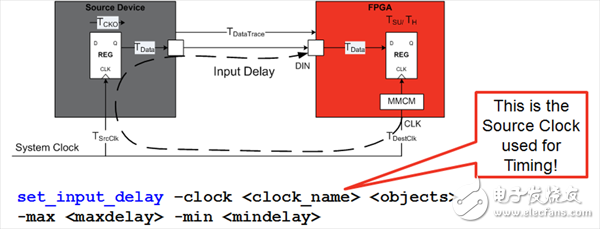

Input 约束

上图所示 set_input_delay 的基本语法中, 是想要设定 input 约束的端口名,可以是一个或数个 port;-clock 之后的 指明了对 时序进行分析所用的时钟,可以是一个 FPGA 中真实存在的时钟也可以是预先定义好的虚拟时钟;-max 之后的 描述了用于 setup 分析的包含有板级走线和外部器件的延时;-min 之后的 描述了用于 hold 分析的包含有板级走线和外部器件的延时。

上述这些选项是定义 Input 约束时必须写明的,还有少数几个可选项,如 -add_delay和 -clock_fall 用于 DDR 接口的约束。

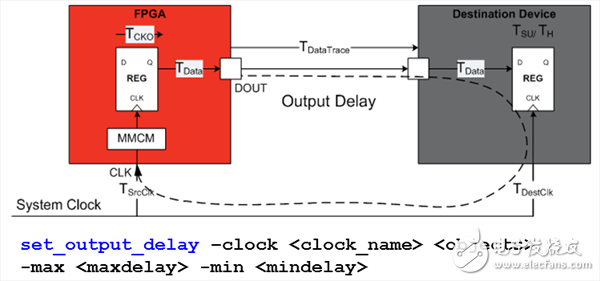

Output 约束

上图所示 set_output_delay 的基本语法中, 是想要设定 output 约束的端口名,可以是一个或数个 port;-clock 之后的 指明了对 时序进行分析所用的时钟,可以是一个 FPGA 中真实存在的时钟也可以是预先定义好的虚拟时钟;-max 之后的 描述了用于 setup 分析的包含有板级走线和外部器件的延时;-min之后的 描述了用于 hold 分析的包含有板级走线和外部器件的延时。

上述这些选项是定义 Output 约束时必须写明的,还有少数几个可选项如 -add_delay和 -clock_fall 用于 DDR 接口的约束。

Setup/Hold 时序分析

我们知道约束是为了设计服务,而设置好的约束必须在时序报告中加以验证。所以,怎样理解时序分析中的检查规则就成了重中之重,这一点对 I/O 约束来说尤为重要。理解时序分析工具如何选取路径分析的发送端(Launch)和接收端(Capture)时钟沿(Clock Edges),在 Setup 和 Hold 分析时又有怎样的具体区别,以及这些数字在时序报告中如何体现等等是设置正确 I/O 约束的基础。

更具体的时序分析方法以及如何深入解读时序报告等内容将会在后续另开主题文章详述,这里仅就 Setup/Hold 分析时对时钟边沿的选择加以描述,便于以下章节的展开。

Setup 时序分析

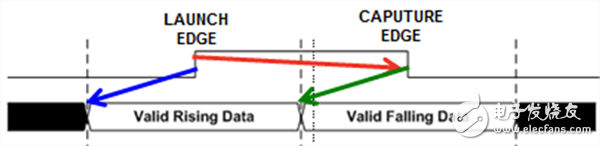

同步电路设计中,一般情况下,数据在时钟上升沿发送,在下一个时钟上升沿接收,发送的时钟沿称作 Launch Edge,接收沿称作 Capture Edge。时序分析中的 Setup Check 跟Capture Edge 的选择息息相关。

在 SDR 接口的 setup 分析中,工具如下图这样识别发送和接收时钟沿。

而在 DDR 接口的 setup 分析中,因为数据是双沿采样,所以发送和接收时钟沿变成上升(下降)沿发送,下降(上升)沿接收。

Hold 时序分析

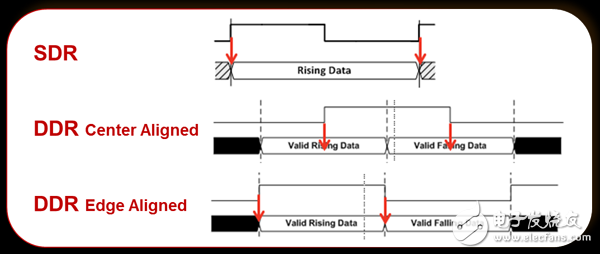

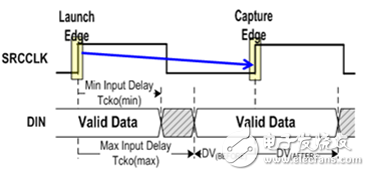

Hold Check 主要是为了保证数据在接收(采样)端时钟沿之后还能稳定保持一段时间,对 Hold 分析而言,同一个时钟沿既是 Launch Edge 也是 Capture Edge,这一点对 SDR和 DDR(不论是中心对齐还是边沿对齐)都一样。

Input 接口类型和约束

由于历史的原因,相当一部分 FPGA 设计仍然在系统中起到胶合逻辑(Glue Logic)的作用,当然,如今的 FPGA 中嵌入了高速串行收发器和嵌入式处理器等,早就不仅仅局限于系统设计的配角,反而成为了其中的主角甚至是明星。但数据接口的同步一直是FPGA 设计中的常见问题,也是一个重点和难点,很多设计不稳定都是因为数据接口的同步有问题。

FPGA 的数据接口同步根据系统级设计方式来讲可以分为系统同步和源同步两种。

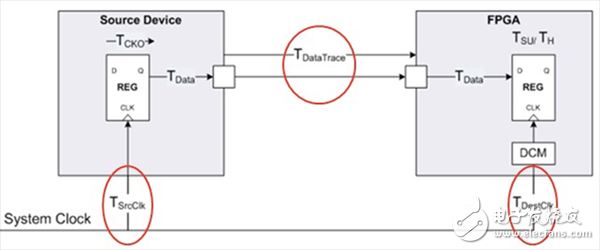

系统同步接口

系统同步接口(System Synchronous Interface)的构建相对容易,以 FPGA 做接收侧来举例,上游器件仅仅传递数据信号到 FPGA 中,时钟信号则完全依靠系统板级来同步。时钟信号在系统级上同源,板级走线的延时也要对齐。正因为这样的设计,决定了数据传递的性能受到时钟在系统级的走线延时和 skew 以及数据路径延时的双重限制,无法达到更高速的设计要求,所以大部分情况也仅仅应用 SDR 方式。

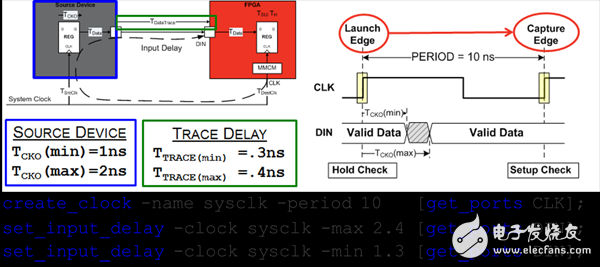

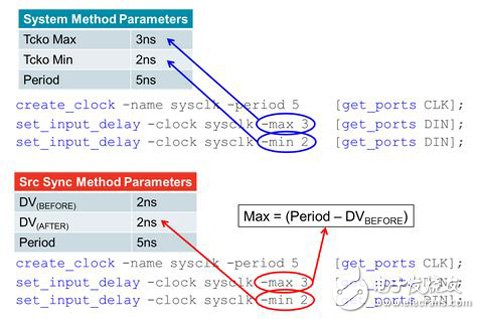

对系统同步接口做 Input 约束相对容易,只需要考虑上游器件的 Tcko 和数据在板级的延时即可。下图是一个 SDR 上升沿采样系统同步接口的 Input 约束示例。

设置和分析 I/O 约束一定要有个系统级思考的视角,如上右图所示,Launch Edge 对应的是上游器件的时钟,而 Capture Edge 则对应 FPGA 的输入时钟,正因为是系统同步时钟,所以可以将其视作完全同步而放在一张图上分析,这样一来,就可以用一般时序分析方法来看待问题。

一条完整的时序路径,从源触发器的 C 端开始,经过 Tcko 和路径传输延时再到目的触发器的 D 端结束。放在系统同步的接口时序上,传输延时则变成板级传输延时(还要考虑 skew),所以上述 -max 后的数值是 Tcko 的最大值加上板级延时的最大值而来,而-min后的数值则是由两个最小值相加而来。

源同步接口

为了改进系统同步接口中时钟频率受限的弊端,一种针对高速 I/O 的同步时序接口应运而生,在发送端将数据和时钟同步传输,在接收端用时钟沿脉冲来对数据进行锁存,重新使数据与时钟同步,这种电路就是源同步接口电路(Source Synchronous Interface)。

源同步接口最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响,所以源同步接口也经常应用 DDR 方式,在相同时钟频率下提供双倍于SDR 接口的数据带宽。

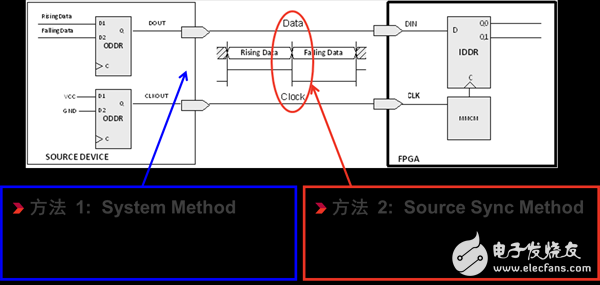

源同步接口的约束设置相对复杂,一则是因为有 SDR、DDR、中心对齐(Center Aligned)和边沿对齐(Edge Aligned)等多种方式,二则可以根据客观已知条件,选用与系统同步接口类似的系统级视角的方式,或是用源同步视角的方式来设置约束。

如上图所示,对源同步接口进行 Input 约束可以根据不同的已知条件,选用不同的约束方式。一般而言,FPGA 作为输入接口时,数据有效窗口是已知条件,所以方法 2 更常见,Vivado IDE 的 Language Templates 中关于源同步输入接口 XDC 模板也是基于这种方法。但不论以何种方式来设置 Input 约束,作用是一样,时序报告的结果也应该是一致的。

针对上图所示中心对齐源同步 SDR 接口时序,分别按照两种方式来约束,需要的已知条件和计算方式虽然不同,但却可以得到完全一样的结果。

DDR 接口的约束设置

DDR 源同步接口的约束稍许复杂,需要将上升沿和下降沿分别考虑和约束,以下以源同步接口为例,分别就输入接口数据为中心对齐或边沿对齐的方式来举例。

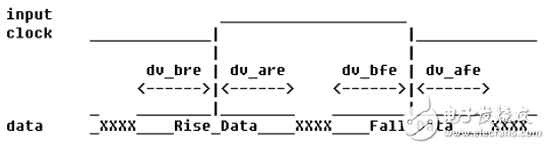

DDR 源同步中心对齐输入接口

已知条件如下:

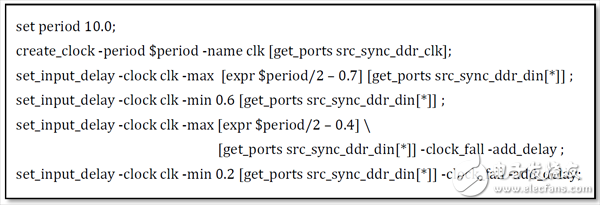

时钟信号 src_sync_ddr_clk 的频率: 100 MHz

数据总线: src_sync_ddr_din[3:0]

上升沿之前的数据有效窗口 ( dv_bre ) : 0.4 ns

上升沿之后的数据有效窗口 ( dv_are ) : 0.6 ns

下降沿之前的数据有效窗口 ( dv_bfe ) : 0.7 ns

下降沿之后的数据有效窗口 ( dv_afe ) : 0.2 ns

可以这样计算输入接口约束:DDR 方式下数据实际的采样周期是时钟周期的一半;上升沿采样的数据(Rise Data)的 -max 应该是采样周期减去这个数据的发送沿(下降沿)之前的数据有效窗口值 dv_bfe,而对应的-min 就应该是上升沿之后的数据有效窗口值dv_are ;同理,下降沿采样的数据(Fall Data)的 -max 应该是采样周期减去这个数据的发送沿(上升沿)之前的数据有效窗口值 dv_bre,而对应的-min 就应该是下降沿之后的数据有效窗口值 dv_afe 。

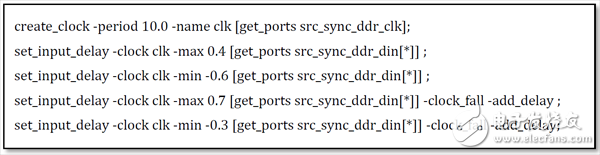

所以最终写入 XDC 的 Input 约束应该如下所示:

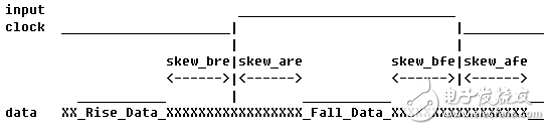

DDR 源同步边沿对齐输入接口

已知条件如下:

时钟信号 src_sync_ddr_clk 的频率: 100 MHz

数据总线: src_sync_ddr_din[3:0]

上升沿之前的数据 skew (skew_bre ) : 0.6 ns

上升沿之后的数据 skew (skew_are ) : 0.4 ns

下降沿之前的数据 skew (skew_bfe ) : 0.3 ns

下降沿之后的数据 skew (skew_afe ) : 0.7 ns

可以这样计算输入接口约束:因为已知条件是数据相对于时钟上升沿和下降沿的skew,所以可以分别独立计算;上升沿的 -max 是上升沿之后的数据 skew (skew_are ),对应的-min 就应该是负的上升沿之前的数据 skew (skew_bre );下降沿的 -max 是下降沿之后的数据 skew (skew_afe ),对应的-min 就应该是负的下降沿之前的数据 skew (skew_bfe )。

所以最终写入 XDC 的 Input 约束应该如下所示:

出现负值并不代表延时真的为负,而是跟数据相对于时钟沿的方向有关。请一定牢记 set_input_delay 中 -max/-min 的定义,即时钟采样沿到达之后最大与最小的数据有效窗口(set_output_delay 中 -max/-min 的定义与之正好相反,详见后续章节举例说明)。

在这个例子中,数据是边沿对齐,只要有 jitter 跟 skew 的存在,最差情况下,数据有效窗口在到达时钟采样沿之前就已经结束,所以会有负数出现在-min 之后。因此,在实际应用中,FPGA 用作输入的边沿对齐 DDR 源同步接口的情况下,真正用来采样数据的时钟会经过一个MMCM/PLL 做一定的相移,从而把边沿对齐变成中心对齐。

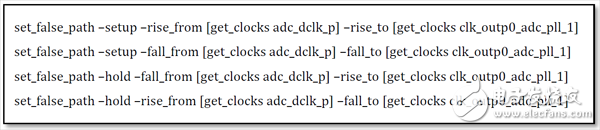

另外,在经过 MMCM/PLL 相移后的采样时钟跟同步接口输入的时钟之间需要做set_false_path 的约束(如下述例子)而把那些伪路径从时序报告中剔除,这里不再详述。

虚拟时钟

在 FPGA 做系统同步输入接口的情况下,很多时候上游器件送入的数据并不是跟某个 FPGA 中已经存在的真实的时钟相关,而是来自于一个不同的时钟,这时就要用到虚拟时钟(Virtual Clock)。

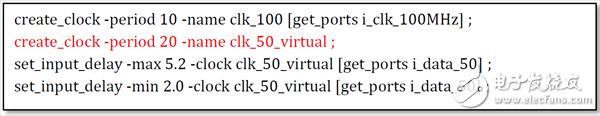

举例来说,上游器件用一个 100MHz 的时钟送出数据到 FPGA,实际上这个数据每两个时钟周期才变化一次,所以可以用 50MHz 的时钟来采样。FPGA 有个 100MHz 的输入时钟,经过 MMCM 产生一个 50MHz 的衍生时钟,并用其来采样上游器件送来的同步数据。

当然,系统级的设计上,必须有一定的机制来保证上游器件中的发送时钟和 FPGA 中的接收时钟的时钟沿对齐。

此时,我们可以借助虚拟时钟的帮助来完成相应的 Input 接口约束。

篇幅所限,对 XDC 中 I/O 约束的设计思路、分析方法以及如何具体设置 Input 接口约束的讨论就到这里,下一篇我们接着分析如何设置 Output 接口约束,看看 Vivado 中有什么方式可以帮助用户准确便捷地定义接口时序约束。

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4491

-

FPGA I/O口时序约束讲解2023-08-14 3236

-

物理约束实践:I/O约束2023-11-18 2804

-

FPGA设计约束技巧之XDC约束之I/O篇(下)2017-11-17 8289

-

XDC的时钟约束及优势2017-11-18 4224

-

FPGA约束的详细介绍2018-06-25 7306

-

XDC约束及物理约束的介绍2019-01-07 7398

-

如何将Altera的SDC约束转换为Xilinx XDC约束2018-11-27 6071

-

XDC时钟约束的三种基本语法2020-01-30 11180

-

FPGA案例之衍生时钟约束2020-11-17 3452

-

FPGA知识之xdc约束优先级2020-11-16 2749

-

XDC约束技巧之时钟篇2023-03-28 4833

-

XDC约束技巧之CDC篇2023-04-03 3699

-

XDC约束技巧之I/O篇(上)2023-04-06 2797

-

XDC约束技巧之I/O篇(下)2023-04-10 2611

全部0条评论

快来发表一下你的评论吧 !