基于动态重构技术的FPGA电路容错性能评估系统

FPGA/ASIC技术

描述

1.背景介绍

空间辐射环境中的高能带电粒子入射到半导体器件的特定区域有可能会引起单粒子效应,从宏观角度看,FPGA的配置存储器中该单元存储的信息由“1”变成了“0”,即出现了存储状态的翻转。美国Los Alamos国家实验室、Brigham Young大学和Xilinx公司对FPGA的单粒子效应进行了多次实验,得出了:单粒子效应引起的FPGA故障多数是由配置存储器发生单粒子翻转引起的。

针对FPGA内部的单粒子效应故障,研究者们提出了相应的检测与加固设计方法,如三模冗余(TMR)设计、两模块冗余(DMR)设计、时间三模冗余(TTMR)设计、状态机状态编码加固设计、运算单元的结果校验等多种方法。这些方法从逻辑设计方面提高了FPGA抗单粒子效应的能力。

本文作者在项目实践中对于系统可靠性设计方面采用过三模冗余、纠错编码等加固措施。这些加固方法带来了系统资源占用率的上升和运算速度的降低,但是其对于抗单粒子翻转性能的提升程度却难以通过简单方法获得,因此需要一种验证方法对其加固效果做出客观评估,需要一个测试系统来完成具有充足覆盖率的自动化大规模测试。本文所描述的基于动态重构技术的FPGA电路容错性能评估系统即在此需求下设计完成的。

2.动态重配置技术简介

FPGA的“动态可重配置” ,是指在系统运行期间,随时可以通过对FPGA的重新配置来改变其逻辑功能,而且并不影响系统的正常运行, FPGA逻辑功能的改变在时间上保持动态连续。由此可见, FPGA的动态可重配置不仅可以改变而且能够动态地改变数字逻辑系统的功能,与静态可重配置相比, FPGA的动态可重配置有着更广阔的应用前景。

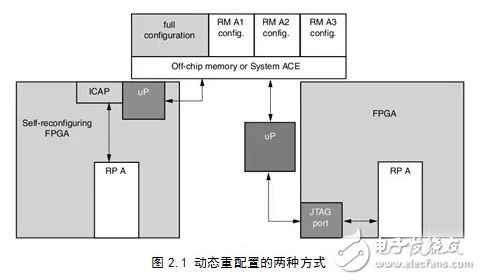

如图2.1所示,有两种途径可以实现动态重配置:(1) 依靠JTAG、SlectMAP等外部配置端口进行配置,这种方式的重配置依靠FPGA外部芯片或者上位机系统;(2) 依靠内部端口(ICAP)完成对配置寄存器,由FPGA内部产生配置指令,完成对FPGA动态区域的重新配置。

2.1内部配置访问端口

内部配置访问端口(Internal Configuration Access Port, ICAP)是FPGA内部配置寄存器的访问端口,为动态重构技术在片上可编程系统的应用提供了基本条件。在嵌入式的微处理器或其他用户逻辑控制下,从PC或者片上存储器中读取配置数据写入该ICAP接口即可完成芯片的动态重构。ICAP用于动态局部自重构,它是FPGA内部单元的入口,用户可通过ICAP访问配置寄存器。ICAP与SelectMAP工作方式相同,但不同于SelectMAP的双向数据总线,ICAP提供专门的读/写总线,总线宽度可以通过设置参数ICAP_WIDTH来确定,有三种可选的数据宽度:8位、16位和32位。

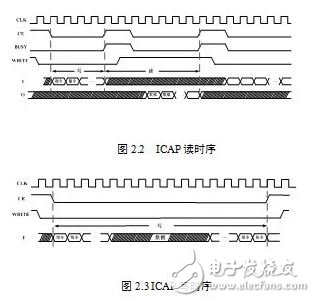

2.2配置信息写入与回读

配置信息写入的过程即是按照配置命令将数据写入配置寄存器,写入配置信息就是完成FPGA的完整配置或重配置。写入过程是通过发送包数据到帧输入寄存器(Frame Data Register Input, FDRI)来实现的,写入过程包括写命令字、写数据。

配置信息回读是通过配置端口将FPGA内部配置存储器中的数据读出的过程。回读过程可以读出CLB、IOB的寄存器、FPGA内部存储器的当前状态以及布线资源的配置情况等,而且可以通过对回读数据的校验来检验当前配置数据的正确性。本文设计的系统通过回读将待测系统的配置信息读入存储器,在此配置信息基础上注入错误后写回到配置存储器以实现故障模拟。

回读过程是通过发送命令从帧输出寄存器(Frame Data Register Output, FDRO)中读取数据包来实现的。回读过程分为写操作命令、读取数据和恢复现场三部分。每一帧的回读数据内容都决定着与其相应的物理排列的FPGA功能模块的功能逻辑.

3.基于动态重构技术的FPGA电路容错性能评估系统的实现

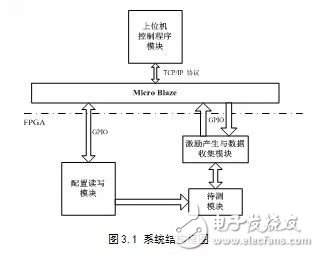

本系统结构如图3.1所示,分为上位机控制模块、Micro Blaze模块、配置信息读写模块、激励产生与测试数据收集模块。其中上位机模块提供用户交互界面,可对模拟粒子量、测试循环等参数进行配置,与测试平台之间依靠TCP/IP协议通信。在动态重构技术支持下,测试平台只需在一片FPGA内即可实现。为了与上位机实现TCP/IP通信,测试平台内嵌了Micro Blaze处理器。Micro Blaze处理器模块获取上位机指令并翻译成逻辑时序通过GPIO发送至平台的逻辑部分。逻辑部分包含了配置信息读写、待测模块激励生成和数据收集等功能。下面将分别详细介绍上位机控制程序、Micro Blaze模块和逻辑部分的实现。

3.1上位机控制程序和Micro Blaze模块

本系统的上位机控制程序基于MFC编写,TCP/IP协议栈的实现则是继承了MFC提供的异步Soket类CAsyncSocket。FPGA中嵌入了Micro Blaze处理器,利用IwIP协议栈实现和上位机的通信。通过两者的相互配合可以对待测系统的配置文件大小、模拟粒子注入量、粒子注入量放大倍数、配置信息bit翻转个数和测试循环次数等参数进行配置。并且可以将待测系统的测试数据进行收集,并发送给上位机。

参数配置完成后系统软件即可开始测试循环,每次循环包含产生随机bit翻转位、待测系统运行和收取数据三个步骤。第一次循环时不产生随机翻转位而直接开始待测系统运行,收集此次的数据作为待测系统对激励的正确响应,以后每次循环收集到的待测系统输出数据与此数据对比得到系统是否正常工作。每次循环结束后,该次循环产生的随机位置和系统工作状态信息会被记录写入文件。循环次数达到参数设定值后系统生成测试报告。

3.2逻辑部分结构

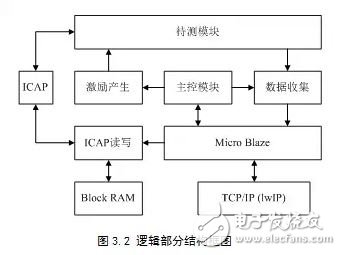

本系统的逻辑部分完成待测模块的配置、故障模拟注入、激励产生与数据收集。结构框图如图3.2所示。待测模块作为FPGA内的动态区,其首次配置由完整比特流完成,开始测试之后的重配置由ICAP读写控制模块通过ICAP端口完成。本系统的待测模块可由网表输入,也可由HDL代码或原理图输入。本文以RS编码器为例,分别将经过局部三模冗余,分布式三模冗余和全局三模冗余加固的RS编码器网表文件输入动态区,对三种加固措施的可靠性进行测试。

激励产生和数据收集模块根据待测模块变化需要做出相应调整,这两个模块协同工作完成待测模块真实工作情况的模拟。数据收集模块将待测模块产生的数据送往Micro Blaze,然后通过TCP数据包发送到上位机进行分析。本文测试中用到的为255-243 RS编码器,即输入243字节,输出243字节后带12字节的RS纠错码。测试系统对RS编码器的激励为累加数且保持每次循环都一致,输出的255字节编码结果作为输出采样数据送到上位机软件平台做自动比对。

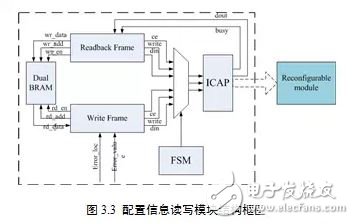

ICAP读写控制模块即为配置信息读写模块,其结构如图3.3所示,通过产生ICAP读写控制时序和指令序列,该模块在系统首次完整配置完成后通过Readback Frame模块将待测模块配置信息回读至Block RAM。此回读数据将作为以后错误注入时配置信息的基础。在以后的注错过程中,Write Frame模块将配置信息读出,根据Micro Blaze模块提供的注错位置,对配置信息加错,并写入到ICAP端口中。

主控模块对系统测试的步骤进行控制和跟踪,接收来自Micro Blaze模块的指令脉冲。Micro Blaze模块发出的指令脉冲是将TCP数据包中的指令译码得到的。Micro Blaze模块还将上位机发出的随机位置数据发送至ICAP读写模块,由后者经位置译码后产生随机bit翻转写入配置信息。Micro Blaze模块中TCP/IP协议栈的建立则是基于开源代码lwIP。

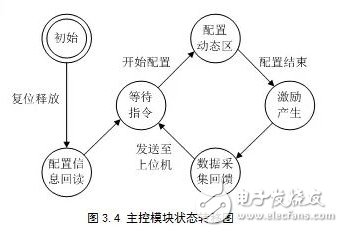

主控模块状态转移如图3.4所示。对FPGA的完整配置结束、复位释放后,首先进行配置信息的回读。此回读操作是针对动态区,也就是待测模块的。将待测模块配置信息回读后,数据将被存入片内存储器Block RAM中。以上操作完成后即进入等待指令状态,在此状态下Micro Blaze处理器将接收来自上位机的TCP连接建立请求,当TCP连接建立后,即可接收来自上位机的TCP指令/数据包。上位机将产生的随机数据打包成TCP数据包,FPGA接收到以后将动态区配置信息更改,达到设定的需要翻转bit位后上位机将发送激励产生指令,主控模块收到后将激励产生模块使能打开,动态区开始工作,数据采集模块开始对待测系统的输出采样,达到设定容量后这些采样数据将被发回到上位机。FPGA模块由此进入下一次指令等待状态。

4.系统测试及结果分析

本文将RS编码器的作为待测目标系统,对其进行可靠性评估,同时对该评估系统进行功能验证。

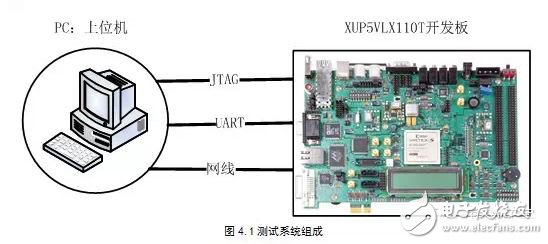

测试系统组成如图4.1所示,包括运行软件部分的上位机和实现硬件的XUP5VLX110T开发板,二者之间通过JTAG下载线、串口线和网线相连。JTAG下载线用于完整比特流的配置,串口线用于调试信息打印和Micro Blaze系统跟踪,网线用于上位机和硬件平台的通信。关于XUP5VLX110T开发板[上以太网硬件环境本文不做赘述,感兴趣读者可参见Xilinx公司的相关文档。

4.1 系统资源占用情况

系统逻辑部分采用Verilog语言描述,在Xilinx大学计划XUP5VLX110T开发板上得以实现。系统开发环境采用Xilinx公司的ISE14.3集成软件开发环境。系统实现的资源占用情况如表4.1所示。

由上表可见,该系统本身占用资源少于40%,适合规模在资源占用率60%以下的待测系统进行可靠性测试。

4.2 系统测试数据

为了分析RS编码器的可靠性,分别将RS编码器、加入局部三模保护的RS编码器、加入分布式三模保护的RS编码器和加入全局三模保护的RS编码器作为待测模块,对各自的配置信息注入随机的定量错误,收集编码结果,并与正确的RS编码器结果进行比较,给出可靠性报告。

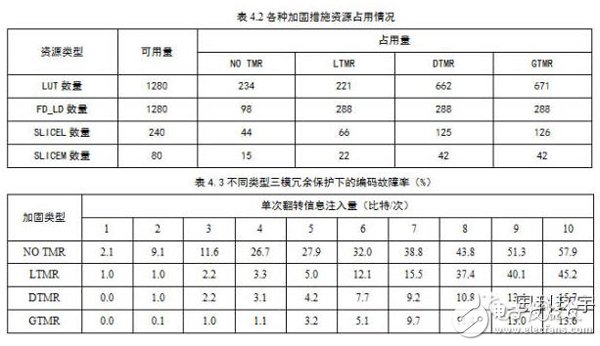

测试系统对待测模块进行三种类型的TMR加固保护,对包含无加固保护在内的四种目标系统分别执行了20000次错误注入实验。三种TMR类型分别是局部三模冗余、分布式三模冗余和全局三模冗余。

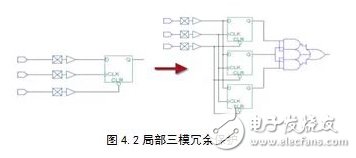

局部三模冗余(LTMR)是指将设计中的时序逻辑(包括触发器、移位寄存器、块RAM等)复制三份,并加入多数表决器来决定正确的输出。如图4.2所示。局部三模冗余中,三份触发器共享输入数据、控制信号和时钟。

分布式三模冗余(DTMR)是指将设计中的时序逻辑、组合逻辑和表决器均复制三份,表决器位于时序逻辑之后,如图4.3所示。但是,分布式三模冗余不对全局布线和I/O进行处理。

全局式三模冗余(GTMR)是指在分布式三模冗余的基础上对时钟布线以及全局寄存器进行三模处理,如图4.4所示。

由于局部三模冗余仅对时序逻辑做三模处理,一旦组合逻辑的配置信息被打翻,仅靠触发器等的复制无法保证电路功能的正确性。因此,较之于其余两种三模冗余方法,局部三模冗余的保护力度略弱一些。其余两种冗余措施组合逻辑和触发器等均做了复制,那么无论三路电路中的任意一路中的组合逻辑出错还是时序逻辑出错,均可由表决器得到正确的结果,因此,分布式三模冗余和全局三模冗余的保护力度较大,全局三模冗余略胜一筹。

添加三模冗余加固依靠Mentor Graphics 公司的Precision(2011a,update2.76)工具,它是为现有可编程器件(CPLD和FPGA)以及下一代大规模可编程片上系统(FPSoC)设计的专用综合工具。支持RTL级的逻辑综合,可实现基于约束的优化,并可给出时序分析,同时还可实现布局布线。其自动添加三模冗余的功能被业界普遍采用。实验采用Precision 套件的Hi-Re版本对RS编码器分别进行局部三模保护、分布式三模保护以及全局三模保护。占用资源情况如表4.2所示。其中可用一列显示当前设定的动态区中可用的资源情况。由资源占用情况可见,全局三模冗余的资源占用比例最大。

实验中选取对上述四种待测模块进行大量测试,针对每种待测模块,设定循环次数为2000次,每次随机注入N(N取1到10)比特翻转信息,并对单次测试结果进行统计,并给出测试报告。表4.3为由测试报告中获取的编码故障率(编码正确的次数/2000次)信息。

4.3 系统测试结果分析

通过分析表4.3可以得到以下结论:

(1) 与加入冗余保护的RS编码器相比,未加冗余保护的RS编码器可靠性较差,因此三模冗余可有效提高编码器的可靠性;

(2) 分布式三模冗余与全局三模冗余的保护效果较好,全局三模冗余的可靠性略高一些,局部三模冗余的保护效果较差,这与三模冗余采用面积换取可靠性的原理相符;

(3) 每种保护措施下,随着单次翻转信息量的增加,正确率下降。

上述实验结果与实际情况相符,充分说明了该平台功能正确,且该平台具有评估系统可靠性的能力,可应用于实际任务中。

-

FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案2021-07-05 4598

-

怎么实现基于FPGA的动态可重构系统设计?2021-05-10 3032

-

如何去实现FPGA动态部分的重构?2021-04-29 4022

-

采用模块化设计实现基于FPGA的动态可重构功能2020-07-29 2934

-

如何在FPGA动态部分重构功能设计中进行模块化设计?2019-09-20 2590

-

如何采用FPGA部分动态可重构方法设计信号解调系统?2019-09-05 1801

-

基于PAD的接收机动态可重构结构应用2019-07-10 1013

-

可重构技术分析及动态可重构系统设计2017-11-25 14680

-

基于CPLD的FPGA快速动态重构设计2017-11-22 1585

-

基于FPGA的三模冗余容错技术的研究2017-11-18 12741

-

基于动态重构技术和GSM通信的FPGA动态配置2015-02-05 2605

-

基于动态可重构FPGA的容错技术研究2012-03-09 798

-

FPGA的重构方式2011-05-27 5090

-

用于可重构硬件容错过程的辅助布线电路设计2010-04-24 1819

全部0条评论

快来发表一下你的评论吧 !