使用NI FlexRIO时我们应当了解和注意的十大点

FPGA/ASIC技术

描述

1. 1.什么是NI FlexRIO?

NI FlexRIO是NI公司的应用FPGA技术的最新产品族。它为LabVIEW FPGA提供了灵活的、可定制的I/O,以创建高性能、可重新配置的仪器。通过一个开放的、可定制的信号前端,可以满足一个测试系统或嵌入式系统的严格需求。可设计的特定模数转换装置、数字缓存装置、连接装置、甚至特定的通道数,以实现与LabVIEW可编程FPGA目标平台协同工作。

图1. NI FlexRIO系统由一个适配器模块和一个PXI FPGA模块构成,使工程师们能够在新的层次上定制LabVIEW FPGA应用。

2. 2. 一个NI FlexRIO系统含有哪些组件?

一个NI FlexRIO系统由两部分组成:一个NI FlexRIO FPGA模块和一个NI FlexRIO适配器模块。

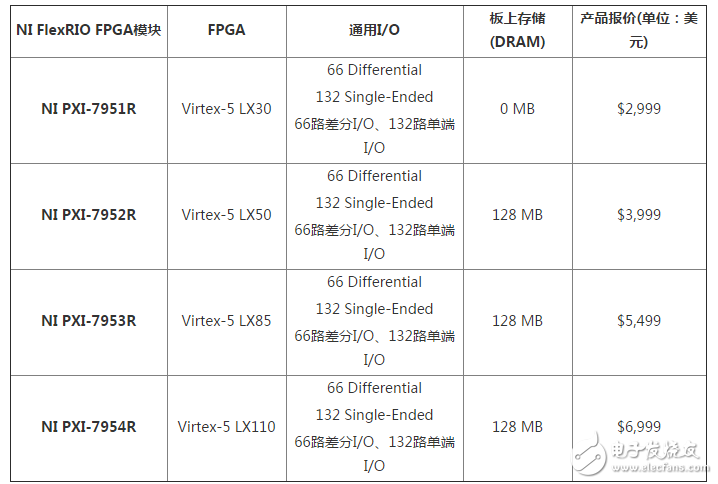

NI FlexRIO FPGA模块基于PXI平台,其特性在于它具有一个高达128 MB板上DRAM的Xilinx Virtex-5 FPGA。该FPGA应用通过LabVIEW FPGA的图形化编程实现,用于执行带有定制定时与触发功能的板上处理。该PXI平台还提供了高速数据流处理和同步功能。表1展示了当前可用的NI FlexRIO FPGA模块。

NI FlexRIO适配器模块定义了一个NI FlexRIO系统的物理输入和输出,并且是可互换和可定制的。不同的适配器模块由NI公司或者第三方制造商提供,也可以利用适配器模块开发工具和您自己的PCB设计工具定制实现。

表1.NI FlexRIO FPGA模块提供Virtex-5 FPGA和高达128 MB的板上存储以满足苛刻的应用需求

3. 3.如果没有NI FlexRIO适配器模块,我可以使用NI FlexRIO FPGA模块么?

如果您计划将NI FlexRIO系统用于信号输入/输出,那么您必须配备一块与NI FlexRIO FPGA模块的前端相连接的NI FlexRIO适配器模块。PXI FPGA模块的设计目的在于支持用户通过卡边沿连接器直接访问FPGA的针脚,以最大程度地保持高性能应用的信号完整性。由于FPGA针脚的前面没有附加的信号调理功能,这使其极易受影响,因而在实施任何接线方案前都需要一定的保护电路。鉴于此,我们必须采用一个适配器模块,以便至少在接线前保护该FPGA,但该模块还将很可能包括调理这些FGPA针脚的专用电路。现有这样一个涉及高速数字通信的范例:虽然这些FPGA针脚可以以400 Mb/s的速率进行通信,但这样的数据速率对于一台外部的待测设备并非是可以直接使用的。NI 6581适配器模块包含多个可以通过更为合适的数字连接器生成和采集多种电平信号的数字缓存器。通过这些缓存器,时钟速率降至100 MHz,在保护FPGA的同时,通信的稳定性得到了很大的提高。

4. 4. 现有哪些NI FlexRIO适配器模块可供使用?

您在挑选面向NI FlexRIO的I/O适配器模块时可有三种选择。

首先,NI公司将为具体应用开发适配器模块,以实现与LabVIEW FPGA模块和NI-RIO驱动程序的最佳软件集成。NI 6581是第一款NI适配器模块,它具有100 MHz数字I/O和可选的电压值。

其次,第三方的开发合作者也设计了面向NI-FlexRIO的适配器模块。敬请访问第三方模块网页以获取关于其可用性的更多信息。

最后,如果您无法找到一款满足您的特殊需求的适配器模块,那么总是存在设计和构建您自己的适配器模块的可能的。NI FlexRIO适配器模块开发工具集(MDK)便是用于这一原因。请记住,构建您自己的适配器模块需要有PCB设计和VHDL的经验。有几家合作者也提供定制设计服务。敬请访问第三方模块网页以获取更多信息。

5. 5.NI FlexRIO适配器模块开发工具集(MDK)包含哪些内容?

NI FlexRIO适配器MDK可供那些希望开发其自己的NI FlexRIO适配器模块的富有经验的工程师们或合作者们使用。MDK提供了关于电气与机械设计细节的全部文档(其中包括CAD文件和PCB轮廓图),以及整体金属封装。工程师们可以在开发定制电路原理图时使用这些导则,并选择几乎任意品牌的CAD软件进行PCB设计。一旦完成了PCB的制作,工程师们就可以植入组件,并添加精密的机械连接端子以尽可能方便地实现系统连接。此外,利用VHDL和一个XML文件创建一个具有套接字的组件层知识产权(CLIP)节点,还需要VHDL的有关知识。它用于在一个LabVIEW FPGA项目中准确地表示定制的I/O。

了解更多关于NI FlexRIO适配器MDK内容的信息

图2. NI FlexRIO适配器MDK提供了所有构建满足复杂应用需求的定制适配器模块所必需的信息

6. 6.我必须使用NI LabVIEW FPGA模块吗?

是的。NI FlexRIO需要 LabVIEW FPGA模块以实现与I/O的接口和FPGA应用程序的编译。与其他数据采集和模块化仪器硬件不同,NI FlexRIO没有功能丰富的驱动程序API可供使用。NI-RIO驱动程序软件使用I/O节点,以实现在硬件层次上与输入和输出的图形化接口。此外,必须创建主计算机应用以与FPGA应用相结合。

7. 7.什么是LabVIEW FPGA?

NI LabVIEW FPGA模块可以帮助您利用LabVIEW程序框图对一个FPGA进行编程。在其底层,该模块采用代码生成技术实现图形化开发环境与FPGA硬件的整合。这种利用程序框图处理FPGA的方式非常适用于FPGA所提供的对内在并行机制的一种直观描述。不论您是否曾使用过硬件描述语言(HDL),您都可以利用该模块以及商业现成可用的(COTS)硬件来创建基于FPGA的测量与控制硬件。

. systems 支持包括PCI/PXI板卡和模块化独立系统的硬件目标平台

. 超过100个面向快速开发的FPGA IP组块

. 内置的I/O直接存储器访问(DMA)提供与主机系统的快速通信

. 创建可以在40 MHz、80 MHz或者更高时钟下单个周期内执行的逻辑

. 管理LabVIEW项目中的存储器、FIFO、时钟和I/O

. 利用可供使用的向导快速启动或从零开始

8. 8.为了使用NI FlexRIO,我需要了解VHDL编程技术么?

如果该适配器模块是由NI公司开发的,那么不需要任何VHDL或其他硬件描述语言的经验。所有的FPGA编程均通过NI LabVIEW FPGA模块和NI-RIO驱动程序软件以图形化的方式完成。如果该适配器模块是由第三方开发的,则或许提供定制的LabVIEW FPGA I/O节点。若存在一个带有套接字的CLIP节点,用户的体验可能会与NI提供的解决方案相似。对于定制设计的适配器模块,设计工程师将需要利用VHDL和XML文件创建一个带有套接字的CLIP节点,以便在LabVIEW FPGA项目中正确表示定制的I/O。

图3. NI FlexRIO中的FPGA利用CLIP节点,集成了第三方的IP核并与适配器模块进行通信

9. 9.可以将第三方的IP(来自VHDL或Verilog)吸纳到我的NI FlexRIO应用中么?

是的,多年前工程师们就已经能够将HDL代码植入LabVIEW框图,以运行与其LabVIEW代码相适应的既有IP。但是,从LabVIEW 8.6 FPGA模块开始,CLIP技术支持工程师们引入第三方的IP并与LabVIEW框图并行执行。这样,第三方IP核可与NI FlexRIO结合使用。

采用FPGA技术有哪些技术优势?

下面列举了FPGA技术的五大技术优势。

. 高性能

. 上市时间短

. 低成本

. 高可靠性

. 长期维护性

10. 10.Virtex-5 FPGA具有哪些技术优势?

Virtex-5 FPGA架构经优化,可利用LabVIEW FPGA模块中的单周期定时循环更快速、更有效地运行。实现FPGA芯片内部的数字逻辑的基本构建模块被称为slice,每个slice由多个触发器和查询表(LUT)组成。上一代的Virtex-II FPGA使用4-输入的LUT,以支持高达16种数字逻辑赋值的组合。而新型的Virtex-5 FPGA使用了6-输入的LUT,以支持高达64种组合,从而提高了您在每个slice中可实现的逻辑的数量。此外,这些slice相互紧密布置,以减少电子的传输时延并提高整体执行速率。对于LabVIEW FPGA应用这意味着什么?单周期定时循环结构利用6-输入的LUT显著地提高了资源的利用率。这意味着您可以优化更多的LabVIEW FPGA代码以载入Virtex-5 FPGA,并在每个时钟周期内完成更多的操作。

-

如何利用NI FlexRIO模块去满足自动化测试需求?2021-05-06 1622

-

数据分析师应当了解的五个统计基本概念2020-11-02 2562

-

pcb拼板教程_pcb拼板十大注意事项2019-05-31 12593

-

学习PHP你应当了解哪些知识?2018-10-26 699

-

NI推出全新的FlexRIO收发器,以满足高带宽雷达系统的原型验证和测试需求2018-10-12 730

-

基于Xilinx Kintex UltraScale FPGA的FlexRIO模块介绍2018-07-05 3978

-

基于Xilinx Kintex UltraScale 技术的全新PXI FlexRIO架构介绍2018-06-30 3507

-

NI FlexRIO设备的FGPA模块和适配器模块分析2017-11-18 2286

-

在NI FlexRIO中使用DRAM2017-11-17 1588

-

基于FPGA的单原子反馈控制与LabVIEW和NI FlexRIO的介绍2017-10-15 757

-

谁成就了智能家居“十大”品牌2014-10-06 3919

-

NI FlexRIO适配器模块系列总数增至20个以上2013-07-23 1314

-

全新NI FlexRIO FPGA适配器模块基于PXI平台扩2011-01-11 774

-

NI宣布NI FlexRIO产品线增加新成员2010-03-02 1158

全部0条评论

快来发表一下你的评论吧 !