JESD204B标准及演进历程

FPGA/ASIC技术

描述

在从事高速数据撷取设计时使用 FPGA 的人大概都听过新 JEDEC 标准「JESD204B」的名号。近期许多工程师均联络德州仪器,希望进一步了解 JESD204B 接口,包括与 FPGA 如何互动、JESD204B 如何让他们的设计更容易执行等。本文介绍 JESD204B 标准演进,以及对系统设计工程师有何影响。

为何有 JESD204B 标准?

高速数据转换器设计师原本使用传统单端 CMOS 接口,约在十年前改用差分 LVDS 界面,因为后者数据传输速率较高(CMOS 接口上限约 200 Mbps),亦可改善讯号线与供电的噪声耦合。但 LVDS 接口的缺点为在采样速度较慢的情况下较为耗电,因此 CMOS 接口并未被完全取代,至今仍有人使用。 由于模拟数字转换器的演进必须提高采样速率及信道密度,业界需要比并联 LVDS 更快速、节能的数字接口,故开发出串行接口 JESD204,并于 2006 年 4 月获 JEDEC 通过。JESD204接口为单一通路、高速序列连结一个或多个数据转换器至一个数字逻辑设备,运输速率最高可达 3.125 Gbps,但必须传送共同架构频率至转换器与 FPGA,以确保架构同步。

但因为 JESD204 仅支持一条通路与一条序列连结,业界很快发现用途不如预期,故在 2008 年4 月增修标准为 JESD204A,可支持多条通路与多条链接,不过速率上限仍为 3.125 Gbps。

JESD204B于2011年7 月研发完成,可克服多项系统设计难题,除了大幅提升传输速率至12.5 Gbps,亦新增确定延迟功能,大幅简化多通道同步。

JESD204B 标准为何?

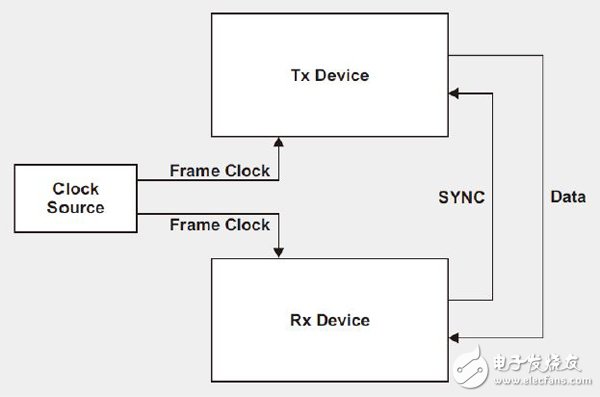

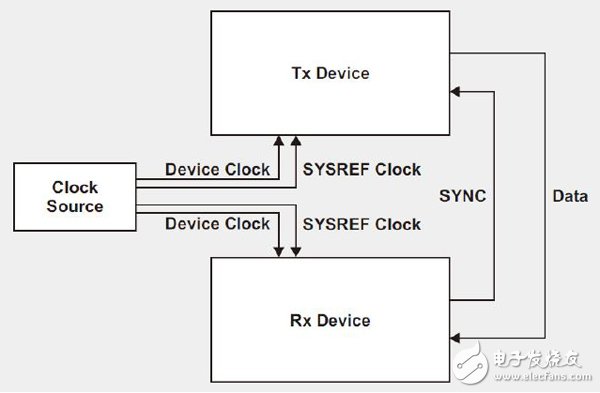

JESD204B 支持接口速率最高 12.5 Gbps,以装置频率取代架构频率,并有三种子集合。子集合0 可向后兼容 JESD204A,但速度受限、不支持确定延迟功能,且 SYNC 讯号亦有错误回报的特殊频率条件(如图一)。子集合 1 藉由同步化讯号 SYSREF,启动与结合各装置的多架构频率(如图二),可达成数据传输同步,并确保数字链接内的已知确定延迟。

图1 JESD204B子集合0介面

图2 JESD204B子集合1介面

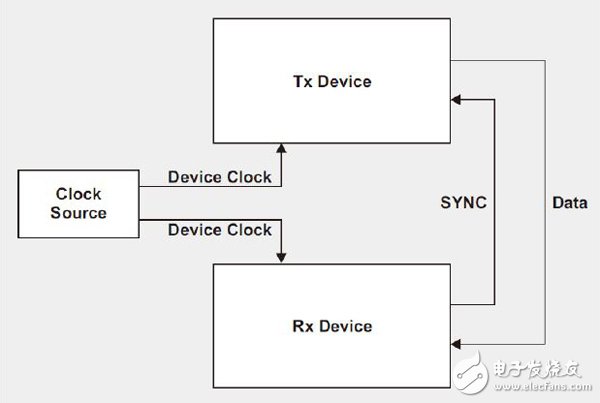

子集合 2 亦使用 SYNC 讯号(如图三),但受限于 SYNC 讯号的频率条件,通常用于数据速率低于 500 MSPS 的情况。数据速率超过 500 MSPS时,通常会采用子集合 1 并外加 SYSREF 频率。

图3 JESD204B子集合2介面

符合 JESD204B 的接收器内具备弹性缓冲空间,可弥补序列器/解序列器通道的时滞,因此简化了电路板配置。弹性缓冲空间可储存数据,直至速度最慢的信道数据抵达,之后再同时释出来自各信道的数据,进行数字处理。因为数据频率已嵌入在序列数据串流中,因此可发挥时滞管理功能。

为何重视 JESD204B 界面?

符合 JESD204B 的数据转换器将数据串行化与传输的速率皆优于旧有接口,因此数据转换器、处理器或 FPGA 所需针脚数都大幅减少,故可降低封装尺寸与成本。而最大优点在于减少针脚数后,电路板上的信道减少,让电路板配置较简单,布线也较容易。

此外由于数据频率嵌入数据串流,且接收器内亦有弹性缓冲空间,使时滞管理需求减少,因此更进一步简化配置与布线,不再须要确认曲线是否等长。JESD204B 亦可延长传输距离,因为放宽时滞条件后,逻辑设备与数据转换器之间的距离可拉长,避免任何敏感模拟零组件冲击。另一方面,JESD204B 接口能够适用各种数据转换器分辨率,故未来不论是模拟数字转换器或数字模拟转换器,都不需重新设计收发器/接收器(Tx/Rx)电路板(逻辑设备)。

LVDS 接口是否已近末日?

对低传输速率的数据转换器而言,CMOS 接口耗能较低,而 JESD204B 接口又比传统 LVDS界面多出几项优点,这么说来,LVDS 界面还有生存机会吗?

简单的说,LVDS 接口的确还是有用处的。虽然 JESD204B 标准运用确定延迟后,可简化多通道同步化,但有些应用要求延迟愈小愈好(甚至最好毫无延迟),这些应用(例如雷达等太空应用)需要立即反应或侦测,故可能延迟必须降至最低,这种情况即需考虑采用 LVDS,因为可避免 JESD204B 导致数据转换器在数据序列过程中延迟。

-

JESD204B使用说明2024-12-18 3123

-

JESD204B的优势2022-11-23 772

-

JESD204B协议介绍2022-11-21 947

-

JESD204B:适合您吗?2022-11-07 721

-

如何构建您的JESD204B 链路2022-11-04 975

-

一文读懂JESD204B标准系统2021-05-24 3175

-

如何去实现JESD204B时钟?2021-05-18 3134

-

JESD204B是什么工作原理?控制字符是什么?2021-04-06 1729

-

jesd204b ip核支持的线速率2020-08-12 6682

-

JESD204B串行接口时钟的优势2019-06-19 3738

-

JESD204B的系统级优势2018-09-18 2408

-

JESD204B SystemC module 设计简介(一)2017-11-17 3626

全部0条评论

快来发表一下你的评论吧 !