在Vivado下利用Tcl脚本对综合后的网表进行编辑过程

FPGA/ASIC技术

描述

在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在Vivado下利用Tcl脚本对综合后的网表进行编辑。

Vivado支持传统的Tcl命令,在此基础上添加了很多自身独有的命令,这些命令可看做是对Tcl命令的进一步扩展。

因此,在Vivado下,图形界面(GUI)方式进行的操作都有相应的Tcl命令,通常会在Tcl Console中显示出来。而相反,很多Tcl脚本能做的事情,GUI方式却无法处理,这也说明了Tcl的强大之处,对综合后的网表编辑就是如此。

什么情况下需要对综合后的网表进行编辑?通常是需要对网表进行微小的改动,比如对高扇出net做寄存器复制或插入BUFG,对logic level较大的路径插入流水寄存器以改善路径延迟,更改待测net等。需要注意的是,利用Tcl直接编辑网表的意义在于可以无需重新综合以节省综合的时间而直接观察编辑后的效果来判定是否需要如此修改。例如,对组合逻辑延迟较大的路径插入流水寄存器,采用Tcl编辑之后,可以重新生成时序报告,观察该路径上的时序有多大的改善,是否达到预期的效果。如果认为插入流水寄存器是有必要的,那么还是要返回到HDL代码中进行代码的修改。再例如,更改待测net,如果设计中的某个信号需要引到PCB的测试口上,可以直接在网表中修改而无需回到HDL代码中修改。

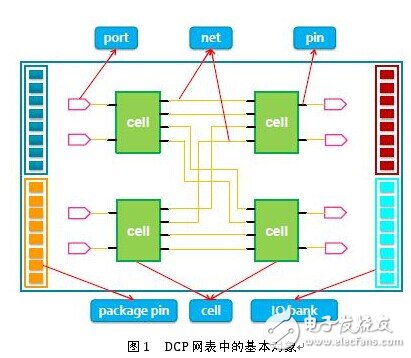

DCP网表中的基本对象

这里先介绍一下Vivado生成的DCP网表中的基本对象:cell,port,net,pin,如图1所示,除此之外还有一个重要的对象clock。在Vivado中可以分别通过get_cells,get_ports,get_nets,get_pins和get_clocks这五个Tcl命令获取到它们。这五个命令是Vivado中最基本、最常用的Tcl命令,在后续的网表编辑中会用到它们。

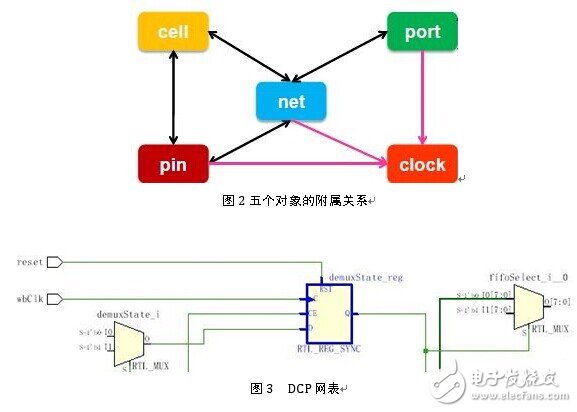

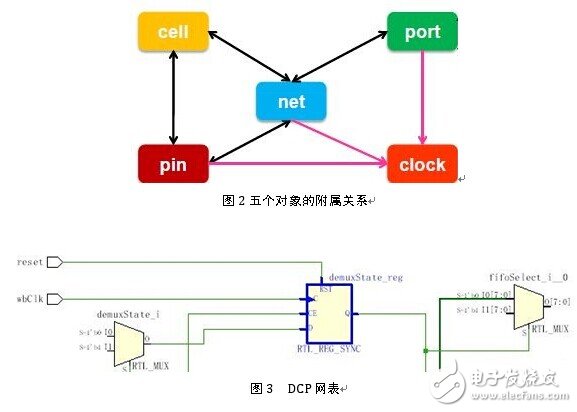

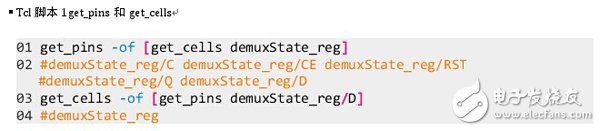

这五个对象之间的附属关系图2所示。以cell和pin为例说明图中箭头的含义,如图3所示的网表。采用Tcl脚本1第1行命令,可通过get_pins获取到该cell上的所有pin,返回值如第2行所示。采用第3行命令,可通过get_cells获取到该pin所在的cell,这是因为pin和cell是一一对应的。

编辑网表

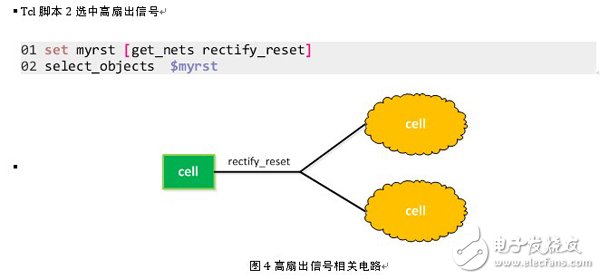

这里以对高扇出信号插入BUFG为例说明如何编辑网表。采用的工程是Vivado自带的例子工程cpu。打开综合后的网表文件,通过report_high_fanout_nets找到高扇出信号rectify_reset,并通过Tcl脚本2以原理图的方式显示相关电路,这里以图4表示。

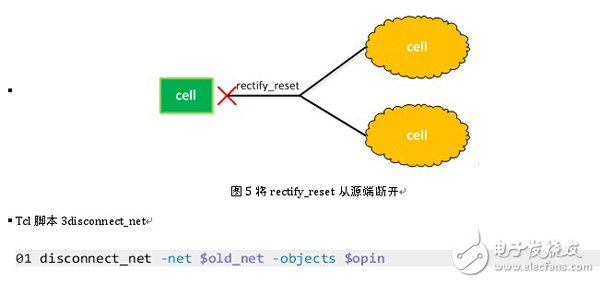

第一步:将rectify_reset从源端断开,如图5所示,相应的Tcl脚本如Tcl脚本3所示。

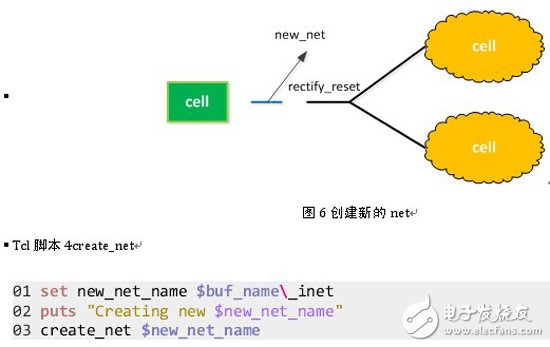

第二步:创建新的net,如图6所示,相应的Tcl脚本如Tcl脚本4所示。

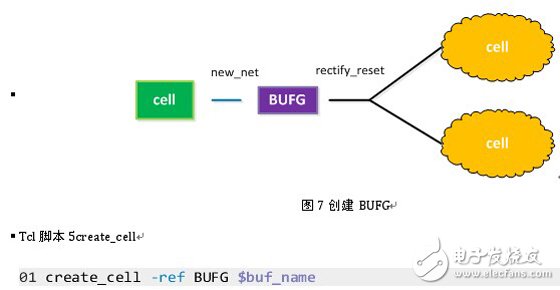

第三步:创建新的cell BUFG,如图7所示,相应的Tcl脚本如Tcl脚本5所示。

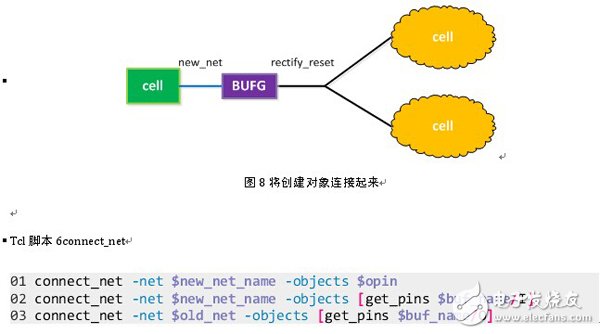

第四步:将新的net一端连接到源端输出pin,一端连接到BUFG的输入pin;将rectify_reset的一端连接到BUFG的输出pin,如图8所示,相应的Tcl脚本如Tcl脚本6所示。

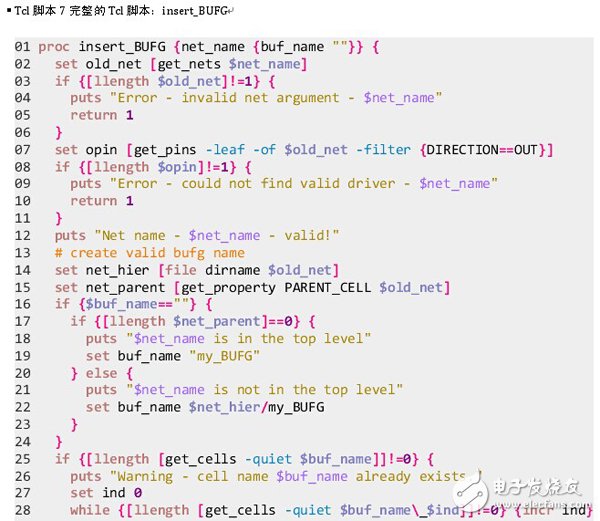

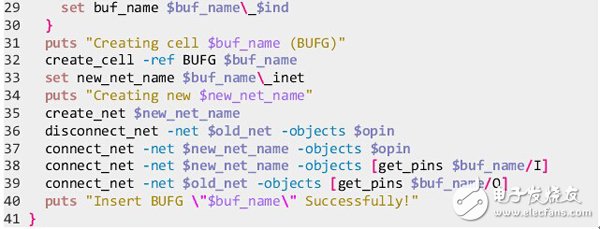

完整的Tcl脚本如Tcl脚本7所示。该命令insert_BUFG可以嵌入到Vivado中作为常规命令来使用。

-

Vivado设计套件用户指南:使用Tcl脚本2023-09-14 663

-

Vivado Design Suite用户指南:使用Tcl脚本2023-09-13 676

-

用 TCL 定制 Vivado 设计实现流程2023-06-28 6146

-

在Vivado中实现ECO功能2023-05-05 4494

-

Tcl在Vivado中的应用2023-04-15 2399

-

在Vivado中进行DCP复用方式进行说明2022-07-18 3867

-

在Vivado图形化界面IDE中运行和调试Tcl命令2022-06-17 3212

-

FPGA设计中Tcl在Vivado中的基础应用2020-11-17 3641

-

VIVADO从此开始高亚军编著2020-10-21 6033

-

【创龙TLZ7x-EasyEVM评估板试用连载】TcL脚本的使用2020-06-07 2332

-

如何为后综合模拟和/或后PAR网表模拟生成VHDL或Verilog网表?2019-11-11 2383

-

Vivado之TCL脚本语言基本语法介绍2018-04-11 11107

-

Vivado使用误区与进阶——在Vivado中实现ECO功能2017-11-18 5942

全部0条评论

快来发表一下你的评论吧 !