Virtex UltraScale器件的优点

FPGA/ASIC技术

描述

赛灵思UltraScale器件的28 Gbps 背板功能让网络能够以1 Tbps 的速率运行。

两年前,IEEE 的一篇报道指出,根据当时发展趋势,通信网络在2015 年需要支持1Tbps 的容量要求,到2020 年则需要支持10 Tbps 的传输能力。根据2012 年的这份报告,明年将有近150 亿台固网和移动网络设备,其中包括机器间的互联。对于光传输网络(OTN)应用,核心节点的每波长带宽到2015 年预计将达到100G 到400G,2020 年将提升到近400G 到1T。

赛灵思Virtex® UltraScale ™ All Programmable FPGA 是高端FPGA 系列的扩展,可支持1Tbps 系统的实现。Virtex UltraScale 系列具有前所未有的高性能、系统集成度和带宽,适用于有线通信、测试测量、航空航天与军用以及数据中心等各种不同应用。

很多公司都表示了对1Tb 网络应用的需求。这些应用要求收发器能够直接驱动25G/28G 背板,以解决可布线性、串扰、差分插入损耗和阻抗匹配等问题。而Virtex UltraScale 器件则完美解决了这些难题,无需重定时器即可支持25G/28G 背板操作,从而实现了对1Tbps 应用的支持。

使用外部重定时器会产生可靠性问题,同时还需要占用大量非常昂贵的PCB板级空间。

实例1-Tbps设计

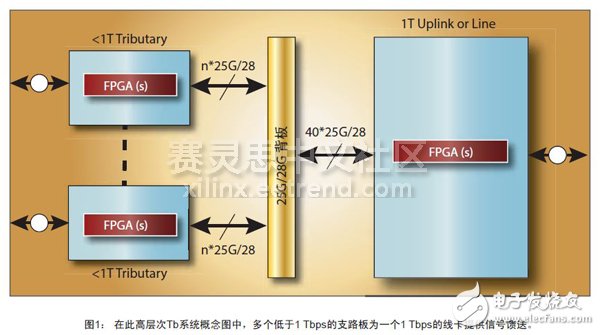

图1 是可能的通用1Tbps 系统的高层次方框图。从图中可以看到,多个带宽低于1Tb 的支路板(此图中有两个)通过在运行速率为25G/28G 的背板与一个1T 线卡相连。

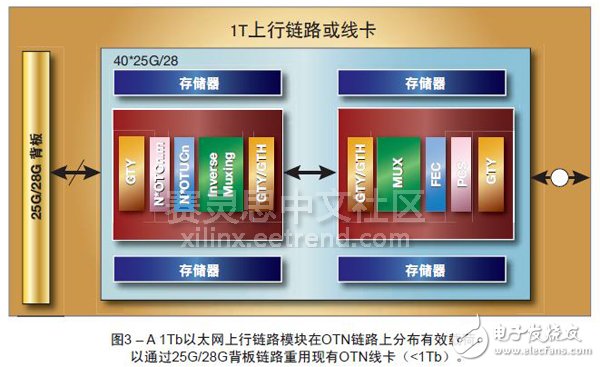

图2、3 和4 是三种可能的1Tbps以太网和OTN 应用的更详细的方框图, 它们全部以Virtex UltraScaleFPGA 为基础进行构建。33 GbpsGTY 收发器可能与CFP2/4 LR4 光学模块以及 25G/28G 背板连接。根据图示,16 Gbps GTH 收发器与高速存储器相连。

这些1T应用必须依赖于支持25G/28G的背板收发器才能实现。带10G链路的背板会面临可布线性、串扰、差分插入损耗和阻抗匹配等问题。

这些1T应用必须依赖于能直接在背板上以25G/28G直接运行的FPGA才能实现。使用外部重定时器会产生可靠性问题,同时还会占用大量非常昂贵的PCB板级空间。背板重定时器为附加组件,必须部署在线卡和支路板上。背板重定时器运行所需的电压调节模块、配电网络、直流阻断帽和参考时钟都会占用这些PCB的板级空间。

可布线行问题

在这些实例中,我们展示了以25G/28G在背板上运行的40个信道,总带宽为40 x 25 Gbps = 1 Tbps。背板厚度通常约为0.25英寸,这主要取决于两个因素:连连接器压装(press-fitting)的机械要求,以及对于多个信道路由支持的需要。如背板接口仅支持10 Gbps操作,则信道数需要增加为原来的2.5倍。对于每个1Tbps线卡和支路板,这样会将背板信道数量从40增加到100。如系统需要25个支路板和线卡,最终所需的信道总数则为100 x 25 = 2,500。这会对路由造成很大的挑战。

使用背板介电材料如松下的介电常数约为3.65且标准导线宽度为7 mil的Megtron-6,我们发现每个差分带状线对的堆叠高度为:每100Ω的差分奇模阻抗对应16密耳。

假定背板连接器间距通常为2mm,则每层的连接器引脚之间可以部署1 个信道。因此,背板每层能够支持每层每个连接器10 个信道(发送+ 接收)。对于25 Gbps,通常需要16个布线层, 总板厚度为16 密耳 x 16 布线层 = 0.256 英寸。对于10 Gbps,厚度为0.640 英寸(16 x 2.5 = 40 个布线层,总板厚度为16 密耳 x 40 层= 0.640 英寸)。但是,背板最大厚度通常由通路孔的深度位宽比决定。典型的通路孔直径为 15 密耳,标准深度位宽比为25:1。这意味着背板厚度上限约为14 x25 = 350 密耳。因此,10G 背板无法支持1T 应用。

串扰问题

对于1T 应用而言,25G 背板相对于10G 背板的另一个关键优势是串扰。串扰通常由于信道距离导致的。背板信道越多,发生串扰的几率就越高。因此,带有1000 个25G 信道的背板比带有2500 个10G 信道的背板发生串扰的几率更低。

但是,大多数介电材料都并非完全同质,因此都会具有远端串扰(FEXT)效应。此外,在背板连接器周围的通路孔区域发生的串扰通常都是远端串扰。

由于背板系统的串扰既有近端串扰(NEXT)又有远端串扰(FEXT)效应,设计师必须谨慎降低与总噪声预算相关的串扰噪声成分。敏感器件和干扰源网络之间即存在互电容Cm(电场),又存在互感Lm(磁场)。互感会在与干扰源网络相对的敏感器件线路上感应产生电流(楞次定律)。互电容会通过互电容传递在敏感器件线路上的双向电流。近端和远端敏感器件线路上的电流一起产生NEXT 和FEXT 效应。

I(Next) = I(Cm) + I(Lm) while I(Fext)= I(Cm) – I(Lm).

NEXT 永为正数。FEXT 即可为正,也可为负。

差分插入损耗

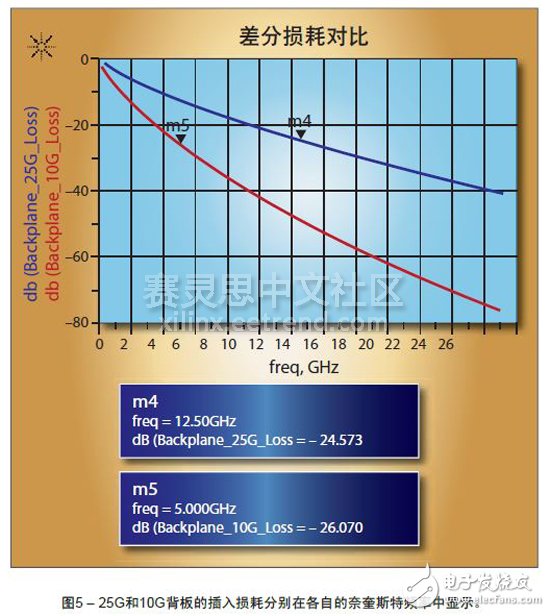

信道的插入损耗是建立可靠链路时的重要参数。IL 取决于两个因素:连接器损耗和介电损耗。使用如松下Megatron-6 等介电材料时,切线损耗为0.004。图5 显示了1 米长走线的插入损耗。表面粗糙度为1 微米(超低截面)。由于背板的最大厚度为0.350 英寸,10G 背板的走线宽度已经降至只有3 密耳宽,以允许在0.350 英寸厚的背板上铺设40 层布线,同时将差分奇模阻抗维持在100Ω。对于25G 背板,走线宽度为7 密耳,可以在最大厚度为0.350 英寸的背板上铺设16 层布线。

图5 显示,10G 背板的差分插入损耗高于25G 背板。这是因为10G 背板在最大背板宽度内增加了布线层数,从而导致走线宽度更窄。

我们已经指出,Virtex UltraScale 器件能支持无需重定时器的25G/28G 背板操作,从而支持1Tbps的应用。这些未来的1Tbps 应用要求接收器能够直接驱动25G/28G 背板,以解决可布线性、串扰、差分插入损耗和阻抗匹配问题。过多的布线层数、更大的连接器以及与通路孔深度位宽比相关的制造可靠性问题都会有一定影响。

- 相关推荐

- 热点推荐

- FPGA

- UltraScale

-

Virtex UltraScale+ FPGA数据手册:DC和AC开关特性2023-09-13 578

-

Xilinx Virtex Ultrascale FPGA MGT电源解决方案2022-09-21 1802

-

xilinx推出全球最大容量FPGA— Virtex UltraScale+器件2019-08-24 4411

-

Virtex UltraScale FPGA VCU108 评估套件是最理想的开发平台2019-08-01 4917

-

赛灵思公司宣布其Virtex UltraScale+ FPGA面向首批客户开始发货2019-07-30 3362

-

Virtex UltraScale FPGA产品简介资料说明2019-02-19 1430

-

Xilinx 16nm Virtex UltraScale+ FPGA器件的功能2018-11-27 4820

-

Virtex UltraScale+ FPGA VCU110开发套件的特点性能演示2018-11-23 4453

-

符合Virtex UltraScale方案的Virtex UltraScale 30G GTY收发器2018-11-22 4154

-

12V输入的Xilinx Virtex Ultrascale FPGA电源参考设计2018-08-29 1989

-

Xilinx Virtex UltraScale FPGA VCU108 评估套件2017-02-08 774

-

全新 Virtex UltraScale+ FPGA 评估套件加速高带宽应用2017-01-13 3547

-

Xilinx UltraScale 系列发布常见问题汇总2013-12-17 4103

全部0条评论

快来发表一下你的评论吧 !