存储器领域的现状

FPGA/ASIC技术

描述

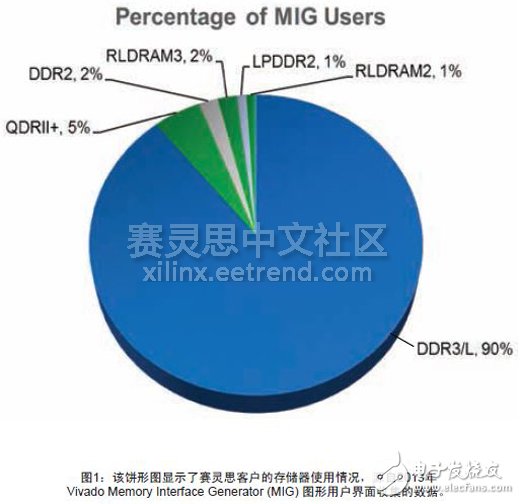

赛灵思有90%的客户在使用DDR存储器。DDR4是倍受青睐的DDR存储器系列的最后一代。众多竞争者们正在虎视眈眈,意图抢占更大的DDR4市场份额。

存储器领域正在发生翻天覆地的变化,这一变化的根本原因在于倍受青睐的DDR存储器系列将在DDR4戛然而止,而赛灵思有90%的客户都在使用该主流缓冲存储器(图1)。

无需过度恐慌:原因在于DDR3能够与大多数系统板完美兼容,DDR4尽管进展缓慢,但在未来数年将会逐步取代DDR3的位置。尽管如此,由于DDR4没有继任者,客户正在寻找另一种存储器,同时也在认真权衡带宽、容量或功耗。可能的继任者是LPDDR3/4,而某些应用领域则更倾向于混合存储立方体(HMC)等串行DRAM解决方案。

为了了解存储器面临的这些重要挑战,让我们先来看看影响这些器件的市场趋势,以及“迫使DDR帝国没落”的限制因素。接下来,我们会考虑替代DDR的新存储器类别,从LPDDR到串行存储器——相信设计人员都希望了解这一新概念。

瞬息万变的市场趋势

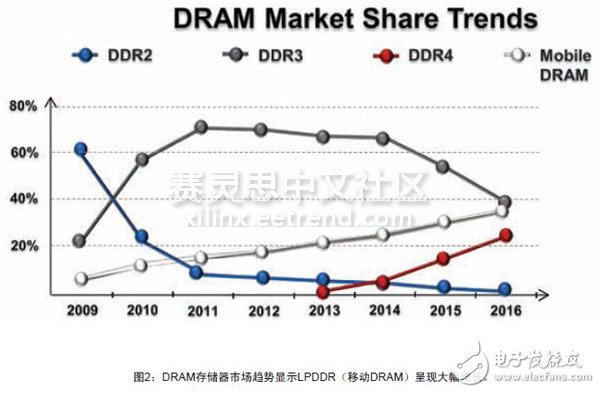

通常,当客户在设计他们的新一代产品时,他们总是会选择同样存储器的新一代产品,以获得更高的容量、速度和吞吐量。鉴于此,图2显示了当前和预计的DRAM市场份额变化趋势。DDR3占据了当前总DRAM市场约70%的份额,这一市场主导地位的确立是由于2009到2010年间其市场份额急剧上升了40%。DDR4的市场接受速度稍慢,部分是因为移动DRAM(又被称为LPDDR)的“侵入”。如果LPDDR能够满足无线市场的需求,那么DDR4的增长空间将会非常有限。

图中,DDR4增长的确呈加速之势,因为它有很多优势,如供电电压较低,所以更加省电,且速度较快。因此,它最终会在各个市场上取代DDR3,且最终取决于PC市场空间。尽管PC的DRAM使用已经不再超过70%的市场份额,但PC仍然是最大的商品设备细分市场。存储器厂商声称,目前DDR4主要用于服务器,而非个人电子产品细分市场。尽管如此,DDR4仍是众多设计的绝佳选择。这种存储器类型广为人知,并且在很长时间内都会存在,尤其是因为它没有继任者。

为什么DDR4是最后一代?

那么,为什么没有DDR5?当终端客户需要采用新器件时,他们希望有更多的存储器可供选择。客户对存储器带宽的需求永无止境。MP3播放器需要存储10,000首歌曲,而曾经流行的盒式录音带则只能存储几十首。客户希望智能手机也能够存储成倍的图片或视频数量。这些期望通常意味着更多组件和更大的板极空间。讽刺的是,消费者通常并不希望他们的电子设备尺寸与存储容量或性能保持同比增长。他们希望技术进步,这样在同样甚至更小的空间内就可以存储更多内容。

当存储器与赛灵思FPGA配合使用时,有具体的操作指南,用于指导板面布局,以确保边距合理以及系统整体成功。具体实例包括走线长度、终端电阻和布线层。这些规则限制了设计的最小尺寸,或者不同部件的最近距离。

最小尺寸板面设计的替代方案可能是一些最前沿的封装类型。不幸的是,如果采取新的封装技术,例如通过硅通孔技术(TSV)实现芯片堆叠,则会使成本急剧上升。DDR存储器并非高成本器件,完全依赖于行业基础设施的规模经济,因此无法采取激进的封装方式或承担价格的提升。因此,这些技术进步在可预见的未来不会对DDR3或DDR4系统有任何帮助。

消费者还想要更快的速度。以更快的速度运行系统会导致电路板设计更加复杂。DDR存储器采用单端信号,信号需要合理端接。您运行系统的速度越快,保证系统功能正常运行的从存储器到FPGA的走线越短。这意味着器件本身需要放置在更加靠近FPGA的位置。与FPGA的距离限制意味着您在设计中能够使用的存储器件数量将会减少。很多DDR4设计会在FPGA周围封装尽可能多的器件,已经达到了设计极限。

如果您想要更多存储空间,您就需要更多器件。如果您需要更快的速度,您就需要缩短器件之间的距离。在有限的空间内能够挤进的存储器件数量有限。DDR5在速度方面的任何改进都会降低存储器件可用的区域,从而降低可用的存储空间。

DDR3的继任者应该是谁?

DDR4能否完全取代DDR3?可能不会全面取代。趋势表明,服务器市场正在采用DDR4,而DDR3较低价格优势仍在持续,使它成为个人电脑细分市场的首选。毫无疑问,消费者对于速度和存储空间的需求会继续增长,最终PC会全面采用DDR4存储器。

如果不是LPDDR,那会是什么呢?

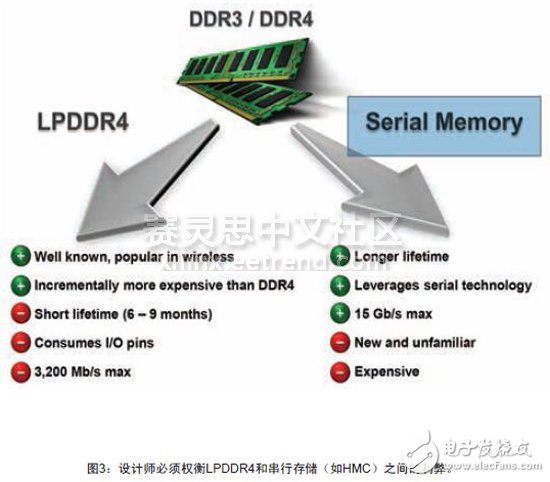

除了LPDDR之外,还有其它几类存储器在觊觎成为下一代存储器继任者。串行存储器就是一种可行的替代方案,并且它完全改变了人们对存储空间的看法(图3)。

从FPGA的角度来看,存储器是最终障碍,也是最后需要串行的部分,原因就是延时。数据从并行流变为串行,通过串行链路,然后再从串行转换为并行数据流,这个流程耗时太长。现在,使用串行链路的缺点在某些应用中是可以容忍的(例如多次写入且只有少量读取的情况下,如CT扫描器的测试测量系统或扫描天空的一组望远镜)。在另一方面,如果质量测量需要写入数据并且立即阅读该数据,串行存储器在任何情形下的表现都劣于并行数据。但是,如果好的存储器的衡量标准是高带宽、能存储大量视频或在互联网上发送大量信息,那么串行存储器就很有诱惑力。

抛开延时,我们需要对同样的弊端进行研究。生命周期不是问题:与LPDDR较短的生命周期相比,这些产品只要有市场需求就可以生产。事实上,如果对串行存储器的需求增加,众多厂商都可能会加入生产该存储器件的行列。

串行存储器没有采用I/O引脚,而采用串并收发器技术。在FPGA中,我们可以使用串行接口(收发器)实现高速率运行。最近,由于降低延时的需求,厂商们也已经解决了这些性能方面的问题。这种高度发达的串行技术能够实现极高的吞吐量,每秒可达15 Gb。下一代(以HMC为例)吞吐量预计可达到30 Gbps。人们喜欢“新事物”,但同时又害怕接触不熟悉的事物。另一方面,新技术会导致生产速率受限且初始价格更高。

混合存储立方体(HMC)

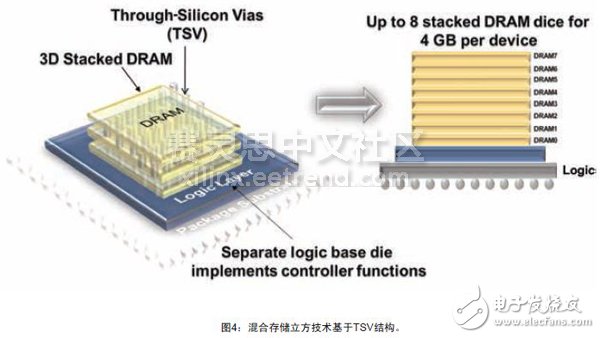

最有望取代DDR DRAM的串行存储器为混合存储立方体 (HMC),由混合存储立方体联盟 (HMC Consortium) 推广,首倡者为美国美光(图4)。该技术的赞助者在推广HMC方面做的非常出色。人们甚至开始使用缩写词HMC来代表“串行存储器”。但事实上,HMC只是串行存储器的一种。

除了HMC之外,MoSys公司正在开发一种名为Bandwidth Engine的串行SRAM存储器,博通公司也提供了一系列串行接口TCAM方案。与之相对,三星和海力士半导体正在推广高带宽存储器(HBM),这是一种基于TSV的堆栈式DRAM,采用超宽并行接口。该存储器看起来似乎风险更低,因为它采用的是并行接口。

但是,目前HMC是从DDR3和DDR4夺取市场份额最有力的竞争者。HMC采用TSV技术,在逻辑层的顶部堆栈了4到8层互相连接的DRAM,以创建2G或4G的封装。该逻辑层可提供一个便捷的接口。

如果需要更多存储空间,您可以将多达8个器件以菊花链形式连接起来。这种1对4的链路能力(以半个链路为单位步进)能够实现256位的存取和超大吞吐量。每个链路包括16个收发器(半个链路为8个),每个都能够处理15 Gbps的数据。这种超大带宽是之前的存储器设计师所不曾体验过的。

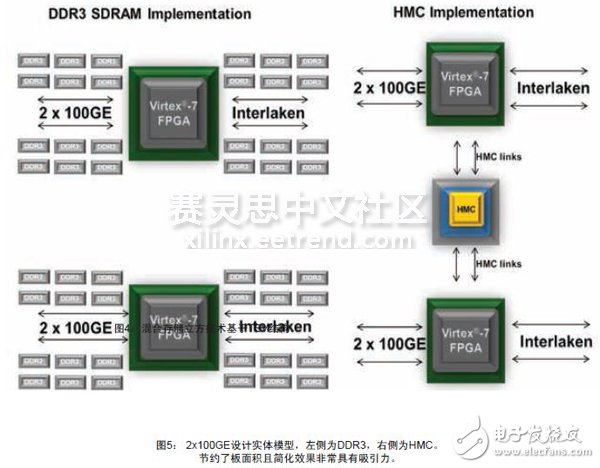

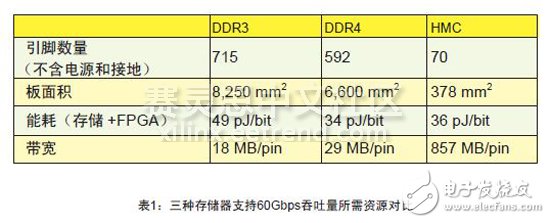

如需了解对DDR解决方案的带宽技术改进,敬请参见表格1,该表格给出了三种设计,每一种 (DDR3/DDR4/HMC) 都被调整为支持60 Gbps的吞吐量。请注意,HMC解决方案中的引脚数量较原来至少减少8倍,极大地降低了电路板的复杂程度并简化了布线(如图5所示)。串并收发器链路的高带宽允许采用更少的器件,本例中仅有一个器件。该单一器件和一个FPGA所占据的板极空间降为原来的1/20。最后,HMC解决方案每比特数据的能耗也降低了2/3。这些数据非常具有震撼性,让观察者们相信HMC能够从DDR4中赢得一部分市场份额。

其它串行存储器

由于HMC和“串行存储器”经常被错误混用,有时候甚至用来代表任何一种新的高带宽存储器,因此探索一些其它新出现的存储器件是非常有益处的。该类别的三大有力的竞争者为MoSys的Bandwidth Engine、博通公司的TCAM,以及三星、海力士半导体和Intel推广的HBM。

MoSys的Bandwidth Engine(BE2)类似于串行SRAM,而非串行DRAM。它采用收发器实现16 Gbps的吞吐量。但是,BE2不太可能取代DDR。相反,它支持72位存取和更低延时,目标是针对QDR或RLDRAM。它可用于存储数据包头或查询表,而不是像DDR一样存储数据包缓冲区。

TCAM为三态内容寻址存储器。这种特殊的高速存储器可以广泛地搜索在高性能路由器和交换机中找到的模式匹配。与高性能相伴的是高费用、能耗和发热。除了速度快之外,TCAM在本质上是并行的,它没有使用串并收发器实现高速度。但是,博通公司正在推出该类存储器的各种串行版本。

因此,TCAM解决方案仍具备串行存储器所具备的引脚数少和速度高的优势。

第三种类型的存储器为HBM。不要被HMC和HBM之间偶尔发生的争辩所迷惑。鲜为人知的是,HBM器件是买不到的。事实上,如果您想使用HBM,就必须从海力士半导体购买一个芯片,并且将该芯片安装在您的封装内部的插入器或硅基片上。插入器设计中必须包含从您的器件到存储器的连接,才能实现这一高带宽的并行存储器。

这种类型的存储器想要占领市场,企业就必须决定他们想要分享的商业机密相关内容,还必须同意采用该类存储器的设计标准(插入器设计、高度、接口、公差等等)。这些细节可以解决,但目前尚未解决。另一方面,HBM的延时会很低。这是因为电子器件的迁移距离会非常小,因为它位于封装内部。这个创意非常好,但需要未来的进一步检验。

进入生产阶段

上述任何或全部解决方案的成功都能确保更多的供应商加入到为该行业服务的先行者队伍当中。目前正在生产当中的解决方案是MoSys的BE2。HMC正在试样,到年底将会全面投产。LPDDR4今年年中会开始试样。HBM并不会作为独立封装提供,但有传言说HBM可能串行并独立封装。如果您想要购买芯片并将HBM整合到您的封装里,您可以联系三星或海力士半导体或其他更小的厂商,很多客户正在这么做。

目前,DDR3仍在销售,表现强劲,而DDR4正处于增长和市场接受阶段。DDR4也会有持久的生命力,很可能比现在倍受青睐的DDR3持续时间更长,因为它是高度成功的存储器件的最后一代产品。LPDDR4最有可能填补该空缺,但不会在所有领域取代DDR4,除非有非常快速的读/写迭代。

否则,串行存储器将成为最值得关注的新兴技术。HMC正准备取代DDR,而Bandwidth Engine则是可以取代QDR和RLDRAM的串行解决方案。

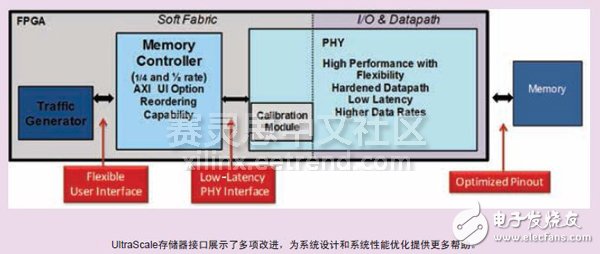

赛灵思如何量身定制ULTRASCALE存储器的性能

赛灵思UltraScale ™ FPGA 专为存储器所需的更高性能和更大的灵活性而设计。演示证明DDR4 运行速度可达2,400 Mbps。这一全球最快的速度得到Agilent 的证实,该公司在设计出了可插入在存储器下方的插入器,并在系统运行时进行系统眼图测量时获得了这一速度。由于DDR4 采用了新型“伪开漏”(POD) I/O 结构,赛灵思也在UltraScale 中添加了POD。该结构与I/O 电压需求为1.2V 的DDR4 协议相结合,能够使存储器接口I/O 系统比类似速度的DDR3 系统节约35%。

除了DDR3 和DDR4 之外,UltraScale 还支持大量其它的并行存储器: LPDDR3、RLDRAM3、QDRII+ 和QDRIV。在串行存储器领域中,UltraScale 可支持HMC 和MoSys 的Bandwidth Engine,该器件带有多达120 个收发器,足以应对大多数应用。

此外,UltraScale 还进行了内部改进,以提升存储器接口性能和FPGA I/O Bank 的利用率。为了提升利用率,赛灵思增加了每个Bank 的I/O 数量,每个I/O Bank 有两个PLL。此外,还增加了更精确的5 皮秒抽头时延功能。不仅如此,每个I/O Bank 还支持4 字节通道,每个通道有13 个引脚。赛灵思还为I/O 的预加重和均衡增加了电路。

这一代技术目前支持4 排DIMM 模块和4 个器件,内存访问深度增加了4 倍。物理层时延的改进让数据访问更加快速。大量的改进意味着存储器架构将得到优化,以满足您所在市场的性能要求。

UltraScale FPGA 支持所有主要的存储器标准。带有MIG IP 向导的Vivado® 设计套件让部署更加快速,因此客户能够更加关注解决方案而非问题。

— Tamara I. Schmitz

-

存储器的分类及原理2008-08-17 1167

-

存储器.ppt2009-04-11 950

-

嵌入式存储器发展现状2009-12-21 855

-

相变存储器:能实现全新存储器使用模型的新型存储器2009-12-31 1532

-

MCP存储器,MCP存储器结构原理2010-03-24 2567

-

存储器卡,存储器卡是什么意思2010-04-01 4051

-

存储器体制的现状和未来改变2018-12-14 4253

-

存储器和新兴非易失性存储器技术的特点2020-06-09 1823

-

只读存储器和随机存储器的区别2020-07-27 18895

-

一文分析2020年存储器的行业现状2020-10-20 4845

-

PLC系统存储器与用户存储器的功能2021-08-04 1598

-

存储器理解2021-11-26 1274

-

存储器工作原理及如何选择存储器品牌2022-10-11 5288

-

ram存储器和rom存储器的区别是什么2024-08-06 3501

-

内存储器分为随机存储器和什么2024-10-14 4999

全部0条评论

快来发表一下你的评论吧 !