基于FPGA时序优化设计

FPGA/ASIC技术

描述

现有的工具和技术可帮助您有效地实现时序性能目标。

当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。目前,设计人员掌握了一些使用技巧,可以帮助您设置时钟;通过Synopsys Synplify Premier 等工具正确设置时序约束;然后调整参数,以满足赛灵思FPGA 设计的性能目标。

有多个攻克角度,其中包括:

•更好的设计设置,例如完整、准确的时序约束和时钟规格;

•节省时间的设计技术,例如仔细RTL编码,以求更佳的性能效果,以及将造成最大性能问题的设计部件整合在一起,从而缩短随后调整设计时序的迭代运行时间。

•综合关联,并布局布线时序,以产生更好的时序结果质量(QoR)和时序收敛。

现在从三个方面详细介绍一下这些技术,并检测如何使用以实现您的时序目标。

您需要确认您已经充分、完全地对您的设计进行约束,且未过度约束。

第一步:更好的设计设置

最大的成本开销来自于指定正确、完整的设计约束条件。这些约束条件可以在设计意图和设计性能目标与综合工具之间实现通信。综合设计之后,这些约束条件和关键路径信息将自动传递至Vivado®Design Suite布局布线(P&R)工具,以进一步确保满足时序要求。

综合工具可以帮助您应对设置综合前约束这项艰巨的任务。您的任务清单如下:

1.识别时钟

2.识别并创建时钟组和时钟关系

3.约束时钟

4.约束设计输入和输出

5.定义多周期路径和错误的路径

您需要确认已经充分、完全地对您的设计进行约束,且未过度约束。过度约束将导致运行时间延长,并有可能报告错误的关键路径。务必要指定多周期和错误路径,并对衍生时钟设置约束(define_path_delay, define_false_path)。

设置Vivado流程的初始约束文件

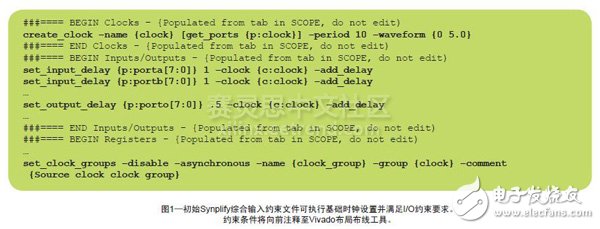

由于约束条件设置工作非常困难,因此综合软件可以提供一个初始约束模版,其中的基础约束和语法可以作为此项工作的起点。例如,在Synplify综合软件中,运行TCL实用程序为特定的设计创建一个初始FDC文件:

TCL: create_fdc_template

图1给出了该流程将生成的约束文件(.fdc)的实例。该实例中,您可以看到声明时钟、时钟组(时钟之间的关系)和输入/输出延迟等关键项目已经纳入考虑范围。

针对Vivado Design Suite流程中约束设置的最佳实践

在Vivado Design Suite流程中设置约束条件时,要确保进行以下操作:

•定义输入端口或与输入端口连接的网络上的所有基础时钟。

•定义黑盒输出引脚上的时钟。

•定义网络上生成的时钟。

•不要定义逻辑选通时钟。

•提供正确的时钟约束:不要过度约束,并确保将不相关的(又称异步)时钟放置在单独的时钟组中。

•定义时序例外,例如错误路径和多周期路径。

提示:在Vivado Design Suite中,时钟约束应尽量接近源时钟,而不是赛灵思 ISE® Design Suite流程中的BUFG。

确保您的约束条件正确无误

我们建议在设计设置阶段采用四种约束验证技术。为了让您了解应该做的约束检查类型,我们来看一下Synplify软件执行的各项检查。

首先,运行“语法检查”—即快速进行约束条件检查,其中包括其嵌入的“get_XX” 和 “all_XX”命令,用以发现和清理任何约束语法错误。错误会显示在日志文件中,并可以超链接至错误手册,以解释错误并提出修改建议。使用Tcl命令check_fdc_query。

第二,运行“综合检查”以检测与硬件相关的错误,例如错误编写的触发器。这些错误会以单独的日志文件报告。

第三,运行基础“快速综合”,以检查时钟设置问题,包括声明、衍生和推断时钟。快速综合支持执行时钟设置检查,因其可生成时钟报告和时序报告,进而使时钟设置问题明朗化。

一些综合工具可支持在“快速”模式下运行综合,其为了实现较短的运行时间,其会禁用一些综合优化。在Synplify Premier综合软件中,您可以通过以下命令实现:

set_option –fast_synthesis 1

综合编译器将创建一个综合报告时钟总结,您可以使用其中有关推断时钟的信息用以识别、定义和约束时钟。

第四,运行全面的“约束条件检查”。该检查会查找关于时钟关系、未约束开始/结束点、未锁定I/O和无约束I/O的约束设置问题。

一个全面的约束检查还会查找正确应用的约束和实例名称。例如,它会标记出应用于不存在或无效参数和对象的时序约束。然后该工具会针对不可应用的约束和未找到的实例生成详细的解释性报告,以便纠正约束文件。Synplify综合工具将在综合预先映射阶段自动运行这些检查,或者您可以在综合开始时使用以下TCL命令运行约束检查:

TCL: project -run constraint_check

运行这些基本的检查类型可在综合周期的早期就能找出潜在的错误,从而改进结果的质量(见图2)。

运行综合之后,请务必要分析后期综合时序报告,因为其可以提供重要的信息。例如在使用Synplify软件时,时序报告的起始时钟部分中的“系统时钟”显示,一些I/O没有被约束。此报告的接口信息将确认情况是否如此。

第二步:RTL代码风格和关键路径调整

为了收敛更好的时序,我们建议您针对有限状态机、RAMS、数学/DSP功能、时钟树和移位寄存器使用特定的代码风格。结果将改进时序QoR,因为通过FPGA原语构建模块,综合工具能够更好地推断实现。

另外,这些代码风格可以避免创建不必要的逻辑,例如推断锁存器、RAMS的读取/写入检查逻辑,以及已经装入DSP原语中的逻辑。关于这个话题我们已经谈了很多,使用综合工具中的核生成器性能是关键考虑因素。例如,Synplify软件包含一个SynCore IP向导,它可以为支持字节的RAM自动生成所需的RTL代码风格。其他IP生成器,例如赛灵思IP Catalog、Synopsys Synphony Model Compiler或Synopsys DesignWare coreTools和DesignWare Building Blocks,也可以帮助您配置IP,执行许多DSP和数学功能,并创建良好的RTL代码风格。如果是手动编码,请记住以下内容:

针对有限状态机

•对于赛灵思流程,启动后请使用同步复位将硬件设置为有效状态,或者在操作期间复位硬件。

•将时序模块从combinational-always模块中分离。

•为所有可能的现态指定次态。

针对模块RAM

•在一切可能的地方尽量编码同步RAM,因为它们一般会以较高的时钟频率运行。

•将RAM编码放置在单独的模块里,以便易于在网表级别进行调试。

•在决定使用RAM(带特定复位条件、支持双端口或字节的RAM,或非对称RAM)之前,请看一下推荐的代码风格,并查看是否支持推断。如果不支持,则网表结束时可能创建较多的控制逻辑。

•请勿从写入相同时钟周期的同一个地址中读取。

•如果其他方法均告失败,可以使用属性(syn_ramstyle for Synplify software)强制让使用寄存器实现,释放RAM资源供以用于更重要的时序和更大的RAM。

针对DSP模块

您可以使用这些原语执行过滤器和数学函数,例如计数器、加法器、乘法器、除法器等。

•将DSP编码放在单独的模块里,以便易于在网表级别进行调试。

•如果其他方法均告失败,可以使用属性(syn_ dspstyle for Synplify in Vivado Design Suite flows)强制使用DSP 模块实现。

针对SRL

您可以将移位寄存器装入选择select_SRL Xilinx SRL原语或在寄存器中执行。

•封装自动进行。对于移位寄存器链,Synplify软件始终会将链中最后一个寄存器留在封装select_srl之外,以便优化时序QoR。

•如果其他方法均告失败,可以使用syn_srl风格属性来控制SRL的实现方式。

针对时钟树

•由于在综合期间其不会自动推断,因此建议在RTL中实例化锁相环(PLL)、时钟生成器或时钟多路复用器。

•PLL的输入时钟的时序约束会在PLL输出针脚上自动生成衍生时钟约束

为了更好地检查时钟约束,可以在原理图查看器中进行检查。例如,Synplify HDL Analyst工具就可在时钟树上运行过滤器,使您可以观察并调试时钟树和时钟约束(见图3)。

使用模块化以改进关键路径性能

设计的某些部分可能比其他部分对于时序更加关键,您需要调节并逐渐改进不执行的部分。有一项技术您可以用于在RTL和网表阶段实现快速调节,那就是将关键路径隔离在单个模块或子项目中,然后您可以不断重复地逐渐改进。另外,您可以强制Vivado布局布线工具将元素紧密放置,从而进一步确保时序QoR。综合期间您可针对该模块使用的功能包括:

•综合之前指定RTL分区(在Synplify软件中,它被称作“编译点”)或者创建分级子项目。

•综合之后隔离(导出)为子项目,由于设计的部分没有使用层级项目管理流程执行。迭代、修复和合并结果。

•使综合软件与Vivado布局布线工具实现通信,将关键路径放置在多个SLR设备的同一个层级内,例如Virtex®-7 2000T FPGA,以避免跨SLR延迟。

第三步:实现最终时序收敛

一般时序可以在综合后和布局布线后报告(见图4)。例如,Synplify软件支持使用TCL命令报告感兴趣的设计特定部分(report_timing)。

为了进一步改进时序QoR,我们建议您关联后综合和后P&R的时序结果,尤其是针对时序关键路径上的给定起点和终点的时序裕量。在Synplify Premier综合软件中,例如您可以并排显示后综合和P&R时序报告,以读取时序结果。

关联工具可并排对比结束点、起始点和所需阶段的状态。根据终点时钟报告路径。而在指定“时序裕量”条件中前后P&R时序没有关联好的路径将标记为“关联不匹配”,以便您采取措施。典型的措施是针对综合工具指定所谓的“布线”约束,其仅在综合阶段加强时序路径约束。例如:

FDC约束输入文件至综合:

set_clock_route_delay {c:clka} 1.4

这些约束使综合在这些路径上“更加努力”地满足时序性能的要求,从而产生更好的关联和QoR。

时序关联性能的好处是,您可以从深层次查看引起问题的准确路径,例如改变每个结束点显示的路径数量。您可以搜索感兴趣的特定时钟或实例,并显示他们的时序路径。此外,还可以对时钟进行比较和显示,以进一步帮助时序关联(见图5)。

您可以看到,您需要完成一些步骤并需要在Vivado Design Suite流程中花一些时间,才能实现更好的时序性能。我们所述的方法可以及早发现时钟约束设置问题,同时还可以提供各种技术以调节和关联设计和RTL中的时序,以快速实现时序收敛。

-

数字IC/FPGA设计中的时序优化方法2025-12-09 3573

-

FPGA时序优化:降低MUXF映射的策略2024-04-01 1877

-

FPGA开发板试用资源汇总 2022.03.31更新2022-03-31 13267

-

时序分析的优化策略详细说明2021-01-14 1588

-

FPGA时序优化最简单的方法详细说明2021-01-12 924

-

FPGA时序优化的四个实例详细说明2021-01-11 938

-

FPGA设计的WNS太高怎么办?五个窍门帮你打赢FPGA优化战役!2018-06-11 6203

-

几个FPGA时序优化简单技巧2018-05-11 11068

-

【InTime试用体验】使用简易、策略选择精确度高的一款时序优化软件2017-07-05 9913

-

Plunify InTime FPGA时序优化专家软件免费试用2017-04-18 2973

-

FPGA设计:时序是关键2014-08-15 1546

-

FPGA的时序优化高级研修班2013-03-27 4986

-

FPGA中的I_O时序优化设计2012-08-12 2388

全部0条评论

快来发表一下你的评论吧 !