基于FPGA的振动信号采集处理系统设计并实际验证

FPGA/ASIC技术

描述

摘要:在振动信号采集和处理系统设计中,信号的处理时间与可靠性决定着系统应用的可行性。本文设计了一种基于FPGA的振动信号采集处理系统,该系统通过振动信号采集电路、抗混叠滤波电路、AD采样电路将电荷信号转化为数字信号送入FPGA,在FPGA处理设计中利用数据流控制方法并行实现了信号的采样和处理,并在数据存储和访问过程中采用时钟时标方法判断信号采样过程中的数据丢失情况,有效提高了振动信号处理的实时性及可靠性。本设计在真实环境中进行了验证,系统运行稳定可靠,满足各项技术应用要求。

振动现象是机械设备运行的伴随过程,结构部件处于工作状态就有振动信号产生,常见故障通过振动和由振动辐射出来的噪声反映。在飞行器的健康监控和诊断过程中,作为提取故障信息的主要手段,振动信号的采集和处理具有特殊重要的意义。

飞行器振动过程的捕捉由于采样点数密集,传感器数量多,传感器之间同步要求高,对于振动采集系统采样速率、采样精度和数据处理能力提出了更高的要求,单纯依靠CPU完成数据采样和处理越来越力不从心。

以FPGA为代表的可编程逻辑器件以其工作稳定、速度快、灵活的可编程能力等特点,获得了越来越广泛应用。本文提出了一种基于FPGA的振动信号采集处理系统;该系统具有实时性高,纠错能力强等特点,采用数据流控制的方法实现了信息的并行处理,可以更加有效的实现多通道振动信号采集;同时为了提高数据的可靠性采用时间标定的方法进行数据的存储和校验。本文第一节介绍了该系统的整体设计方案,第二节、第三节介绍了电荷放大器及和混叠滤波电路的实现方法,第四节着重介绍了FPGA的实现方法,最后介绍了方案的实际应用情况。

1 整体方案

振动信号采集处理系统用于采集轴承的圆周运动所导致的振动过程,振动传感器安装在机械部件上,可以同时采集机械部件各方向的振动量值,为达到振动信号校验和标定的目的,结构部件上安装有光栅传感器,结构部件每转动一周产生一个脉冲信号,该信号与振动信号同时送入振动采集系统用于后续处理。

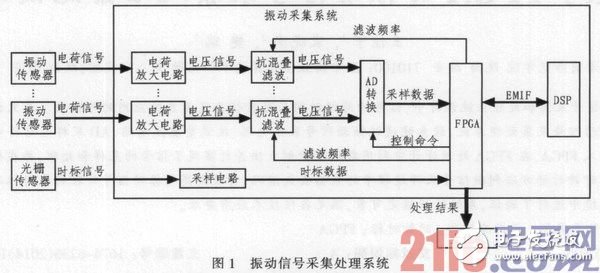

本文所采用的振动传感器为成熟的商用传感器,该传感器输出信号为电荷信号,其量值与结构部件的振动加速度成正比。振动传感器发出的信号经过电荷放大器电路将该信号转变为电压信号,该电压信号经抗混叠滤波处理、AD采样后转化为二进制数据,送入FPGA进行后续处理;光栅传感器产生的脉冲信号,经光电隔离处理后送入FPGA作为时标用于后续处理;DSP从FIFO中读取采样数据,进行分析和处理并根据处理的结果进行显示和告警。方案中AD转换电路采用16位的高精度高速AD转换芯片实现,时标采样电路采用光电隔离器件实现。振动信号采集处理系统原理图如图1所示。

2 电荷放大器电路设计

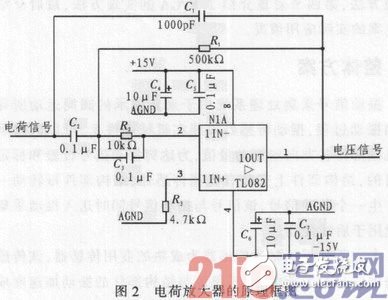

电荷放大器电路原理图如图2所示,放大器采用美国TI公司的TL082芯片。该芯片是采用二次离子注入Bi—FET兼容工艺制作的单片集成高输入阻抗运算放大器。电路中C1为积分电容用于实现电荷信号及电压信号的转化,C1电容的精度对整个电路精度有较大影响,应选用高精度的瓷介电容,电阻R1为反馈电阻主要功能是避免电容C1出现饱和现象,电阻R1阻值需大于等于500 kΩ。为了保护运放TL082,在其反相端串接电阻R2,为避免R2与运放TL082的输入电容构成另一个极点而使运放产生自激振荡。在R2两端并联电容C3实现相位补偿。电容C2和R2、C3并联电路相串联,作用是隔离掉压电传感器的零漂。电容C4、C5、C6、C7用于滤除电源上的干扰信号。

3 抗混叠滤波电路设计

混叠现象由信号中高于采样速率一半的成分引起的,该现象会导致A/D转换后的数据波形失真,产生错误。解决办法是将信号中高于采样速率一半的频率成分滤除。这要求在采样率变化的情况下,滤波器的低通截止频率也要相应调整。滤波器MAX291配合A/D转换器的低通滤波电路可以实现程控抗混叠滤波。该器件是一款巴特沃思低通滤波器。截止频率范围从0.1 Hz到50 kHz。截止频率与输入时钟频率之比为50:1。系统可以通过FPGA分频产生5 Hz到25 MHz的方波信号,控制抗混叠滤波电路实现不同截止频率的低通滤波功能。

4 FPGA设计

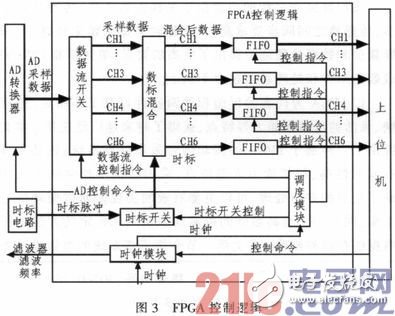

文中FPGA芯片选用XILINX公司的virtex-5系列XC5VFX70芯片,该芯片具有11,200个可配置逻辑块和18KB大小的RAM块296个,能够满足较复杂的逻辑控制和较大的数据存储要求。FPGA控制逻辑包括数据流控制逻辑、FIFO控制逻辑、调度模块、数据存储、数据访问等几部分。调度模块是FPGA的核心控制模块向其他模块发出控制指令,数据流控制逻辑完成了数据由串行数据向并行数据的转化,FIFO控制逻辑完成了FIFO的写入写出控制,数据的存储和访问控制逻辑主要用于数据的校验,FPGA逻辑组成框图如图3所示。

4.1 调度模块

调度模块是控制逻辑的核心负责协调其他模块的工作,调度模块由输入时钟驱动,内部设置定时器周期运行为调度模块的调度提供时间基准,定时器在每一个驱动时钟的上升沿加1,达到最大值时自动清零重新开始运行,当定时器达到某一特定的值时,调度逻辑进行逻辑判断是否需要发出控制指令,如果逻辑判断为真则发出调度指令发送给其他模块驱动其工作。

调度模块有2种工作状态忙状态和空闲状态,调度模块发出启动AD装换指令后处于忙状态,此时调度模块只控制数据流开关进行数据读取和写入的操作,时标数据不会被写入FIFO,此时如果系统收到时标脉冲信号,调度模块指示定时器锁定当时的定时器值,不进行其他操作。当调度模块完成数据输入后进入空闲状态,此时如果系统收到时标脉冲信号或者在前一个忙状态系统收到时标脉冲信号,则调度模块向数据流开关发出指令,数据流开关打开完成定时器时钟的记录。

4.2 数据流开关

采样数据处理的实时性是FPGA设计中首先要考虑的问题,振动信号采集过程中常会由于输入数据量过大,导致后续处理电路处于饱和状态以致数据丢失。为解决上述问题,FPGA通过开关切换的方式将数据分别送入不同的线程进行处理。振动传感器输出数据格式如下:(A1B1C 1D1E1F1),(A2B2C2D2E2F2),……(AN BN CN DN EN FN),A、B、C、D、E、F分别代表不同方向的振动量值。采用单通道的数据处理方式时,程序首先需完成数据的区分工作,然后完成6次数据处理过程,当一次需要处理数据量较大的情况下,系统会产生较大的延迟并导致后续数据的丢失。为降低数据处理电路的负担,采用数据流开关将振动传感器输出数据分别存储在不同的通道中通过数据流控制开关后数据格式如下:

通道1:A1、A2……AN;

通道2:B1、B2……BN;

通道3:C1、C2……CN;

通道4:D1、D2……DN;

通道5:E1、E2……EN;

通道6:F1、F2……FN。

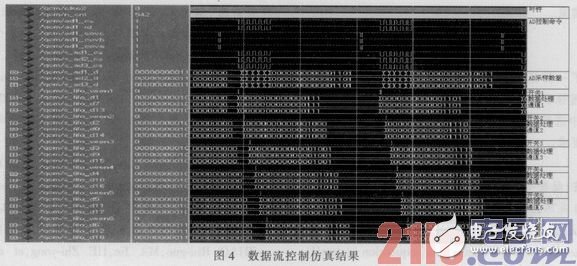

仅需处理N个数据就能满足系统要求,系统对于处理能力的要求相应降低。数据流控制仿真结果如图3所示。图中AD采样数据为连续的单通道输入数据,经过AD控制命令和通道开关的控制后被分别发送到6个数据处理通道进行后续处理。

4.3 FIFO的控制

振动数据存储在由XILINX提供的FIFO软核中。FIFO核的存储深度、数据宽度、标志位设置、存储类型和读写端口速率可以在FIFO生成时进行设置,FIFO模块生成时占用FPGA内部的BLOCK RAM,即使存储容量很小的FIFO也会占用整块BLOCK RAM。FIFO端口包括输入输出端口、读写使能、读写时钟及空满标志几部分。其中,输入输出端口与数据总线连接用于数据传输;读写使能由控制逻辑驱动完成一次读写操作;读写时钟信号完成读域或者写域所有信号的同步;满标志表明由于该FIFO处于满状态,写操作将被忽略,空标志表明FIFO处于空状态,读操作将不能获得正确的数据。

FIFO控制逻辑进行数据写入操作时首先判断FIFO是否处于满状态,如果FIFO处于满状态,先从FIFO中读出一条数据,然后将新数据写入FIFO中。如果FIFO不处于满状态则直接进行写操作。FIFO读操作的时机由DSP控制,DSP内的程序首先读取空状态寄存器判断FIFO中是否存有数据,如果寄存器显示FIFO为空则取消读操作,否则就从FIFO中读出需要的数据。IP核对使能信号的访问时序有着严格地要求,使能信号必须于读写时钟完全同步,而且控制逻辑将使能信号的长度控制在一个读写时钟周期内。

4.4 数据的存储

振动采样数据的数据量非常庞大,一旦出现错位将无法完整复现信号的原始状态,因此在对数据进行存储的同时,对数据进行时间标记也是十分重要的。时间标记在一个完整的记录周期结束时进行,调度模块控制时标开关在所有的FIFO中存入时标信息,FIFO中存储在时标以前的数据均为本周期的数据,存储在时标信息以后的数据均为下一周期的数据,时标及数据记录格式如表1所示。表中D15,D14位是保留位用于功能扩展,D13,D12是表明存储数据是时标信号(01、02),或者采样数据(00)。

4.5 数据的访问

DSP进行数据还原时,访问程序依据采集顺序先从本周期起始通道开始依次读出采样数据,当访问程序读取到第一个时标数据后本周期数据读取完毕,访问程序继续读取后续通道的时标信息,直至获得所有通道的时标数据后表明本次数据访问过程结束,如果访问程序连续获得了所有通道的时标信息表明采样数据为完整有效的数据,否则说明在采样过程中存在数据丢失的现象,数据不可信不能进行后续处理,如果出现数据丢失现象则访问程序将所有通道时标数据读出后本次访问结束。

5 结束语

文中设计了一种基于FPGA的振动信号采集处理系统,通过数据流管理等手段实现振动信号的实时采集处理,本设计在真实环境中进行了验证,系统运行稳定可靠,各项性能指标满足技术要求。

-

基于FPGA的多普勒测振计信号采集与处理系统设计方案2013-10-29 3189

-

一种基于FPGA的振动信号采集处理系统设计介绍2019-07-01 1823

-

基于FPGA 的交流信号采集与处理系统2009-05-16 755

-

基于FPGA和DSP的光纤信号实时处理系统2009-06-19 922

-

高精度振动信号处理系统的研究2009-08-15 440

-

基于FPGA的雷达信号处理系统设计2015-10-30 1124

-

基于FPGA的玻璃缺陷图像采集预处理系统设计2016-08-30 716

-

基于FPGA+DSP实时图像采集处理系统设计2017-01-03 1269

-

基于LabVIEW的信号采集处理系统_金爱娟2017-03-18 1056

-

基于DSP的数字信号采集处理系统设计2017-10-19 1041

-

基于FPGA的振动信号采集系统设计及实现2017-11-17 8695

-

基于FPGA的多路卫星信号处理系统设计实现方案及验证2017-11-18 5522

-

FPGA信号处理系统的散热解决方案介绍2019-04-23 5127

-

基于FPGA+DSP弹载SAR信号处理系统设计2021-12-27 998

-

基于Simulink代码生成的FPGA信号处理系统仿真验证平台2022-11-04 3985

全部0条评论

快来发表一下你的评论吧 !