基于FPGA和处理器的集成式电源管理方案

FPGA/ASIC技术

描述

该解决方案在单芯片IC上集成多个开关稳压器、LDO和监控/看门狗定时器

由于机器视觉系统的尺寸不断变小,而这些系统的处理能力持续飞速增长,电源管理正进一步成为新机器视觉系统的重要设计因素。目前,最新的FPGA和用于机器视觉系统的处理器有一个共同的要求,即需要多个供电轨供电。通常用于这些FPGA和处理器的电源要求使用多个分立式开关稳压器和LDO。

在这些分立式电源设计中,使用开关稳压器来为高电流内核电轨供电,使用LDO为对噪声更敏感、低电流的时钟供电。更多新的集成式电源解决方案正在开发中,以便满足更小的PCB面积要求,如机器视觉系统中。这些新的多通道集成式电源管理解决方案在单芯片IC中集成多个开关稳压器、LDO和监控/看门狗定时器,极大地缩减了用于FPGA的典型多电轨电源解决方案的尺寸、成本和设计时间。随着客户设计周期的不断缩短,产生多个电轨的单电源IC变得越来越重要,它们极为灵活且易于配置,因此单个多通道IC可快速用于不同的应用或配置中,轻松减少设计时间以及新产品的上市时间。(见图1。)

使用uPMU为FPGA和处理器供电的优势有:

经济有效的解决方案

电路板占位面积小

可轻松实现时序控制和电压跟踪

低噪声、开关错相工作,减少EMI

无需使用外部同步信号

使用简便,不需要具有太多的电源专业知识

更少的元器件、更高的可靠性

让我们详细看看其中的四大重要优势:

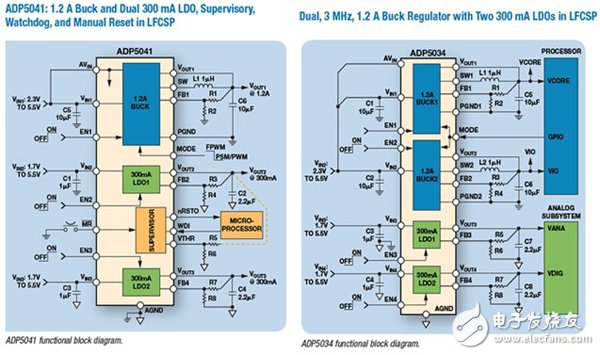

解决方案尺寸

将多个开关降压稳压器、LDO、电源监控器和看门狗功能集成到单芯片解决方案中,可以大幅缩小多轨电源解决方案的PCB面积。ADP5034就是一个很好的范例,它是一款集成两个300 mA LDO的双通道降压稳压器,采用24引脚LFCSP封装。ADP5034在单个封装中集成多个开关稳压器和LDO,实现新一代高集成度多路输出稳压器,只需非常小的电路板空间。集成开关稳压器以3MHz开关频率工作,允许使用非常小的片式电感,极大地减少解决方案的整体尺寸。ADP5034解决方案的整体尺寸仅为72 mm2。

易于使用

新产品的设计周期越来越短,初始阶段易于设计、未来又能根据设计要求轻松修改的新型电源管理解决方案对于保证新产品发布日期日益重要。ADP5041多路输出稳压器提供一个降压稳压器和两个300mA LDO,并集成上电复位功能和看门狗定时器以支持基于高可靠性处理器的系统。ADP5041的所有集成稳压器都有专用使能引脚,赋予电源设计工程师极大的灵活性,可以通过硬件使能或禁用各稳压器,无需任何软件开销,并且可以轻松控制三个电源轨的上电时序。各稳压器的输出电压利用外部电阻分压器设置,电源设计工程师同样可以利用这一点来轻松快捷地更改输出电压,从而满足原型开发和新设计重用对不同输出电压组合的需求。多路输出稳压器的各集成稳压器都有独立的使能引脚和电阻可编程的输出电压,有助于降低电源设计的复杂度,缩短设计时间,加快新产品上市。

更少的元器件、更高的可靠性

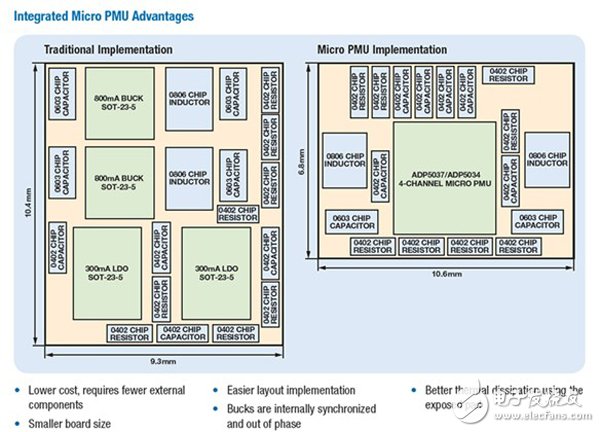

图2显示分立式双通道降压稳压器和双通道300 mA LDO组成的电源解决方案示例布局,以及单芯片ADP5034多路输出稳压器示例布局。分立电源解决方案需要将22个器件贴装在97mm2 PCB面积上,而ADP5034解决方案只需将19个器件贴装在72mm2 PCB面积上。ADP5034解决方案所需的PCB面积减少35%,并且节省了贴装3个器件的成本。如果考虑到采购、仓储、贴装、检查成本,则在PCB上贴装1个器件的成本可能高达3美分。PCB上贴装的器件数目越多,生产出残次品的风险也就越大;通过减少PCB上贴装的器件数目,便可降低生产成本,同时提升生产工艺的可靠性。

低噪声解决方案

开关降压稳压器上的专用MODE引脚可以通过微处理器GPIO端口方便地控制,迫使开关稳压器以恒定PWM模式工作。在轻负载下,开关稳压器以突发模式工作会产生宽带噪声,如果受电电路(收发器、ADC、音频)对宽带噪声敏感,那么这种控制就是必需的。集成到这些多路输出稳压器中的LDO具有1.7 V至5.5 V的输入电压范围,配合一个降压稳压器使用时,低输入电压使得LDO能够提供极高效率的低噪声输出。例如,降压稳压器可以用作前置稳压器,实现5V输入到1.8V输出的高效率压降,然后将此1.8V电压施加于LDO的输入端,以提供极低噪声的1.2V输出电压,从而以非常高的效率从5V初始输入为极敏感的模拟电路供电。集成LDO具有高PSRR(即便Vin-Vout裕量较低)和低内部噪声,稳压器之间的串扰已被降至最小。为噪声敏感型电路供电时,所有这些特性都很重要。

-

处理器的电源管理原理2009-10-22 4472

-

多核处理器提升电源效率方案2018-09-25 1559

-

Xilinx Spartan 6 FPGA集成式电源解决方案2018-11-09 2991

-

基于FPGA应用设计优秀电源管理解决方案2019-05-05 2893

-

便携式应用处理器的电源管理技巧2009-04-27 505

-

采用FPGA处理器的刀片管理控制器原理及设计2010-03-17 498

-

处理器电源管理解决方案设计要点2010-07-05 489

-

便携式应用处理器的电源管理解决方案2010-04-20 866

-

基于FPGA的NoC多核处理器的设计2017-11-22 5459

-

应该要知道如何选择嵌入式处理器及其电源管理的解决方案2019-04-23 852

-

恩智浦处理器的电源管理解决方案2021-05-12 1080

-

德州仪器的高效集成电源(适用于NXP处理器和Xilinx FPGA)2022-10-31 741

-

浅谈FPGA与处理器技术的集成历史2023-04-25 706

-

适用于ARM Cortex®—A53处理器和 FPGA的集成电源管理IC TPS65220数据表2024-03-06 490

-

STPMIC1:高度集成的微处理器电源管理IC2026-02-28 219

全部0条评论

快来发表一下你的评论吧 !