教你如何为Xilinx设计创建创建自定义XBD文件

FPGA/ASIC技术

描述

创建自定义赛灵思板级描述(XBD)文件不仅有助于节省时间,而且还能确保设计项目按计划推进。为您设计的任意开发板创建一个XBD文件并非难事。

FPGA厂商推出了许多出色的评估板和专用开发板,既可用于评估FPGA,甚至还能作为开发系统的基础。不过有时设计项目需要的功能可能在评估板上并未提供,或者需要一款较小型的终端系统。在此情况下,设计团队必须构建一款定制开发板。

赛灵思每款评估板都配套提供一份XBD文件,其列出了FPGA的板载外设、配置、控制寄存器和引脚。XBD文件不仅可确保设计团队工作有条不紊地开展工作,而且还有助于他们为当前乃至未来在开发板上实现的设计制定最佳策略。

当然,如果您创建的是定制开发板,那就无法获得赛灵思提供的XBD文件支持。但是花时间开发自己的XBD文件还是值得的。专门制作的XBD文件能帮助设计团队管理项目,简化设备驱动程序和固件开发。所幸的是,经过一番研究和努力,用户不费周折就可以为自己的开发板创建一份自定义XBD文件。(对使用Vivado设计套件的用户而言,赛灵思在随Vivado设计套件2014.1版本一并推出的新型实用工具Board Manager中提供了XBD优化功能。如欲了解更多信息,敬请查阅“Vivado设计套件用户指南” http:/china.xilinx.com/support/docu-mentation/sw_manuals/xilinx2013_3/ug898-vivado-embedded-design.pdf 。)

下面我们来看看开发自定义XBD文件的方法之一。就本实例设计而言,我们针对采用Virtex®-5 FX30T FPGA的定制开发板创建XBD文件。

我们从赛灵思和分销商安富利(Avnet)提供的技术文档入手。由于我们必须自己编写XBD文件,因此必须遵循XBD语法。赛灵思已在平台规范格式参考手册中介绍了XBD语法(敬请查阅: )。

您的定制开发板极可能需要串行通信(RS232和RS422)、模数转换器(ADC)、数模转换器(DAC)、RAM和闪存存储器。正好赛灵思和安富利的评估板也提供这些外设,所以找到有类似部件的开发板并参考其相关XBD文件就能加快自定义XBD文件的开发进程。

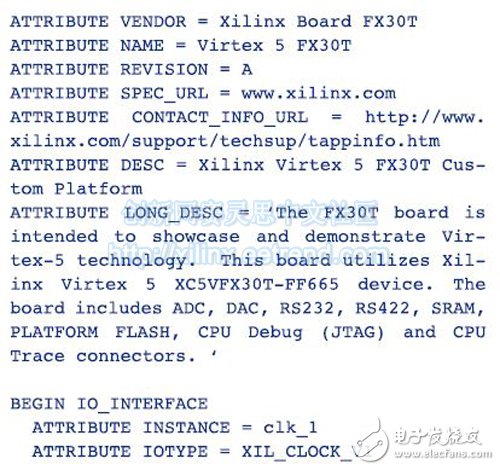

每个XBD文件都有不同的模块,其定义了开发板支持的FPGA接口,并且每个模块都有一系列属性、参数和端口。因此文件第一项记录就是全局属性命令、厂商信息、开发板名称及其版本号、辅助Web URL以及开发板描述的简明版本和详细版本。

文件的本地属性命令在BEGIN-END模块之间进行定义,并用特定格式表达,这也可以查阅平台规范参考手册。就本实例来说,我们将使用面向Virtex-5FX30T FPGA的ISE设计套件12.4版本。Virtex-5FX30T FPGA含有可配置逻辑单元和PowerPC® 440硬核。

除了FPGA之外,定制开发板将根据设计需要还包括不同外设,如串行通信接口(RS232、RS422)、ADC、DAC、SRAM等。您可通过使用串行通信专用IP模块来满足多个UART需求。例如,您可用外部存储器控制器(EMC) IP实现SRAM与FPGA的连接,并用通用I/O (GPIO) IP将ADC和DAC与FPGA相连接。

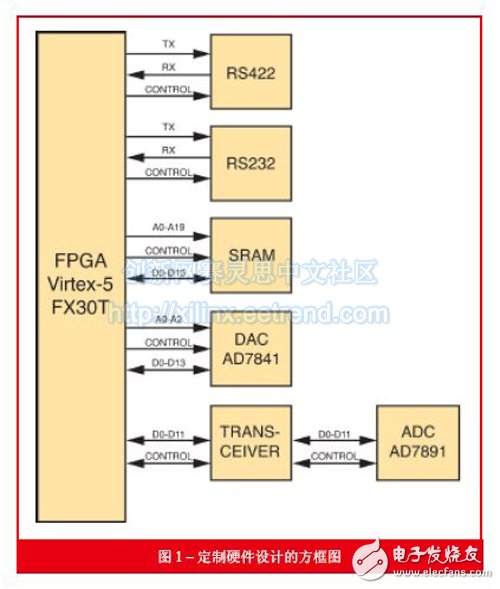

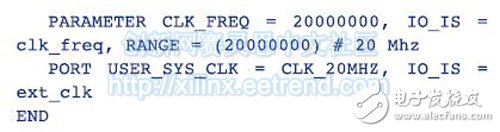

在我们的实例设计中,我们制作自定义XBD文件来满足器件数据手册中列出的功能及器件需求。FPGA的输入时钟信号为20 MHz。处理器运行频率为200MHz,而处理器本地总线(PLB)工作频率为100 MHz。根据上述信息,我们能够保证维持本地器件驱动时序。图1给出了定制硬件的方框图。

让我们开始创建自定义文件。首先从全局属性命令着手,随后是时钟信号,这是所有开发板都必须遵循的步骤,如下所示:

接下来我们要在文件中逐一列出开发板的所有外设。(对每个外设模块详细编码信息感兴趣的读者可查阅配套提供的PDF文件《定制开发板XBD编码详情》,敬请访问官方网站。)

数模转换器

让我们从Analog Devices提供的数模转换器AD7841开始,该数模转换器(DAC)具有8个通道、3条地址线和14位数据线以及一些可处理器件功能的控制信号。该器件通过赛灵思的GPIO IP核与FPGA相连。而器件的地址线(A0-A2)则与处理器地址线相连。

该DAC具有4种控制信号:LDACN、CSN、WRN和CLRN。组建这些信号有两种方法,您既可以给每个信号分配一个位,也可以直接设计一个4位寄存器,具体取决于您的应用所需的信号处理方式。该DAC为14位D0-D13。

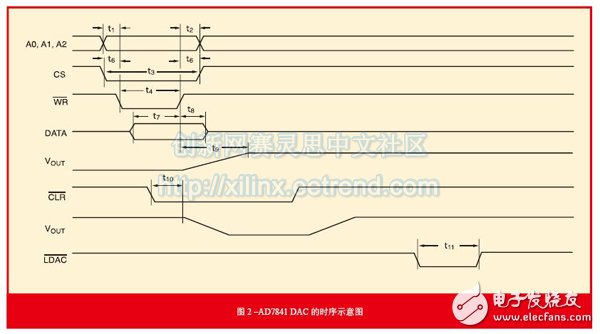

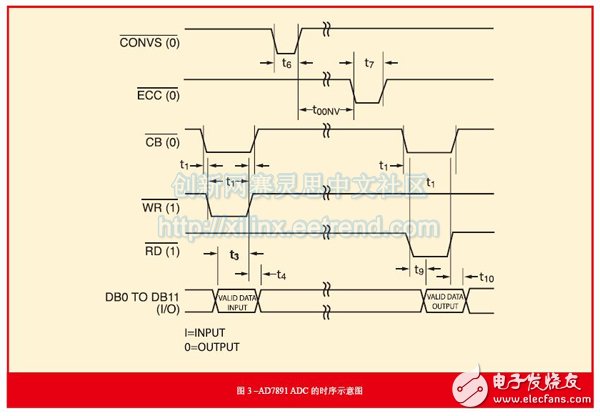

现在我们已经了解XBD文件中所列首个器件DAC的一个细节,下面我们来了解一下如何写入固件。在开发器件驱动程序时,我们应认真研究数据手册和时序示意图。时序示意图如图2所示。

器件数据手册说明了用户必须阅读时序示意图并生成控制信号。时序信息t0-t11完全遵照Analog Devices提供的数据手册(AD7841)。第一步要设置信号方向为出口,然后通过写入1到相应地址将其拉高。例如,将方向LDACN信号设为出口,然后通过以下语句将其拉高:

信号之间的延迟可用“for”循环,也可选择“NOP”指令来实现。每个信号的序列和建立-保持时序也同样重要,这些规范均在器件数据手册中予以提供。这里,当处理器运行频率为200 MHz时,每个增量相当于5纳秒。

借助赛灵思EMCIP核与XBD文件,存储器的接口连接和控制变得轻松简便。我们在器件数据手册中找到了时序约束,并将其列在XBD文件中。

通信与SRAM接口

我们将使用赛灵思的XIL UART IP将RS232和RS422驱动程序IC与Virtex-5 FPGA实现接口相连。我们针对RS422和RS232通信分别选择了MAX3079和MAX3237这两款Maxim器件。我们通过GPIO IP核来生成RS422 IC的控制信号。

就存储器而言,我们选择赛普拉斯的静态RAM,即CY7C1061BV33器件,从而利用赛灵思外部存储器控制器IP核(XIL_EMC)将其连接到FPGA。借助该IP核和XBD文件,存储器的接口连接和控制变得轻松简便。我们在器件数据手册中找到了时序约束,并将其列在XBD文件中。由于赛灵思IP核足以处理该存储器,因而无需使用单独的器件驱动器。

ADC接口

在该设计中,将ADC与FPGA进行接口相连是一个难题,因为来自不同传感器的所有输入模拟信号都在±10V范围之内。为了满足实例板的功能要求,我们选用了Analog Devices的AD7891-1。该ADC具有8个通道和一个12位数据总线,并提供可选的串行和并行接口。在该设计中,经实践证明并行接口是更好的选择。

该器件工作在5V输入上,由于FPGA I/O电压为3.3V,因此我们的设计需要可实现与FPGA接口相连的收发器。接下来我们将会把此收发器作为缓冲器。收发器在一侧连接到FPGA,而在另一侧则连接到ADC。FPGA可处理缓冲器的控制信号。我们需要认真处理器件的方向引脚和输出启用引脚,以便控制FPGA到ADC的数据流,反之亦然。可将器件控制信号归组为5位寄存器。

器件的转换端(EOCN)应在自定义XBD文件中分开列出,因为这是一个非常重要的信号。EOCN表明转换已经完成且新数据可用于FPGA进行处理。

缓冲器接口

在本设计中,我们选择了德州仪器的SN74ALVC164245电平位移收发器作为缓冲器。其是一款16位非反相总线收发器,拥有2个单独的端口及供电轨。可将器件的端口B与5V ADC连接,而端口A则与3.3V FPGA连接。该配置支持从5V到3.3V的信号转换,反之亦然。

方向引脚设为低,将端口B的数据传输至端口A。若设为高,则情况正好相反,端口A的数据将被传输到端口B。要读取ADC的数据,需要将输出使能(OEN)和方向(DIR)引脚设为低。在写入操作中,FPGA将向ADC发送指令,且方向引脚为高而输出启用引脚为低。在我们的实例设计中,我们将缓冲器的输出启用引脚进行拉高,从而避免了总线冲突。我们在该设计中使用了两个缓冲器和两个ADC。

图3为并行接口模式的时序示意图,我们用它来生成控制信号。从t0到t11的信号时序通过Analog Devices的器件数据手册引用。

您可用Notepad或WordPad等任何编辑程序创建或修改该文件。您必须将此文件保存扩展名为.xbd的格式文件。完成后,文件必须保存到特定的路径下,当创建新项目时,对EDK工具直接可见。启动新项目时,应为定制开发板选择该文件。

例如,假设开发一个名为“customboard”的开发板,该开发板对EDK工具可见,您应当遵循特定的目录结构要求。这是很重要的一步。我们的实例“customboard_RevX_vX_X_0.xbd”一旦创建后,必须保存到以下目录下:

示例路径:

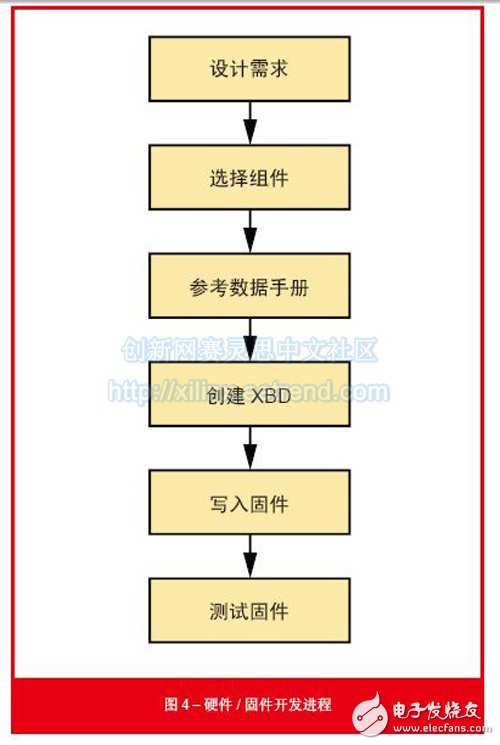

此外,针对任何应用的硬件或固件开发也应遵循特定的步骤,如图4所示。

加速开发进程

打造定制硬件以便为自己的特定应用开发器件驱动程序,这对于嵌入式设计人员来说是一项充满挑战性的工作。赛灵思提供了大量有关开发过程的文献资料,也为开发工作提供了通用板级描述文件。您可轻松定制并修改该文件以满足您自身定制硬件的需求。硬件配置如需任何修改或改动,您只需参考一个统一的文件即可,并将所有器件相关的改动整合到该文件中。这样,自定义XBD文件就能提高生产力,加速开发进程。

- 相关推荐

- 热点推荐

- Xilinx

-

使用Python/MyHDL创建自定义FPGA IP2026-04-09 275

-

MCUXpresso SDK创建自定义清单2026-04-07 321

-

如何快速创建用户自定义Board和App工程2025-02-08 2047

-

创建自定义的基于闪存的引导加载程序(BSL)2024-09-19 414

-

创建自定义Kria KV260加速ML应用程序2023-06-26 1332

-

教程 2:添加特征-自定义配置文件创建2023-03-15 798

-

在16x2 LCD显示器上创建自定义动画2022-10-24 1310

-

如何为LCD1602显示器创建自定义字符2022-10-21 2450

-

如何在TensorFlow2里使用Keras API创建一个自定义CNN网络?2021-04-15 2979

-

Glib创建自定义事件源的方法2020-06-22 3949

-

有什么软件可以创建一个XBD文件?2019-08-16 1257

-

利用SDSoC创建自定义硬件2018-11-26 3174

-

Qt自定义窗口部件的创建2018-09-09 2794

-

在NI Multisim中创建自定义元器件2016-07-20 1685

全部0条评论

快来发表一下你的评论吧 !