MicroBlaze如何与ZynqSoC和平共存

FPGA/ASIC技术

描述

赛灵思 Zynq-7000 All Programmable SoC已具有很强的板载处理能力。但是Zynq应用处理单元(APU)中强大的双Cortex-A9处理器和相关外设的存在并不妨碍您在同一封装中添加一个或多个MicroBlaze处理器,只要能让应用受益就好。

为什么要给处理功能已经很强大的解决方案添加MicroBlaze呢?首先就是可靠性的问题。单线程会大幅提高可靠性。您可以针对计算密集型任务为每个Cortex-A9都布置一个线程,而且能根据需要为其它线程实例化任何数量的MicroBlaze处理器。其次,您可将任何杂务交给MicroBlaze去完成,让处理功能强大的Cortex-A9去执行最需要它的工作,充分发挥其用武之地,从而节省数个关键的工作周期。

下面这个例子能反映以上两种情况。设想一下,一个任务需要长期高强度计算,同时还要监控用户输入。这里,MicroBlaze可管理用户输入(频率较低、计算强度不高),并写入APU存储器空间,这样APU闲置时(也就是完成了处理任务时)就能看看接下来需要处理什么信息。

一旦您决定在基于Zynq的设计中添加一个MicroBlaze处理器,马上就会发现一些问题。首要问题就是APU如何与MicroBlaze通信,哪些处理器系统(PS)资源可供MicroBlaze使用。包括ZC702和Zedboard等在内的许多开发板将许多外设直接映射到与处理系统相连的引脚。可编程逻辑(PL)中,这些引脚不能直接访问MicroBlaze。处理系统还包含多种不同定时器和中断资源。有什么办法能从MicroBlaze领域访问这些资源吗?

PS与PL之间的接口

处理器系统和可编程逻辑紧密结合,这意味着Cortex-A9、窥探控制单元(SCU)、PS外设、时钟管理及其它功能与可编程逻辑之间存在多个紧密的集成连接。事实上,PS和PL之间共有6种不同类型的互联,您可将这些互联类型彼此结合使用。此外,许多路径是对称的,也就是说PC能启动到PL的连接,而PL也能启动到PS的连接。

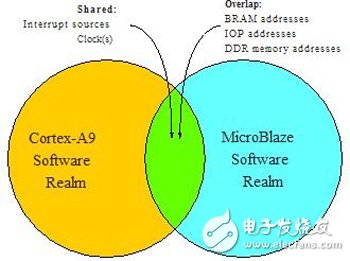

图1:PL中PS和MicroBlaze的边界是一片雷区吗?二者能否共享资源?

赛灵思公司目前提供的应用指南、用户指南和白皮书等大量资料均介绍了作为设计“核心”的Zynq-7000 APU如何利用可编程逻辑来访问存储器、基于PL的外设和硬芯片外设(如PCIe模块、BRAM、DSP48和千兆位级收发器等)。要分析MicroBlaze如何成为其自身领域的主导,逻辑上的第一步就是看看6个接口变量,首先从通用、高性能和加速器一致性端口这三类AXI接口入手。

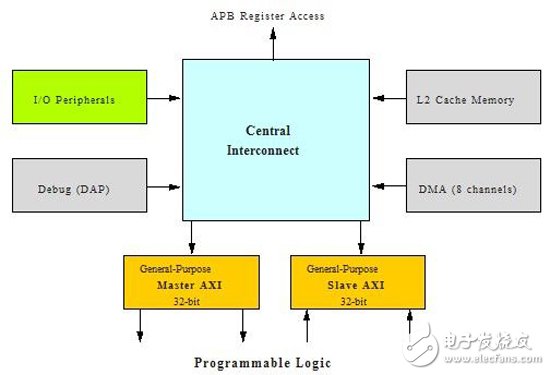

PS有两个连接到PL的主AXI通道和两个由PL启动的从通道(图2)。这里的“主”是指AXI通道为发起方,能启动数据交换,而“从”在只能用于响应到达的数据。主AXI通道通常用来与PL中的外设通信。从AXI通道负责响应PL的请求,其中可能包括MicroBlaze处理器所执行的事务处理。这些AXI通道连接到PS的中央互联,可路由到许多资源。

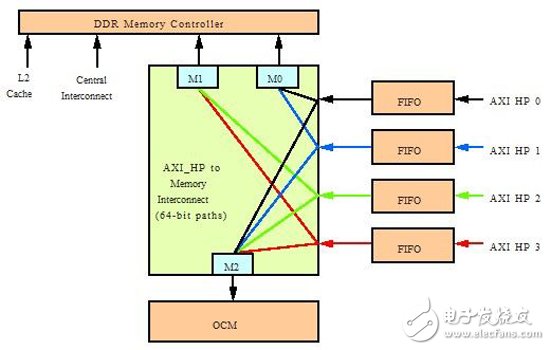

此外,还有4个高性能(64位宽)AXI通道连接点。从PS角度来说,所有这4个通道均为从通道,连接至PS中的存储器接口子系统(图3)。这4个通道的目的就是让PS中的主设备启动DDR存储器事务处理。

这种存储器互联和DDR存储器控制器是所有资源到DDR存储器的门户。虽然Cortex-A9处理器的优先级通常高于从AXI连接,但4个AXI连接中每个都有一个“现在为我服务”信号,能让发出该请求的通道获得优先级。未断言该信号时,架构、采用循环机制确定哪个请求方有权访问特定类型存储器。

加速器一致性端口(ACP)是另一种PL的32位AXI PS从连接。ACP的独特之处在于它直接连接到SCU中。SCU的任务就是确保L1、L2和DDR存储器之间的一致性。采用ACP,您能访问PS中的每个Cortex- A9处理器的高速缓存存储器,而不必担心与主存储器中的数据同步问题(硬件会自动处理好这个问题)。该功能不仅可大幅降低设计负担,而且还能显著加速处理器与PL之间的数据传输。

图2:到处理系统中央互联的简化连接

图3:到DDR存储器控制器和片上存储器(OCM)的简化连接

除了AXI链接之外,可扩展多路输入输出(EMIO)信号也可用于路由许多PS的硬外设直至PL,以便访问封装引脚。只有54个封装引脚直接连接到PS,不过PS的硬外设可使用的引脚数量大大超过54个。EMIO是PS硬外设和PL之间的通道。这些I/O信号可直接路由到PL可用的封装引脚,而您也可利用这些引脚与PL中兼容的外设进行通信。

PS和PL之间另外的各种杂项信号可以分为5个基本类:时钟与复位、中断信号、事件信号、空闲AXI与DDR存储器信号,以及DMA信号。

* 时钟与复位:PS为PL提供4个独立的可编程频率。通常这些时钟之一用于AXI连接。每个时钟域都有自己的域复位信号,可重设与该域关联的任何器件。

* 中断信号:PS中的通用中断控制器(GIC)负责收集所有可用源的中断,包括PS外设的所有中断源和可编程逻辑的16个“外设”类型中断。此外,还有4个连接到CPU(IRQ0、 IRQ1、FIQ0和FIQ1)的直接中断。来自PS外设的共28个中断可提供给PL。

* 事件信号:这些“带外”异步信号说明PS的特殊情况。PS提供一系列信号用于表明哪个CPU进入待机模式,哪个CPU执行了SEV(“发送事件”)指令。PS可用事件信号从WFE(“等待事件”)状态中唤醒。

* 空闲AXI与DDR存储器信号:PS的空闲AXI信号用来指示PL中没有未处理的AXI事务处理。该信号由PL驱动,是用来启动PS总线时钟关断功能的条件之一,确保所有PL总线器件均处于闲置状态。DDR紧急/仲裁信号用来向PS DDR存储器控制器的4个AXI端口DDR仲裁表示关键的存储器处于紧张状况。

* DMA信号:PS的直接存储器访问(DMA)模块通过一系列“请求和确认”信号与PL从设备通信。

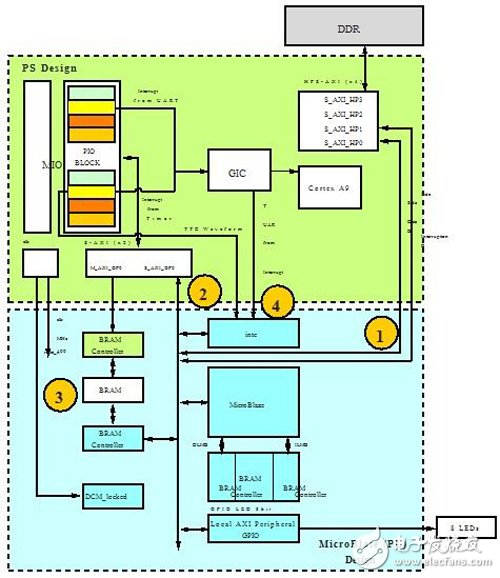

图4:硬件设计实例方框图

访问DDR存储器

我们下面来分析一个设计实例,该实例涵盖了典型MicroBlaze用户可能涉及的几个常见的需求,比如如何访问DDR存储器;如何使用PS IOP中的外设;如何在MicroBlaze和PS之间传输数据块;如何在MicroBlaze和PS之间实现事件同步等。图4给出了解决每种问题的方法(分别标识为1、2、3、4)。

访问DDR存储器最简单方法就是通过4个高性能(HP)AXI接口的一个或多个连接(方框图右上方)。4个64位宽端口可供可编程逻辑访问。您首先必须启用一个端口,然后连接AXI到端口。MicroBlaze采用AXI4-Lite接口,而HP端口则应用作全AXI4连接。所幸的是,赛灵思设计工具可自动弥补,无需任何手动修改就确保实现成功连接。方框图中①显示了该连接。这类连接的优势在于创建起来非常简单,而DDR存储器对设计来说就是常规存储器。而不足之处在于,AXI-Lite不支持突发模式,而且只有32位宽,因此会丧失不少性能。

还可通过其它方法将基于PL的外设连接到DDR存储器,比如采用DMA控制器,同样也可采用HP端口。虽然这种连接机制更复杂,但能提高大数据块的传输性能。

在PS中启用UART和三重定时器/计数器(TTC)。M_AXI_GP0连接的BRAM控制器位于PL中,但从概念上说是PS设计的组成部分(实际上也是PS设计的一部分)。

MicroBlaze作为设计的另一部分采用BRAM提供64KB的整合代码和数据空间,供MicroBlaze专用。显然,我们能连接这些端口到PS的HP端口以访问DDR存储器,不过这样做会让实现工作变得更复杂。

有3个连接到MicroBlaze的标准外设:一个是负责接收TTC的PWM波形输入并将其解释为中断源和接收的UART字符中断的中断控制器;一个是负责驱动ZC702开发板上8个LED的GPIO,第三个是用于连接到PS所连接的同一BRAM的B侧的BRAM控制器。此外还有两个连接:一个是到S_AXI_GP0的连接,用于实现PS内部外设的寻址;另一个到高性能端口的连接,可让MicroBlaze访问DDR存储器部分。

外设、数据块和同步

到PS S_AXI_GP0端口的连接是访问可编程系统IOP模块的关键(图中的②)。S代表这是一个从端口,也就是接受PL中的组件启动的事务处理。在MicroBlaze和S_AXI_GP0端口之间建立连接时,IOP模块可从0xE000_0000扩展到0xE02F_FFFF,这意味着MicroBlaze地址空间中的其它外设都不能重叠于这段地址,而这段地址将供处理器共享。

与此同时,许多机制均支持MicroBlaze和PS之间的数据块传输。往返DMA和DDR以及DMA和片上存储器(OCM)就是两个可能性。另一种就是在设计实例中实现的机制,其使用双端口BRAM(图中的③)。PS为BRAM控制器一侧主设备,而MicroBlaze则为其另一侧主设备。软件负责管理分区和共享BRAM存储器空间的使用,因为两侧都有权对存储器的全部内容进行全面读取和写入。

最终问题涉及如何在MicroBlaze和PS之间同步事件。PS包括大量定时器,您能对PL中任意数量的定时器实例化。设计实例中采用了一个TTC外设中的一个通道来生成100毫秒的脉冲信号(图中的④)。这里的关键是要认识到TTC生成的波形能从PS以外访问,但TTC中断只能在PS以内可用。您可用波形本身作为MicroBlaze中断,从而规避这个问题。此外,您也可采用硬件定时器(AXI定时器或用户编码的定时器)为PS和MicroBlaze提供中断。

图5:独立软件域和重叠项

与任何嵌入式设计一样,您要考虑的不光是硬件实现问题,还要考虑软件支持。对本例而言,要考虑两个处理器的重叠区域(如图5所示)。

就硬件而言,要把系统视为两个相互交叉的嵌入式设计:PS和MicroBlaze。我们的参考设计可让PS为其自身和MicroBlaze生成时钟信号并提供中断。MicroBlaze可使用这些信号,但不能影响或对其修改。PS和PL共用PS的IOP模块、DDR存储器与控制器以及常见的双端口BRAM。

从地址映射角度看,IOP地址固定在硬件中,不能修改。MicroBlaze和Cortex-A9必须对外设使用相同的地址。技术参考手册在这方面做了详细说明,非常具有参考价值。技术参考手册分两部分对解决设计中的外设问题进行了阐述。这部分中的所有寄存器都列出了地址和简介,管理两个处理器之间的资源则是用户要开展的一项任务,要避免数据冲突,避免资源不足等。

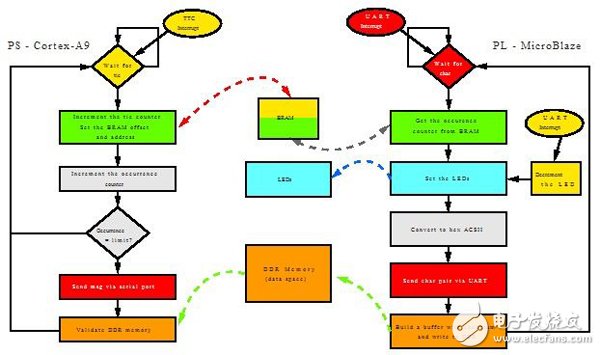

图6:Cortex-A9应用和MicroBlaze应用流程图

采用DDR存储器及其控制器比较简单,因为DDR存储器控制器能管理冲突问题,而且提供适当的启发避免任何请求方无法获得数据。由于这不在用户控制下,时延可能会有些难以预见。

常见的BRAM采用相同的较低地址位,不过针对该模块的每个处理器存储器空间的位置可用Xilinx Platform Studio的地址标签来选择。跟以前一样,数据冲突、同步和存储器分配也是读者要完成的工作。

我们的软件设计实例更主要的目的是演示连接Cortex-A9和MicroBlaze的过程,而不是要做任何实际的工作。一些方法将演示这方面的可能性。

图6左侧所示的Zynq-7000应用是一款简单的设计,其采用赛灵思单机版板支持包。它运行的程序很大程度上让处理器保持空闲状态,只是周期性地通过串行端口发出T字符表明自己仍在工作。此外,它会计算T的次数并将计数统计保存在BRAM中,与MicroBlaze共享。

MicroBlaze应用也运行单机版板支持套件。这样就能支持中断,每次串行端口上出现字符,MicroBlaze就把字符缓存起来,并发送对应的Hex-ASCII到PS IOP模块的串行端口。此外,它会构建接收字符串,每收到一个字符都保存在DDR存储器中。收到回车后,将计算校验和,并在字符串后直接添加到DDR存储器。BRAM预先设定的位置处设置标记,当Cortex代码“看到”标记时就从DDR存储器读取字符串,并验证校验和。如果校验和准确,MicroBlaze发出“+”,否则发出“X”。

简而言之,设计实例证明MicroBlaze和Zynq7000 PS完全能和平共处。AXI连接点数量很多,使MicroBlaze(或PL中的任何组件)能方便地访问IOP模块中的外设、OCM和DDR。可编程逻辑能方便地访问IOP模块的中断,而PL中能生成一系列中断并发送给PS。软件协调和定义良好的行为是避免争抢情况和寻址冲突的关键。

- 相关推荐

- 热点推荐

- 存储器

- MicroBlaze

-

基于MicroBlaze嵌入式高级应用及设计技巧2018-03-07 997

-

MicroBlaze串口设计2023-08-02 2579

-

MicroBlaze MCS和MicroBlaze的区别在哪?2023-08-23 2431

-

基于MicroBlaze 软核的FPGA 片上系统设计2009-04-15 718

-

基于MicroBlaze软核的FPGA片上系统设计2009-11-30 530

-

基于MicroBlaze的嵌入式系统设计2017-03-01 884

-

利用Vivado进行MicroBlaze处理器应用教程2017-11-17 19948

-

MicroBlaze性能详解2017-11-25 9109

-

Xilinx公司的MicroBlaze处理器的结构和原理是怎么样的?2018-09-05 1851

-

MicroBlaze的特点与功能概述2018-11-28 4396

-

ARTY Board与Xilinx MicroBlaze的配合使用演示2018-11-27 3163

-

MicroBlaze处理器参考指南2023-09-14 624

全部0条评论

快来发表一下你的评论吧 !