基于FPGA的并行硬件ECC模型的设计

FPGA/ASIC技术

描述

摘要:针对大容量固态存储器中数据错“位”的问题,目前大多采用软件ECC 模型进行检错和纠错,但这势必会极大地影响存储系统的读写性能。基于ECC 校验原理,提出一种并行硬件ECC 模型,并采用FPGA 实现。仿真分析和实验结果表明:该模型不仅具有良好的纠错能力,而且显著地提高了存储系统的读写性能。

由于NAND Flash 生产工艺的局限性,芯片在数据存储或传输过程中偶尔会发生“位”翻转现象,需要进行必要的检错和纠错。常用的数据检验方法有奇偶校验和CRC 校验等[1]。但NAND Flash 出错时一般不会造成整个块( block) 或是页( page) 全部出错,而是其中1 位或几位出错,故在NAND Flash处理中常采用专用的ECC( Error Checking and Correcting)校验。

传统的ECC 校验方法一般采用软件实现,这虽然复杂度低,易于实现工程应用,但由于每次读写NAND Flash 时都需要进行ECC 校验操作,大量的计算校验工作带来庞大的软件开销,直接导致存储系统的读写性能下降。

本文基于高速大容量固态存储器的硬件结构[2],结合NAND Flash 整页读写访问的特点[3],采用FPGA 逻辑进行了硬件方式的设计与实现,提出了一种并行硬件ECC 模型,将ECC 校验和数据读写同时并行实现,既保证了数据的可靠性,又显著地提高了存储系统的读写性能。

1 软件ECC 模型

ECC 校验[4,5]是在奇偶校验的基础上发展而来的,它将数据块看作一个矩阵,利用矩阵的行、列奇偶信息生成ECC 校验码。它能够检测并纠正1 位错误和检测2 位错误,克服了传统奇偶校验只能检出奇数位出错、校验码冗长及不能纠错的局限性。

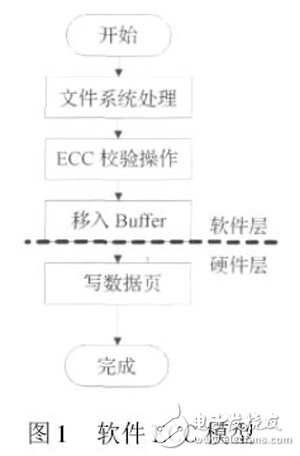

如图1 所示,传统软件ECC 模型的工作机理是:当应用程序需要写数据时,文件系统首先作相应的处理,然后根据待写的数据生成ECC 校验码,接着将数据和ECC 校验码移入数据缓冲区( 硬件Buffer) 中,最后向硬件控制器发起写命令,将数据写入NANDFlash 芯片。读操作的过程刚好逆向执行。

2 并行ECC 模型设计与实现

2. 1 并行ECC 模型设计思想

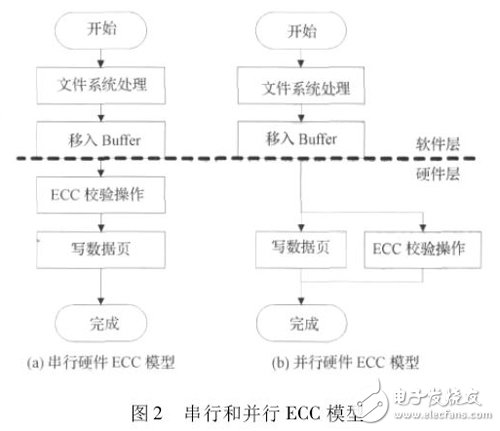

在软件ECC 模型中,首先ECC 校验操作带来庞大的软件开销,直接导致存储系统的读写性能下降。其次向NAND Flash 芯片写入或者读取数据都是以页为单位进行的。本文基于这两点原因,提出了并行硬件ECC 模型( 简称并行ECC 模型) ,如图2 ( b) 所示。一方面,ECC 校验改由硬件实现,减轻了软件开销; 另一方面,读写数据页和ECC 校验并行执行的巧妙设计提高了读写效率。

2. 2 并行ECC 模型实现

2. 2. 1 FPGA 逻辑结构

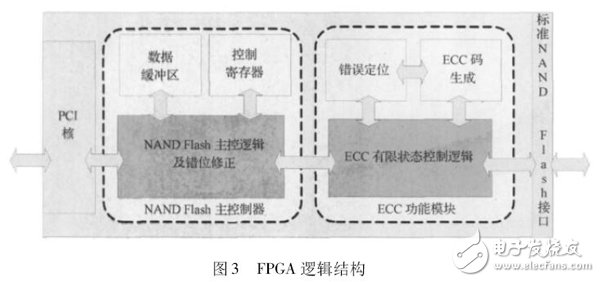

大容量固态存储器以FPGA 为控制核心,由多片NAND Flash 构成存储阵列,采用PCI 接口实现数据的高速传输。FPGA 作为大容量存储器的控制核心,主要有三大部分: PCI 核,NAND Flash 主控制器和ECC 功能模块,如图3 所示。采用Xilinx ISE 自带的PCI 核可以实现与CPU 端的通信和高速传输。NAND Flash 主控制器主要实现对NAND Flash 芯片的块擦除、页读取、页编程、ID 读取、状态查询和复位等命令的时序操作。ECC 功能模块完成ECC 码生成,错误检测,上报校验信息等工作。

FPGA 逻辑设计不仅要考虑NAND Flash 芯片对于块擦除、页读取、页编程等操作的时序要求和以页为单位进行读写访问的特点,还要保证ECC 功能模块能够正确地检错纠错。

2. 2. 2 ECC 功能模块

ECC 功能模块串接在NAND Flash 主控制器和NAND Flash 芯片之间,捕获读写信号和数据。通过

置位或复位相应的寄存器来使能和禁止ECC 校验功能,不需要工作时ECC 功能模块直接将收到的信号传给NAND Flash,需要工作时截取主控制器的控制信号,加上自己的操作后再传给NAND Flash。ECC 功能模块可以细分为ECC 有限状态控制逻辑、ECC 校验码生成模块和ECC 错误定位模块三部分。

ⅰ) 校验码生成模块

NAND Flash 在读写数据的时候是以页为单位进行的,结合ECC 校验算法,将每页前4 kB 大小的数据区分为8 组512 字节的数据块,每组对应3 个字节的奇偶校验码。根据送入的地址和数据,ECC校验码生成模块中8 个3 字节大小的寄存器将相应地更新奇偶校验值,最终生成ECC 校验码。

ⅱ) 错误定位模块

当NAND Flash 进行读操作时,读出的前4 kB数据将会被ECC 校验码生成模块重新计算ECC值。最后24 字节将会被错误定位模块移位存入ECC 存储值寄存器中,与ECC 校验码生成模块新生成的ECC 计算值进行比较,判断是否有数据位发生错误,并将错误类型和位置存入错误信息寄存器中。

ⅲ) 有限状态控制逻辑

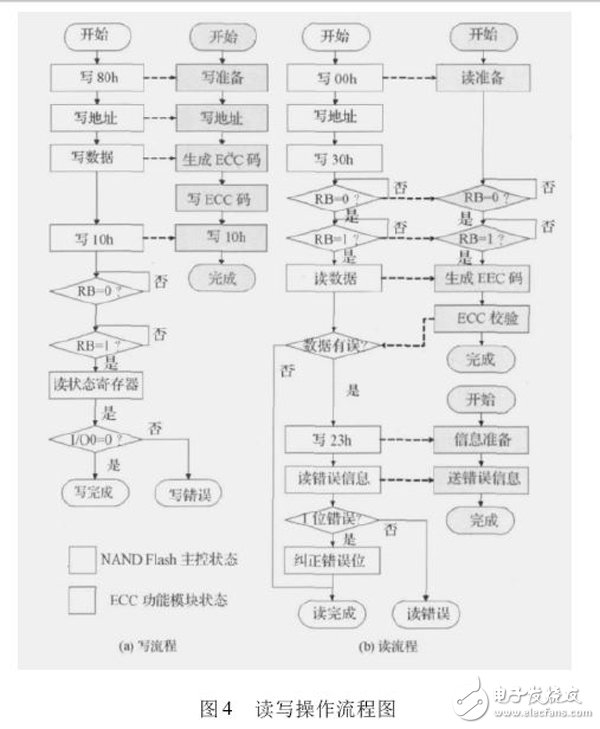

ECC 有限状态控制逻辑控制整个ECC 功能模块的工作时序,同时根据当前的状态信息输出状态信号。对于写操作,如图4 ( a) 所示,总线上传输前4 kB 数据时,ECC 功能模块捕获数据同时计算ECC校验码,当主控制器传完前4 200 字节后,ECC 功能模块接管数据总线,将其生成的ECC 校验码传入NAND Flash 中。对于读操作,与写操作类似,如图4( b) 所示,也以整页为单位进行。数据一边由NAND Flash 传入主控器的数据缓存区中,ECC 功能模块一边计算ECC 校验码。传完前4 200 字节后,与页尾24 字节ECC 存储值比较检错。如果有错,NAND Flash 主控制器就向ECC 功能模块发起查错周期,必要时根据错误信息进行纠错。ECC 功能模块只处理由NAND Flash 主控制器发起的读、写和查错三种命令,对于其他命令,则直接传给NAND Flash 芯片。

3 并行ECC 模型仿真验证与分析

3. 1 时序仿真与功能验证

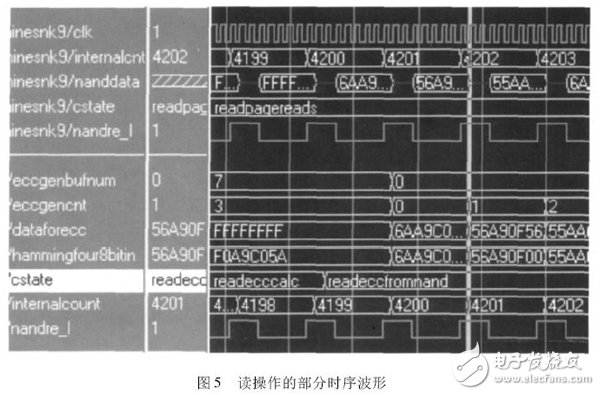

FPGA 逻辑设计阶段,要先通过仿真来分析时序是否满足芯片要求,ECC 校验功能是否运行正确。在ModelSim 中调用NAND Flash 主控制器模块和ECC 功能模块并将其实例化,产生时钟和复位信号以及读写请求,形成仿真波形,对ECC 功能进行验证。图5 为并行ECC 模型读操作的部分时序波形,传完前4 200 字节后,错误定位模块正在进行比较检错。

FPGA 逻辑设计完成之后,要通过测试程序来验证功能:

①读写数据时FPGA 逻辑能否正确生成ECC 校验码;

②遇到数据有误时,能否正确地检错和纠错。

3. 2 性能测试与分析

由于并行硬件ECC 模型既要考虑ECC 校验,又要满足NAND Flash 读写时序,开发难度较大,本文在前期先实现了串行硬件ECC 模型( 如图2 ( a)所示) ,经充分验证之后,复用相关模块,进而实现了并行硬件ECC 模型。

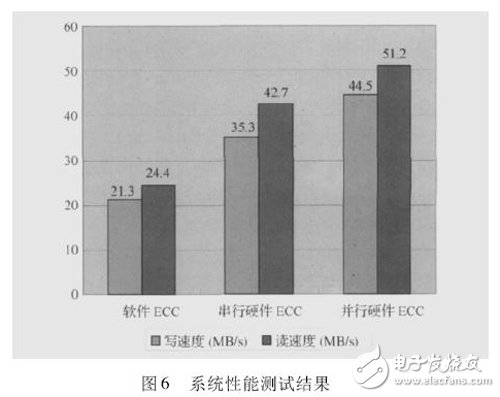

为验证本文模型的可行性,本文分别对软件ECC 模型、串行硬件ECC 模型和并行硬件ECC 模型做系统性能测试。

硬件平台: 以FPGA 为控制核心的大容量固态存储器。

软件环境: VxWorks 5. 5 操作系统、Datalight 公司的FlashFX Pro 3. 3 设备管理驱动和Reliance 3. 2文件系统。

测试方法: 在上述3 种模型对应的系统中分别创建一个文件,写入1 GB 大小的特定数据,测试各模型的读写速率。

如图6 所示,测试结果表明: 在保证数据可靠性的前提下,并行硬件ECC 模型的读写性能均要明显优于其它二者,且较之软件ECC 模型,并行硬件ECC 模型读/写速率均提高到2 倍多,极大地改善了系统的读写性能。

4 总结

本文首先通过分析传统ECC 数据校验方法,结合NAND Flash 整页读写特性,提出了一种并行硬件ECC 模型。该模型具有每512 字节能够检测并纠正1 位错误和检测出2 位错误的校验能力,可以有效地保证大容量固态存储器在其生命周期内数据的可靠性和安全性。进而,针对NAND Flash 芯片对于块擦除、页读取、页编程及复位等操作的时序要求和以页为单位进行读写访问的特点,采用FPGA 逻辑实现了并行硬件ECC 模型。最后通过时序仿真、功能验证和性能测试,证明了该模型的有效性和可行性。

-

如何使用FPGA驱动并行ADC和并行DAC芯片?2024-02-22 6193

-

并行编程模型有什么优势2019-07-11 3728

-

怎么实现以FPGA为核心器件的并行多通道信号产生模块?2021-04-29 1631

-

并行可配置ECC专用指令协处理器2009-03-20 766

-

基于FPGA的NAND Flash ECC校验2011-07-17 7318

-

城域传输网ECC配置规范2011-08-02 919

-

基于FPGA的ECC快速算法研究及设计2017-01-07 758

-

基于FPGA的ARM并行总线研究与仿真2017-01-24 1086

-

一种基于门限ECC的PKI_CA模型的设计_毛颖慧2017-03-19 692

-

FPGA电源设计在并行工程中的应用2017-10-13 942

-

基于FPGA帧ECC逻辑端口描述应用2017-11-15 2647

-

如何使用FPGA实现全并行结构FFT2021-03-31 1526

-

如何使用FPGA驱动并行ADC和并行DAC芯片2022-04-21 8565

-

基于FPGA的ARM并行总线设计原理2023-10-10 445

-

FPGA加速深度学习模型的案例2024-10-25 2215

全部0条评论

快来发表一下你的评论吧 !